4位数码管动态扫描Verilog程序

- 格式:docx

- 大小:13.36 KB

- 文档页数:2

简单4位数字频率计设计一、 设计要求(1)、利用Verilog HDL 语言行为描述方法,设计一个简单的4位数字频率计; (2)、要求输入标准时钟信号频率为1MHz ,系统可计数频率范围为1Hz~9999Hz ; (3)、系统具有复位信号,且当计数频率发生溢出时能够给出指示信号,计数的频率通过4个共阴数码管进行显示(动态扫描显示)。

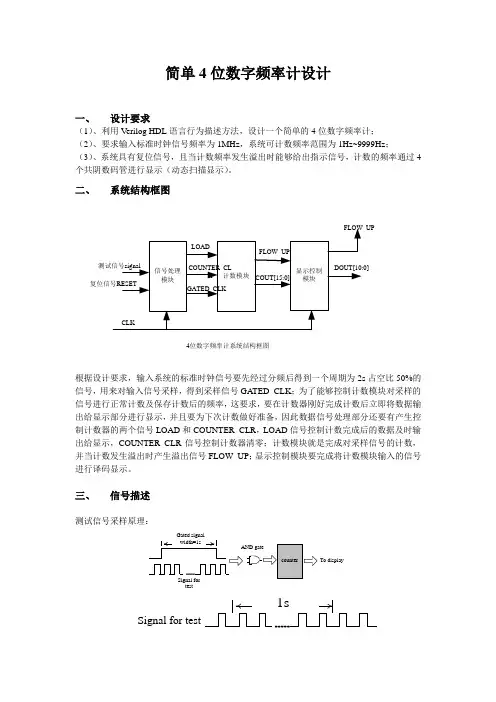

二、 系统结构框图4位数字频率计系统结构框图根据设计要求,输入系统的标准时钟信号要先经过分频后得到一个周期为2s 占空比50%的信号,用来对输入信号采样,得到采样信号GA TED_CLK ;为了能够控制计数模块对采样的信号进行正常计数及保存计数后的频率,这要求,要在计数器刚好完成计数后立即将数据输出给显示部分进行显示,并且要为下次计数做好准备,因此数据信号处理部分还要有产生控制计数器的两个信号LOAD 和COUNTER_CLR ,LOAD 信号控制计数完成后的数据及时输出给显示,COUNTER_CLR 信号控制计数器清零;计数模块就是完成对采样信号的计数,并当计数发生溢出时产生溢出信号FLOW_UP ;显示控制模块要完成将计数模块输入的信号进行译码显示。

三、 信号描述测试信号采样原理:Signal for testTo displaySignal for testGA TED_CLK 、LOAD 、COUNTER_CLR 信号的关系:COUNTER_CLRGATED_CLKLOAD四、 Verilog 程序各子模块verilog 程序:(1)信号处理模块_verilog : moduleFREQUENCY_COUNTROL_BLOCK(GATED_CLK,LOAD,COUNTER_CLR,CLK_IN,SIGNA L_TEST,RESET); output GATED_CLK; output LOAD; output COUNTER_CLR; input CLK_IN; input SIGNAL_TEST; input RESET; reg LOAD; reg COUNTER_CLR; reg DIVIDE_CLK; reg[19:0] cn; reg A1,A2;//信号分频:由CLK_IN 得到分频后的信号DIVIDE_CLK(0.5Hz) always @(posedge CLK_IN) begin if(RESET) begin DIVIDE_CLK<=0; cn<=0;endelse if(cn==1000000)begincn<=0;DIVIDE_CLK<=~DIVIDE_CLK;endelsecn<=cn+1;end//频率计数控制信号的产生:产生LOAD信号和COUNTER_CLR信号always @(posedge SIGNAL_TEST)beginA1<=~DIVIDE_CLK;endalways @(posedge SIGNAL_TEST)beginA2=A1;endalways @(A1 or A2)beginLOAD=A1&&(!A2);endalways @(posedge SIGNAL_TEST)COUNTER_CLR=LOAD;//产生驱动计数模块的信号GATED_CLK,也就是被计数模块检测的信号assign GATED_CLK=SIGNAL_TEST&DIVIDE_CLK;endmodule(2)、计数器模块:moduleFREQUENCY_COUNTER_BLOCK(COUT,FLOW_UP,CLOCK_IN,RESET,LOAD,COUNTER _CLR);output[15:0] COUT;output FLOW_UP;input CLOCK_IN;input LOAD;input COUNTER_CLR;input RESET;reg[15:0] TEMP;reg FLOW_UP;parameter B_SIZE=16; //二进制位宽,为便于移植,所有定义了成参数reg[B_SIZE+3:0] bcd; //转换后的BCD码的位数要比二进制多4位reg[B_SIZE-1:0] binary;reg[B_SIZE-1:0] bin;reg[B_SIZE+3:0] result;//计数器完成计数得到二进制表示的频率数值always @(CLOCK_IN or RESET or LOAD or COUNTER_CLR)beginif(RESET|COUNTER_CLR)beginTEMP<=0;FLOW_UP<=0;endelse if(LOAD)binary<=TEMP;else if(TEMP>9999)beginFLOW_UP<=1;binary<=9999;endelseif(CLOCK_IN)TEMP<=TEMP+1;end//将二进制表示(或十六进制表示)的数转换为BCD码的形式,便于数码管译码显示always @(binary or RESET)beginbin=binary;result=0;if(RESET)bcd<=0;elsebeginrepeat(B_SIZE-1)beginresult[0]=bin[B_SIZE-1];if(result[3:0]>4)result[3:0]=result[3:0]+4'd3;if(result[7:4]>4)result[7:4]=result[7:4]+4'd3;if(result[11:8]>4)result[11:8]=result[11:8]+4'd3;if(result[15:12]>4)result[15:12]=result[15:12]+4'd3;if(result[19:16]>4)result[19:16]=result[19:16]+4'd3;result=result<<1;bin=bin<<1;endresult[0]=bin[B_SIZE-1];bcd<=result;endendassign COUT=bcd[15:0];endmodule(3)信号显示处理:module FREQUENCY_DISPL Y_BLOCK(DOUT,DCLK_IN,RESET,CDIN);output[10:0] DOUT;input[15:0] CDIN;input DCLK_IN;input RESET;reg[10:0] DOUT;reg[3:0] Temp1;reg[1:0] cn;always @(posedge DCLK_IN) //设置成动态扫描beginif(RESET)cn<=0;elsebegincn<=cn+1;case(cn)2'b00: begin DOUT[10:7]<=4'b0001; Temp1<=CDIN[3:0];end2'b01: begin DOUT[10:7]<=4'b0010; Temp1<=CDIN[7:4];end2'b10: begin DOUT[10:7]<=4'b0100; Temp1<=CDIN[11:8];end2'b11: begin DOUT[10:7]<=4'b1000; Temp1<=CDIN[15:12];endendcaseendendalways @(Temp1) //译码显示begincase(Temp1)4'b0000: DOUT[6:0]<=7'b0111111; //3fh=04'b0001: DOUT[6:0]<=7'b0000110; //06h=14'b0010: DOUT[6:0]<=7'b1010110; //56h=24'b0011: DOUT[6:0]<=7'b1001111; //4fh=34'b0100: DOUT[6:0]<=7'b1100110; //66h=44'b0101: DOUT[6:0]<=7'b1101101; //6dh=54'b0110: DOUT[6:0]<=7'b1111101; //7dh=64'b0111: DOUT[6:0]<=7'b0000111; //07h=74'b1000: DOUT[6:0]<=7'b1111111; //7fh=84'b1001: DOUT[6:0]<=7'b1101111; //6fh=9default: DOUT[6:0]<=7'b0111111; //3fhendcaseendendmodule顶层verilog程序:moduleFREQUENCY_COUNTER_DISPL Y_BLOCK(DOUT,FLOW_UP,CLK,TEST_CLK_IN,RESET) ;output[10:0] DOUT;output FLOW_UP;input CLK;input TEST_CLK_IN;input RESET;wire gated_clk,load,counter_clr;wire[15:0] cout_cdin;FREQUENCY_COUNTROL_BLOCKu1(.GATED_CLK(gated_clk),.LOAD(load),.COUNTER_CLR(counter_clr),.CLK_IN(CLK),.SIG NAL_TEST(TEST_CLK_IN),.RESET(RESET));FREQUENCY_COUNTER_BLOCKu2(.COUT(cout_cdin),.FLOW_UP(FLOW_UP),.CLOCK_IN(gated_clk),.RESET(RESET),.LOA D(load),.COUNTER_CLR(counter_clr));FREQUENCY_DISPL Y_BLOCKu3(.DOUT(DOUT),.DCLK_IN(CLK),.RESET(RESET),.CDIN(cout_cdin));endmodule五、仿真结果分析仿真结果如图所示,输入标准时钟频率为1MHz,经过分频后变成频率为0.5Hz的信号,将其与测试信号相与得到采样信号GATED_CLK,同时利用测试信号和0.5Hz的分频信号可以产生LOAD信号和COUNTER_CLR信号,它们和采样信号的关系在图上可以清楚的看出。

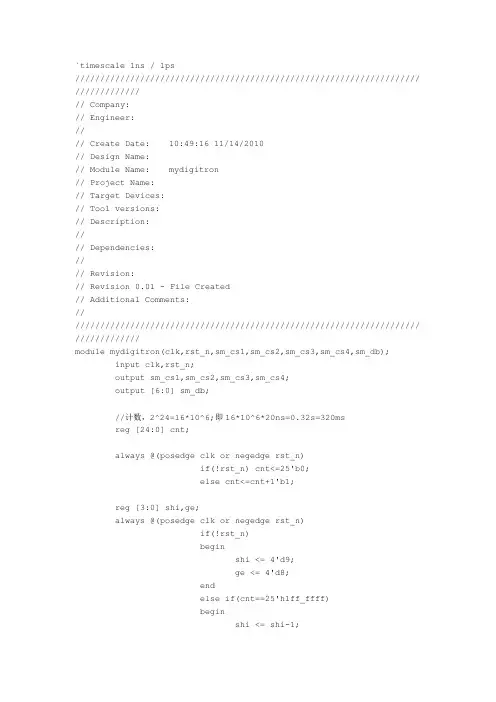

`timescale 1ns / 1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 10:49:16 11/14/2010// Design Name:// Module Name: mydigitron// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module mydigitron(clk,rst_n,sm_cs1,sm_cs2,sm_cs3,sm_cs4,sm_db);input clk,rst_n;output sm_cs1,sm_cs2,sm_cs3,sm_cs4;output [6:0] sm_db;//计数,2^24=16*10^6;即16*10^6*20ns=0.32s=320msreg [24:0] cnt;always @(posedge clk or negedge rst_n)if(!rst_n) cnt<=25'b0;else cnt<=cnt+1'b1;reg [3:0] shi,ge;always @(posedge clk or negedge rst_n)if(!rst_n)beginshi <= 4'd9;ge <= 4'd8;endelse if(cnt==25'h1ff_ffff)beginshi <= shi-1;ge <= ge-1; endparameterseg0 = 7'hc0,seg1 = 7'hf9,seg2 = 7'ha4,seg3 = 7'hb0,seg4 = 7'h99,seg5 = 7'h92,seg6 = 7'h82,seg7 = 7'hf8,seg8 = 7'h80,seg9 =7'h90,sega =7'h88,segb =7'h83,segc =7'hc6,segd =7'ha1,sege =7'h86,segf =7'h8e;//segf =7'hff;reg [3:0] num;reg [6:0] sm_dbr;always @(num)case(num)4'h0:sm_dbr<=seg0; 4'h1:sm_dbr<=seg1; 4'h2:sm_dbr<=seg2; 4'h3:sm_dbr<=seg3; 4'h4:sm_dbr<=seg4; 4'h5:sm_dbr<=seg5; 4'h6:sm_dbr<=seg6; 4'h7:sm_dbr<=seg7; 4'h8:sm_dbr<=seg8; 4'h9:sm_dbr<=seg9; 4'hA:sm_dbr<=sega; 4'hB:sm_dbr<=segb; 4'hC:sm_dbr<=segc; 4'hD:sm_dbr<=segd; 4'hE:sm_dbr<=sege; 4'hF:sm_dbr<=segf; default:;endcaseassign sm_db = sm_dbr;reg sm_cs2_r,sm_cs1_r;always @(clk or shi or ge)beginif(cnt[20])beginsm_cs2_r = 0;sm_cs1_r = 1;num = shi;endelsebeginsm_cs2_r = 1;sm_cs1_r = 0; num = ge;endendassign sm_cs4 = 1;assign sm_cs3 = 1;assign sm_cs2 = sm_cs2_r;assign sm_cs1 = sm_cs1_r;endmoduleImplementation Constrants FlieNET "clk" LOC = P54;NET "rst_n" LOC = P38;NET "sm_cs1" LOC = P34;NET "sm_cs2" LOC = P33;NET "sm_cs3" LOC = P32;NET "sm_cs4" LOC = P26;NET "sm_db<0>" LOC = P25;NET "sm_db<1>" LOC = P16;NET "sm_db<2>" LOC = P23;NET "sm_db<3>" LOC = P21;NET "sm_db<4>" LOC = P20;NET "sm_db<5>" LOC = P17;NET "sm_db<6>" LOC = P83;。

1.利用动态扫描方法在六位数码管上显示出稳定的87654321.#include<reg52.h>#define uint unsigned int#define uchar unsigned charuchar code tabledu[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x7 1};uchar code tablewe[]={0x7f,0xbf,0xdf,0xef,0xf7,0xfb,0xfd,0xfe};uint numdu,numwe,a;/*用uint 或int时只能65536-(1000~5000),用uchar和char则不会*/ void main(){numdu=8;numwe=0;a=0;EA=1;ET1=1;TR1=1;TMOD=0x10;TH1=(65536-1000)/256;TL1=(65536-1000)%256;while(1){ if(a==1){a=0;P0=tabledu[numdu];numdu--;if(numdu==0)numdu=8;P2=tablewe[numwe];numwe++;if(numwe==8)numwe=0;}}}void time1() interrupt 3{TH1=(65536-1000)/256;TL1=(65536-1000)%256;a++;}2.用动态扫描方法和定时器0在数码管的前三位显示出秒表,精确到1%秒,即后两位显示1%秒,一直循环下去。

#include<reg52.h>#define uint unsigned int#define uchar unsigned charuint temp,aa=0,bai,shi,ge; /*不能用uchar或char,可用uint或int*/uchar code table[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};void display(uchar bai,uchar shi,uchar ge);void delay(uint z);void init();void main(){init();//初始化子程序while(1){display(bai,shi,ge);}}void delay(uint z){uint x,y;for(x=z;x>0;x--)for(y=110;y>0;y--);}void display(uchar bai,uchar shi,uchar ge){P2=0x7f;P0=table[bai]+0x80;delay(5);P2=0xbf;P0=table[shi];delay(5);P2=0xdf;P0=table[ge];delay(5);}void init(){temp=0;TMOD=0x01;TH0=(65536-10000)/256;TL0=(65536-10000)%256;EA=1;ET0=1;TR0=1;}void timer0() interrupt 1{TH0=(65536-10000)/256;TL0=(65536-10000)%256;aa++;if(aa==1) /*放主函数中达不到此效果*/{aa=0;temp++;if(temp==1000){temp=0;}bai=temp/100;shi=temp%100/10;ge=temp%10;}}3、利用动态扫描和定时器1在数码管上显示出从765432开始以1/10秒的速度往下递减直至765398并保持显示此数,与此同时利用定时器0以500MS速度进行流水灯从上至下移动,当数码管上数减到停止时,实验板上流水灯也停止然后全部开始闪烁,3秒后(用T0定时)流水灯全部关闭、数码管上显示出“HELLO”。

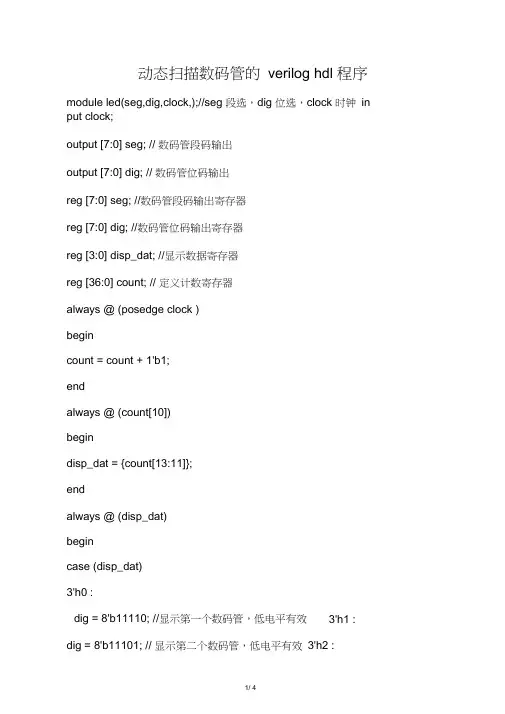

动态扫描数码管的verilog hdl 程序module led(seg,dig,clock,);//seg 段选,dig 位选,clock 时钟in put clock;output [7:0] seg; // 数码管段码输出output [7:0] dig; // 数码管位码输出reg [7:0] seg; //数码管段码输出寄存器reg [7:0] dig; //数码管位码输出寄存器reg [3:0] disp_dat; //显示数据寄存器reg [36:0] count; // 定义计数寄存器always @ (posedge clock )begincount = count + 1'b1;endalways @ (count[10])begindisp_dat = {count[13:11]};endalways @ (disp_dat)begincase (disp_dat)3'h0 :dig = 8'b11110; //显示第一个数码管,低电平有效3'h1 : dig = 8'b11101; // 显示第二个数码管,低电平有效3'h2 :dig = 8'b111011; // 显示第三个数码管,低电平有效 3'h3 : 3'h4 : dig= 8'b110111; // 显示第四个数码管,低电平有效 dig= 8'b111011; // 显示第五个数码管,低电平有效 3'h5 : dig= 8'b110111; // 显示第六个数码管,低电平有效 3'h6 : dig= 8'b10111; // 显示第七个数码管,低电平有效 3'h7 : dig= 8'b01111; // 显示第八个数码管,低电平有效 endcaseendalways @ (disp_dat) begin case (disp_dat)4'h0 :seg = 8'hc0; //显示 "0" 4'h1 :seg = 8'hf9; //显示 "1" 4'h2 :seg = 8'ha4; //显示 "2" 4'h3 :seg = 8'hb0; //显示 "3" 4'h4 :seg = 8'h99; //显示 "4" 4'h5 :seg = 8'h92; //显示 "5"4'h6 :seg = 8'h82; //显示"6" 4'h7 :seg = 8'hf8; //显示"7" 4'h8 :seg = 8'h80; //显示"8" 4'h9 :seg = 8'h90; //显示"9" 4'ha :seg = 8'h88; //显示"a" 4'hb :seg = 8'h83; //显示"b" 4'hc :seg = 8'hc6; //显示"c" 4'hd :seg = 8'ha1; //显示"d" 4'he :seg = 8'h86; //显示"e" 4'hf :seg = 8'h8e; //显示"f" endcase end endmodule。

1、简单4位计数器程序:module count4(clk,cnt);input clk;output reg[3:0]cnt=4'b0;always @(posedge clk)begincnt<=cnt+1;endendmodule测试程序:`timescale 1 ns/10 psmodule test_count4();reg clk=0;wire [3:0]cnt;count4 i1(.clk(clk),.cnt(cnt));always #10 clk=~clk;initialbegin$monitor($time,,,"clk=%d cnt=%d",clk,cnt); #400 $stop;endendmodule仿真波形:2、异步清零4位计数器源程序module count4_reset(clk,rst,cnt);input clk,rst;output reg[3:0]cnt=4'b0;always @(posedge clk or negedge rst)beginif(!rst) cnt<=4'b0;else cnt<=cnt+1;endendmodule测试程序`timescale 1 ns/10 psmodule test_count4_reset();reg clk=0;reg rst;wire [3:0]cnt;count4_reset i1(.clk(clk),.rst(rst),.cnt(cnt));always #10 clk=~clk;initialbeginrst=0;#20 rst=1;#45 rst=0;#10 rst=1;endinitialbegin$monitor($time,,,"clk=%d rst=%d cnt=%d",clk,rst,cnt);#800 $stop;endendmodule仿真波形3、异步清零、计数使能控制的4位计数器module count4_rst_en(clk,rst,en,cnt);input clk,rst,en;output [3:0]cnt;reg [3:0]cnt;always @(posedge clk or negedge rst)beginif(!rst) cnt<=0;else if(en==1) cnt<=cnt+1;endendmodule测试程序`timescale 1 ns/10 psmodule test_count4_rst_en();reg clk=0;reg rst,en;wire [3:0]cnt;count4_rst_en i1(.clk(clk),.rst(rst),.en(en),.cnt(cnt));always #10 clk=~clk;initialbeginrst=0;en=0;#15 en=1;#20 rst=1;#20 en=0;#20 en=1;rst=0;#20 rst=1;endinitialbegin$monitor($time,,,"clk=%d rst=%d en=%d cnt=%d",clk,rst,en,cnt);#800 $stop;endendmodule仿真波形:4、异步清零、计数使能、数据加载控制功能的4位计数器:module count4_rst_en_load(clk,rst,en,load,data,cnt);input clk,rst,en,load;input [3:0]data;output reg[3:0]cnt;always @(posedge clk or negedge rst)beginif(!rst) cnt<=0;else if(en==1)beginif(load) cnt<=data;else cnt<=cnt+1;endendendmodule测试程序:`timescale 1 ns/10 psmodule test_count4_rst_en_load();reg clk=0;reg rst,en,load;reg [3:0]data;wire [3:0]cnt;count4_rst_en_load i1(.clk(clk),.rst(rst),.en(en),.load(load),.data(data),.cnt(cnt));always #10 clk=~clk;initialbeginrst=0;en=0;load=0;data=4'd6;#20 en=1;#20 rst=1;#20 load=1;#20 rst=0;#20 rst=1;#20 load=0;endinitialbegin$monitor($time,,,"clk=%d rst=%d en=%d load=%d cnt=%d",clk,rst,en,load,data,cnt);#800 $stop;endendmodule仿真波形:。

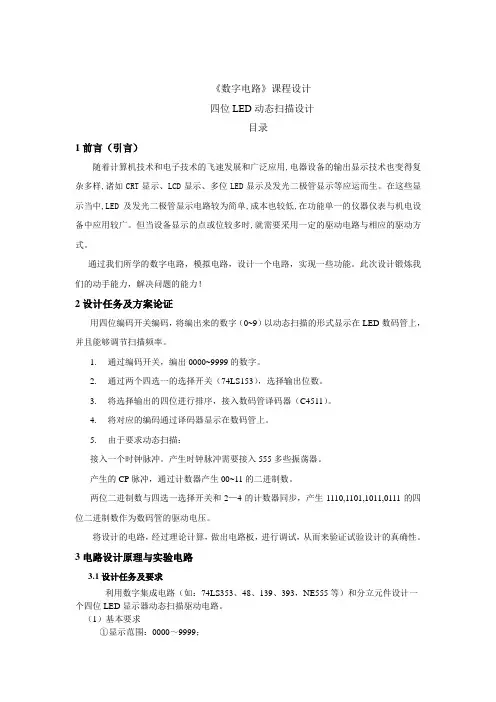

《数字电路》课程设计四位LED动态扫描设计目录1前言(引言)随着计算机技术和电子技术的飞速发展和广泛应用,电器设备的输出显示技术也变得复杂多样,诸如CRT显示、LCD显示、多位LED显示及发光二极管显示等应运而生。

在这些显示当中,LED及发光二极管显示电路较为简单,成本也较低,在功能单一的仪器仪表与机电设备中应用较广。

但当设备显示的点或位较多时,就需要采用一定的驱动电路与相应的驱动方式。

通过我们所学的数字电路,模拟电路,设计一个电路,实现一些功能。

此次设计锻炼我们的动手能力,解决问题的能力!2设计任务及方案论证用四位编码开关编码,将编出来的数字(0~9)以动态扫描的形式显示在LED数码管上,并且能够调节扫描频率。

1.通过编码开关,编出0000~9999的数字。

2.通过两个四选一的选择开关(74LS153),选择输出位数。

3.将选择输出的四位进行排序,接入数码管译码器(C4511)。

4.将对应的编码通过译码器显示在数码管上。

5.由于要求动态扫描:接入一个时钟脉冲。

产生时钟脉冲需要接入555多些振荡器。

产生的CP脉冲,通过计数器产生00~11的二进制数。

两位二进制数与四选一选择开关和2—4的计数器同步,产生1110,1101,1011,0111的四位二进制数作为数码管的驱动电压。

将设计的电路,经过理论计算,做出电路板,进行调试,从而来验证试验设计的真确性。

3电路设计原理与实验电路3.1设计任务及要求利用数字集成电路(如:74LS353、48、139、393,NE555等)和分立元件设计一个四位LED显示器动态扫描驱动电路。

(1)基本要求①显示范围:0000~9999;②显示方式:LED显示;③扫描频率:1Hz~1000Hz连续可调;④可预置数:0000~9999。

(2)发挥部分①扫描频率:1Hz~1000Hz连续可调;②自制符合要求电源。

3.2 设计方案通过编码开关对0到9的数字进行编码,送入四选一的选择器(74LS153),通过由低位到高位的排序,将选择的数字传入到译码器(74HC4511)中,并通过输出中间级使其数据传送到LED七段数码显示管。

FPGA入门(一)---四位共阴数码管显示--2007。

4。

412--采用4X4键盘进行控制,并显示相应的数字。

3--选自AVR和CPLD的书4--串行联接的七段数码管驱动程序,用了4个数码管5--四位数码管动态显示。

6--高电平选通位选端。

共阴数码管78library i eee;9use i eee.std_logic_1164.all;10use i eee.std_logic_unsigned.all;11entity l ed_7com is12port(clock:in s td_logic;13key_num:IN integer range 0 to 9;14en:out s td_logic_vector(0 to 3);--分别接4个数码管的公共端15display:out s td_logic_vector(0 to 7 ));--接数码管的7 隹刂贫? abcdefgend;1617architecture light of l ed_7com issignal c ounter:integer range 0 to 3;1819begin20process(clock)21variable n um:integer range 0 to 9;22begin23--if rising_edge(clock) thenif c lock'event and c lock='1' then2425if c ounter =3 then26counter<=0;27else28counter<=counter+1;29end if;case counter is3031when 0 =>32en<="1000"; --点亮第一个数码管,屏蔽其它5个数码管33num:=key_num; --显示第一个数34when 1=>en<="0100";3536num:=key_num;37when 2=>38en<="0010";39num:=key_num;40when 3=>en<="0001";4142num:=key_num;43when others=>null;end case;44Page 1 of 2Revision: led_7comcase num is4546when 0=> display <="11111101";--0abcdefg段47when 1=> display <="01100000";--148when 2=> display <="11011011";49when 3=> display <="11110010";50when 4=> display <="01100111";51when 5=> display <="10110110";52when 6=> display <="00111111";53when 7=> display <="11100000";54when 8=> display <="11111111";55when 9=> display <="11100110";56when others => display <="00000000";57end case ;58end if ;59end process;60end ;6162Page 2 of 2Revision: led_7com。

/*-----------------------------------------------------方案要求:上电一个LED一直闪,四位数码管9999循环正计数思路:用两个定时器分别控制LED和数码管----------------------------------------------------------*/#include <reg51.h>//51头文件#define Uchar unsigned char//宏定义,用Uchar来代表关键词unsigned char(无符号字符型数据)#define Uint unsigned int//宏定义,用Uchar来代表关键词unsigned int(无符号整型数据)sbit seg = P2^6; //位声明,声明该位用于控制数码管的笔画.sbit com = P2^7;//位声明,声明该位用于控制数码管的公共端.sbit LED = P1^0;//位声明,声明该位用于控制一个LED亮灭.Uchar displ[]= //声明数组,displ是自定义数组名,[]是叫下标的,里面本应填元素个数,但可以不填.{0x3f,0x06,0x5b,0x4f, //这些都是叫数组的元素,按顺序排放,从左到右,从上到下.0x66,0x6d,0x7d,0x07,0x7f,0x6f,//这是共阴数码管,ox7f=01111111 ,如果该数(8字)是10000000则是共阳.};Uint number, number1, number2, qian, bai, shi, ge; //定义多个全局变量,以便后面要用到void delay_mS (Uint k)//延时子程序,k为形参,在显示子程序里会传递实参来进行计算{Uint i,j;//定义两个局部变量for(i=k; i>0; i--)//k接到实参后,如果i大于0,那么让i自减1,再执行{ }内的for语句,然后再判断i是否大于0,{for(j=110; j>0; j--);}//直到i=0(不大于0),该延时子程序才算执行完成,跳出。

4位数码动态显示电路(VHDL)---4位数码管动态显示电路Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;----输入数据采用8421BCD编码方式----输入刷新频率要求100hz以上----输出代码为串行输出ENTITY scanseg4 ISPORT( CLKIN: in std_logic;date : in std_logic_vector(15 downto 0);---4位待显示的数据point: in std_logic_vector(3 downto 0);----小数点控制信号sdateout:out std_logic;-----串行输出显示码clkout :out std_logic;-----串行输出时钟segweixh:out std_logic_vector(3 downto 0);-----数码管位选控制信号,低电平有效);END scanseg4;Architecture beh of scanseg4 ISsignal datebuf:std_logic_vector(3 downto 0);----显示数据缓存寄存器signal datein :std_logic_vector(15 downto 0);signal cnt :std_logic_vector(1 downto 0);------动态扫描计数器signal segma :std_logic_vector(6 downto 0);-----数码管段码输出,采用共阴数码管编码方式signal pointout: std_logic------小数点控制输出signal cnt8 :std_logic_vector(3 downto 0);------串行码输出个数计数器signal clkweix:std_logic:='0';------字动态扫描计数器输入时钟信号,为串出计数到信号signal temp :std_logic_vector(7 downto 0);---数码管8位编码寄存器begindatein<=date;------读取要显示的数据clkout<=clkin;-----显示模块的输入时钟与串行驱动电路的时钟同步temp <=segma&point;process(clkin) --------串行输出计数器模块,产生扫描时钟beginif clkin'event and clkin='1' thencnt8<=cnt8+"01";end if;if cnt8="111"thenclkweix<='1';elseclkweix<='0';end process;process(clkweix) --------数码管扫描计数器模块beginif clkweix'event and clkweix='1' thencnt<=cnt+"01";end if;end process;process(clkweix)-----驱动模块beginif clkweix'event and clkweix='1' thencase cnt iswhen"00" =>datebuf<= datein(3 downto 0);pointout<= point(0);segweixh<= "1110";when"01" =>datebuf<= datein(7 downto 4);pointout<= point(1);segweixh<= "1101";when"10" =>datebuf<= datein(11 downto 8); pointout<= point(2);segweixh<= "1011";when"11" =>datebuf<= datein(15 downto 12); pointout<= point(3);segweixh<= "0111";when others =>datebuf<= datein(3 downto 0);pointout<= point(0);segweixh<= "1111";end case;end if;end process;process(datebuf)-----译码模块begincase datebuf iswhen"0000" =>segma<= "1111110";---显示0when"0001" =>segma<= "0000110";---显示1when"0010" =>segma<= "1101101";---显示2when"0011" =>segma<= "1111001";---显示3when"0100" =>segma<= "0110011";---显示4when"0101" =>segma<= "1011011";---显示5when"0110" =>segma<= "1011111";---显示6when"0111" =>segma<= "1110000";---显示7when"1000" =>segma<= "1111111";---显示8when"1001" =>segma<= "1111011";---显示9when others =>segma<= "1111111";end case;end process;process(clkin)---单个字并并转串beginif clkin'event and clkin='1' thentemp<=temp(6 downto 0)& pointout;-----实现左移操作 sdateout<=temp(7);end if;end process;end beh;。

时代农机TIMES AGRICULTURAL MACHINERY第46卷第2期Vol.46No.22019年2月Feb.20192019年第2期摘要:应用仿真软件,设计“2018”动态显示程序并进行计算机仿真。

关键词:程序;动态显示;单片机控制作者简介:谭明良(1998-),男,辽宁大连人,大学本科,主要研究方向:机电一体化技术。

通讯作者:王伟(1957-),男,山东菜州人,硕士,副教授,主要研究方向:机电一体化技术、机床电气与PLC 技术。

单片机控制的四位数码管动态显示编程谭明良,王伟(沈阳工学院,辽宁抚顺113122)1软件介绍与动态说明PROTEUS 软件是英国Lab Center Electronics公司出版的EDA (电子设计自动化)工具软件。

KeilC51是美国Keil Software 公司出品的51系列兼容单片机C 语言软件开发系统。

两软件的联合调试是单片机仿真的基础。

静态显示就是用单片机I/O 口输出固定的数值,每个数码管的驱动电平不会改变,一般用来显示固定的数值。

动态显示,也称扫描显示,是将所有数码管的8段即a~dp 段都连接在一起,分时使各个数码管的位选端有效,也就是在某一个时刻只能有1个数码管在显示。

由于人眼具有“视觉暂留”作用(通常在20ms 左右),因此只要使多个数码管显示的时间间隔较短,人眼一般是感绝不到数码管熄灭的,因此可以形成多个数码管在“静态显示”的假象。

动态显示优点是占用的I/O 接口较少,但需要消耗一定的时间。

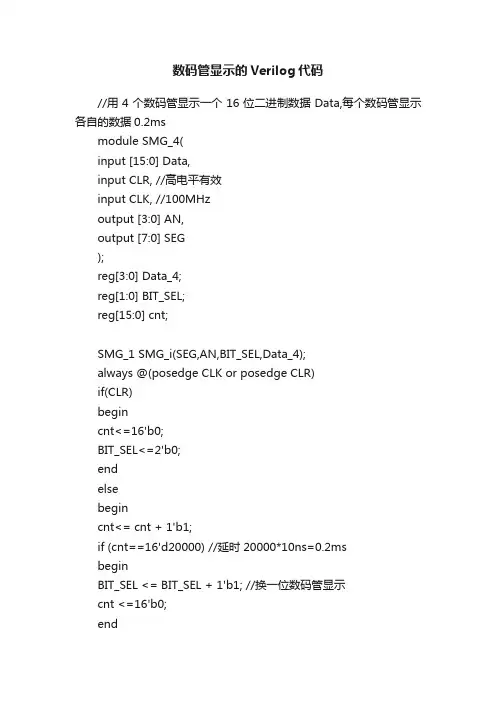

2动态显示编程由四位数码管用动态显示“2018”,原理是由单片机的一个I/O 口输出显示段码,另一个I/O 口输出位码。

程序如下:#include<reg52.h>delay ();#define uchar unsigned char P2=0x00;#define uint unsigned intP2=a [2];uchar code a [4]={0x7f ,0x06,0x3f ,0x5b};P1=b [2];uchar code b [4]={0xfe ,0xfd ,0xfb ,0xf7};delay ();uint time ;P2=0x00;void delay ();P2=a [3];void main ()P1=b [3];{P0=0x00;delay ();while (1)P2=0x00;{P2=a [0];}P1=b [0];}delay ();void delay ()P2=0x00;{time=1300;P2=a [1];while (time--);}P1=b [1];3仿真效果4结语动态显示可以同时显示多位数码管,通过不停的刷新I/O 口的数据来实现多位的持续显示。

FPGA—4位十进制频率计4位十进制频率计一、设计目的用Verilog HDL语言设计一个能实现自动测频的4位十进制频率计。

1)测量范围: 1Hz~9999Hz2)测量的数值通过4个数码管显示3)频率超过9999Hz时,溢出指示灯亮,可以作为扩大测量范围的接口。

二、设计原理1、若某一信号在T秒时间里重复变化了N 次,则根据频率的定义可知该信号的频率fs 为:fs=N/T。

2、当T=1s时,N就是测得的频率。

3、根据以上所提出的方法,测定信号的频率必须有一个脉宽为1秒的对输入信号脉冲计数允许的信号;1秒计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器复位信号。

这个复位信号可以由一个测频控制信号发生器产生,即图1中的TESTCTL,它的设计要求是,TESTCTL 的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT10的EN使能端进行同步控制。

当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。

在停止计数期间,每0.01ms锁存器进行一次锁存,并由数码管显示计数值。

设置锁存器是为了使显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号之后,必须有一清零信号RST_CNT对计数器进行清零,为下1秒钟的计数操作准备。

图3 芯片信息配置由于我们所采用的板子为RCXQ208_V5 FPGA开发板,所以配置如图所示。

1、新建各个分模块并输入代码。

图4 建立VHDL文件2、建立顶层文件为原理图型,例化各个模块并连接。

图5 建立VHDL文件3、对设计进行综合,如果出现错误,根据提示改正。

图6 综合黄色感叹符号代表有警告,有些警告可以忽略,绿色小勾表示综合成功。

4、建立测试文件并进行仿真,验证设计。

图7 建立激励文件之后一直点击确认即可。

为了结合我们的下载板子的时钟信号,在测试文件中设置时钟单位为10ns,精度为1ps,如图:图8 设置时钟单位仿真文件应验证个端口的正确性。