74ls138中文资料_数据手册_参数

- 格式:pdf

- 大小:1.68 MB

- 文档页数:9

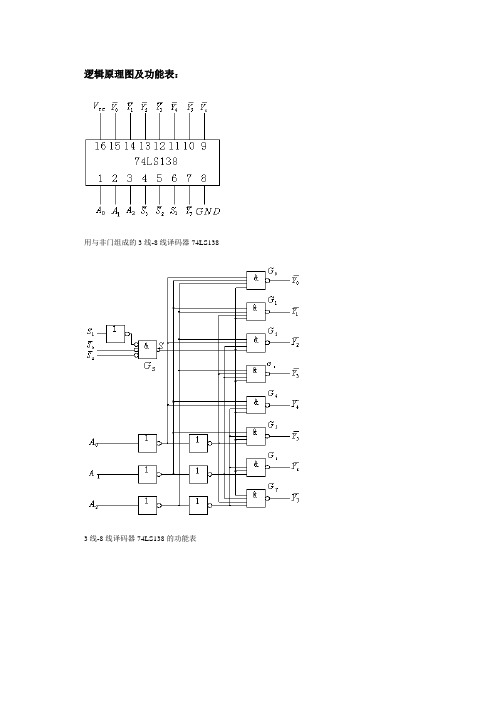

逻辑原理图及功能表:用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

解:由图3.3.8可见,74LS138仅有3个地址输入端。

如果想对4位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。

取第(1)片74LS138的和作为它的第四个地址输入端(同时令),取第(2)片的作为它的第四个地址输入端(同时令),取两片的、、,并将第(1)片的和接至,将第(2)片的接至,如图3.3.9所示,于是得到两片74LS138的输出分别为图3.3.9 用两片74LS138接成的4线-16线译码器式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。

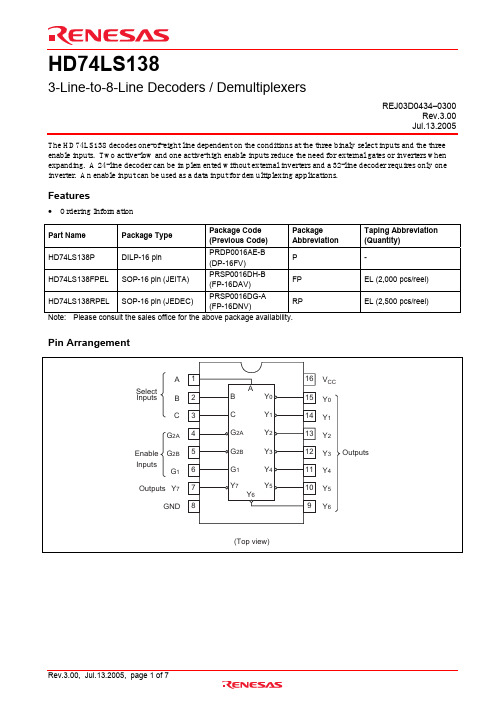

HD74LS1383-Line-to-8-Line Decoders / DemultiplexersREJ03D0434–0300Rev.3.00Jul.13.2005The HD74LS138 decodes one-of-eight line dependent on the conditions at the three binaly select inputs and the three enable inputs. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented without external inverters and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.Features• Ordering InformationPart Name Package Type Package Code(Previous Code)PackageAbbreviationTaping Abbreviation(Quantity)HD74LS138P DILP-16pin PRDP0016AE-B(DP-16FV)P -HD74LS138FPEL SOP-16 pin (JEITA) PRSP0016DH-B(FP-16DAV)FP EL (2,000 pcs/reel)HD74LS138RPEL SOP-16 pin (JEDEC) PRSP0016DG-A(FP-16DNV)RP EL (2,500 pcs/reel)Note: Please consult the sales office for the above package availability. Pin ArrangementFunction TableInputsEnable Select OutputsG1 G2* C B A Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7X H X X X H H H H H H H H L X X X X H H H H H H H H H L L L L L H H H H H H H H L L L H H L H H H H H H H L L H L H H L H H H H H H L L H H H H H L H H H H H L H LL H H H H L H H H H L H L H H H H H H L H H H L H H L H H H H H H L H H L H H H H H H H H H H L H ; high level, L ; low level, X ; irrelevant * ; G 2 = G 2A + G 2BBlock DiagramAbsolute Maximum RatingsItem Symbol Ratings UnitSupply voltage V CC 7 VInput voltage V IN 7 V Power dissipation P T 400 mWStorage temperatureTstg–65 to +150°CNote: Voltage value, unless otherwise noted, are with respect to network ground terminal.Recommended Operating ConditionsItem Symbol Min Typ Max UnitSupply voltage V CC 4.75 5.00 5.25 V I OH — — –400 µAOutput currentI OL — — 8 mAOperating temperature Topr –20 25 75 °CElectrical Characteristics(Ta = –20 to +75 °C)ItemSymbol min. typ.* max. Unit ConditionV IH 2.0 — — V Input voltageV IL — — 0.8 VV OH 2.7 — — VV CC = 4.75 V, V IH = 2 V, V IL = 0.8 V, I OH = –400 µA— — 0.4 I OL = 4 mA Output voltageV OL — — 0.5 VI OL = 8 mA V CC = 4.75 V, V IH = 2 V,V IL = 0.8 VI IH — — 20 µA V CC = 5.25 V, V I = 2.7 V I IL — — –0.4 mA V CC = 5.25 V, V I = 0.4 VInput currentI I —— 0.1 mA V CC = 5.25 V, V I = 7 V Short-circuit outputcurrentI OS –20— –100 mA V CC = 5.25 V Supply current I CC — 6.3 10 mA V CC = 5.25 V, Outputs enabled and open Input clamp voltage V IK — — –1.5 V V CC = 4.75 V, I IN = –18 mA Note: * V CC = 5 V, Ta = 25°CSwitching Characteristics(V CC = 5 V, Ta = 25°C)Item Symbol Inputs Output Levelsof delaymin. typ. max. Unit Conditiont PLH — 13 20 nst PHL 2 — 27 41 nst PLH — 18 27 nst PLH BinaryselectA, B, C Y 3— 26 39 ns t PLH — 12 18 ns t PHLEnableG 2A , G 2B 2— 21 32 ns t PLH — 17 26 ns Propagationdelay time t PLH EnableG 1 Y3— 25 38 ns C L = 15 pF,R L = 2 k ΩTesting Method Test CircuitWaveformRelation Between Input and Output to Levels of DelayOutputsInputs2 levels of delay3 levels of delayA Y0Y2Y4Y6Y1Y3Y5Y7B Y0Y1Y4Y5Y2Y3Y6Y7C Y0Y1Y2Y3Y4Y5Y6Y7G1Y0 to Y7G2A, G2B Y0 to Y7Package Dimensions RENESAS SALES OFFICESRefer to "/en/network" for the latest and detailed information.Renesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500, Fax: <1> (408) 382-7501Renesas Technology Europe LimitedDukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900Renesas Technology Hong Kong Ltd.7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong KongTel: <852> 2265-6688, Fax: <852> 2730-6071Renesas Technology Taiwan Co., Ltd.10th Floor, No.99, Fushing North Road, Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology (Shanghai) Co., Ltd.Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, ChinaTel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952Renesas Technology Singapore Pte. Ltd.1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001Renesas Technology Korea Co., Ltd.Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, KoreaTel: <82> 2-796-3115, Fax: <82> 2-796-2145Renesas Technology Malaysia Sdn. Bhd.Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, MalaysiaTel: <603> 7955-9390, Fax: <603> 7955-9510。

74ls138芯片的功能

74LS138芯片是一种3-8译码器/解码器芯片,常用于数字电路设计中。

它的主要功能是将三位二进制输入信号转换为八个输出信号,用于实现多种不同的功能,如地址译码、数据选择等。

74LS138芯片有三个输入引脚,分别是A0、A1和A2,用于

输入三位的二进制编码。

它还有八个输出引脚,分别是Y0、

Y1、Y2、Y3、Y4、Y5、Y6和Y7,用于输出相应的二进制

编码。

在74LS138芯片中,输入信号通过内部逻辑电路被译码为活

动低电平信号,也就是说当对应的输入信号为“0”时,相应的

输出引脚会输出低电平。

而当对应的输入信号为“1”时,相应

的输出引脚会输出高电平。

作为一个3-8译码器/解码器,74LS138芯片可以实现多种不同的功能。

最常见的应用是地址译码。

在一个多路复用器中,当控制信号为三位二进制编码时,使用74LS138芯片可以将对

应的输入信号译码为八个输出信号,用于选择相应的通路。

此外,74LS138芯片还可以用于数据选择。

通过将输入信号与

选择信号进行逻辑与门操作,可以选择我们想要的数据进行输出,而将其他数据屏蔽。

此外,74LS138芯片还有一些其他的应用,例如时序控制,多

功能逻辑控制等。

通过合理的配置输入信号和选择信号,可以实现不同的功能。

总结起来,74LS138芯片是一种常用的3-8译码器/解码器芯片,它能够将三位的二进制输入信号译码为八个输出信号,用于实现多种不同的功能。

它在数字电路设计中具有广泛的应用,如地址译码、数据选择、时序控制等。

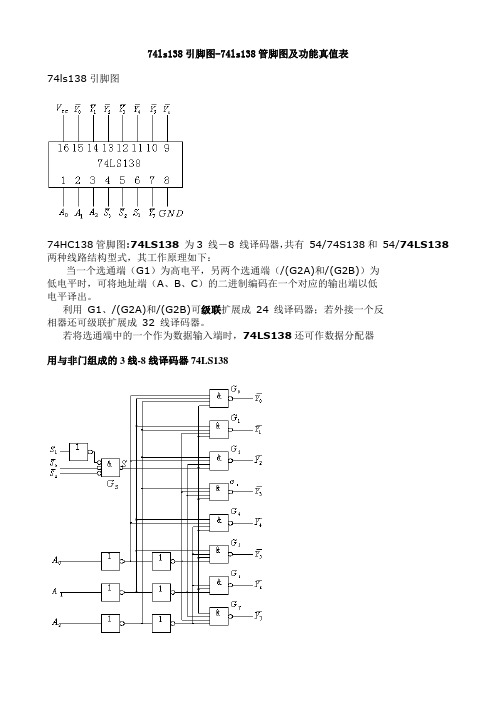

74ls138引脚图-74ls138管脚图及功能真值表74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

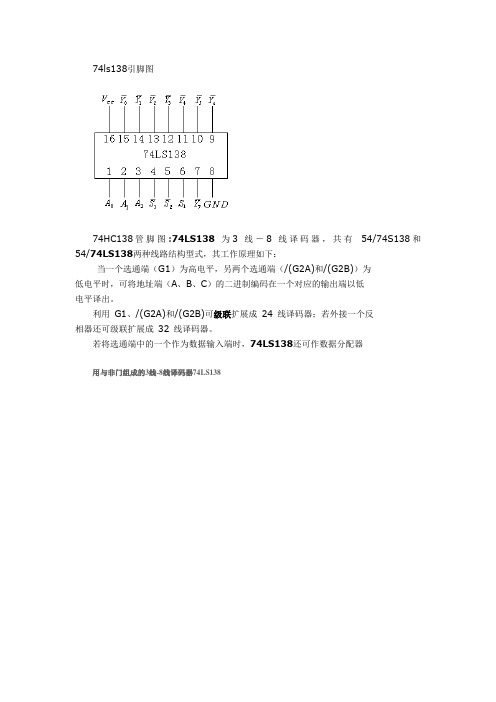

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74系列芯片数据手册大全本文将为大家介绍74系列芯片数据手册的大全,主要是介绍各种74系列芯片的应用以及参数等相关信息。

一、常用的74系列芯片有哪些?74系列芯片是最常用的数字集成电路之一,主要包括以下几种芯片:1. 74LS00:四个二输入与门。

6. 74LS74:双D触发器。

8. 74LS138:三线八选一译码器。

9. 74LS151:八路数据选择器/复用器。

10. 74LS161:四位二进制同步计数器。

11. 74LS240:三态缓冲器。

13. 74LS373:透明锁存器。

16. 74LS595:8位移位寄存器。

二、74LS00芯片的应用及参数74LS00芯片是一种四个二输入与门的数字集成电路,通常用于逻辑门的实现和数字电路的设计。

该芯片可以从以下几方面进行分析:1. 参数描述该芯片内部具有四个与门,每个与门都有两个输入端和一个输出端。

输入端的输入电压范围通常为0V-5V,输出电平为低电平(0V)或高电平(5V),输出电流为16mA。

该芯片的工作电压范围为4.75V-5.25V,工作温度范围为0°C-70°C或-40°C-85°C。

2. 应用领域74LS00芯片通常用于逻辑门的实现和数字电路的设计,例如计数器、锁存器、转换器、寄存器等电路。

由于其适用于逻辑运算,因此在数字电路的开发中已经成为一种非常重要的芯片。

3. 管脚说明该芯片的14个管脚可以分为四类:电源引脚(VCC和GND)、输入引脚(A1、A2、B1、B2、C1、C2、D1和D2)、输出引脚(Y1、Y2、Y3和Y4)和负载引脚。

其中,电源引脚VCC 和GND是给电源提供电的,输入引脚是二进制的输入信号,输出引脚是二进制的输出信号,负载引脚是与其它数字电路相连的终端。

4. 使用方法在使用74LS00芯片时,需要将芯片的电源引脚接到适当的电源上,然后将输入引脚所接收到的二进制值输入到芯片中,芯片会处理这些二进制数值并输出相应结果。

74LS138中文资料54LS138和74LS138 为3 线-8 线译码器共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:54LS138 /74LS138 传播延迟时间22ns 功耗32mW原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图1 引脚图图2 内部逻辑管脚图引脚功能:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)真值表:建议操作条件:电气参数:符号参数测试条件最大值典型值最大值单位VI 输入钳位电压VCC = Min, II = -18 mA- - -1.5 VVOH 输出高电平电压VCC = Min, IOH = Max,VIL = Max, VIH = Min2.73.4 - VVOL 输出低电平电压VCC = Min, IOL = Max,VIL = Max, VIH = Min- 0.35 0.5V IOL = 4 mA, VCC = Min - 0.25 0.4II 最大输入电压时输入电流VCC = Max, VI = 7V - - 0.1 mAIIH 输入高电平电流VCC = Max, VI = 2.7V - - 20 mA IIL 输入低电平电流VCC = Max, VI = 0.4V - - -0.36 mA IOS 输出短路电流VCC = Max (Note 4) -20 - -100 mA ICC 电源电流VCC = Max (Note 5) - 6.3 10 mA 动态特性表:符号参数To (Output) 时滞RL = 2 kW单位CL = 15pF CL = 50 pF最大值最大值最大值最大值tPLH 低到高电平输出传递延迟时间Select to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 2 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Select to Output 3 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 3 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Enable to Output 2 - 24 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 3 - 18 - 27 nstPHL 传递延迟时间Enable to Output 3 - 28 - 40 ns。

74ls138译码器内部电路逻辑图功能表简单应用74HC138:74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138<74ls138译码器内部电路>3线-8线译码器74LS138的功能表<74ls138功能表>无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出<74ls138逻辑图>由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

Hitachi CodeJEDECEIAJWeight (reference value)DP-16 Conforms Conforms 1.07 gHitachi Code JEDEC EIAJWeight (reference value)FP-16DA —Conforms 0.24 g*Dimension including the plating thicknessBase material dimension° – 8°Hitachi CodeJEDECEIAJWeight (reference value)FP-16DNConformsConforms0.15 gUnit: mm*Dimension including the plating thickness Base material dimension° – 8°元器件交易网Cautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

74ls系列芯⽚功能和参数详细介绍74、74HC、74LS系列芯⽚资料系列电平典型传输延迟ns 最⼤驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯⽚,逻辑功能上是⼀样的。

74LSxx的使⽤说明如果找不到的话,可参阅74xx 或74HCxx的使⽤说明。

有些资料⾥包含了⼏种芯⽚,如74HC161资料⾥包含了74HC160、74HC161、74HC162、74HC163四种芯⽚的资料。

找不到某种芯⽚的资料时,可试着查看⼀下临近型号的芯⽚资料。

7400 QUAD 2-INPUT NAND GATES 与⾮门7401 QUAD 2-INPUT NAND GATES OC 与⾮门7402 QUAD 2-INPUT NOR GATES 或⾮门7403 QUAD 2-INPUT NAND GATES 与⾮门7404 HEX INVERTING GATES 反向器7406 HEX INVERTING GATES HV ⾼输出反向器7408 QUAD 2-INPUT AND GATE 与门7409 QUAD 2-INPUT AND GATES OC 与门7410 TRIPLE 3-INPUT NAND GATES 与⾮门7411 TRIPLE 3-INPUT AND GATES 与门74121 ONE-SHOT WITH CLEAR 单稳态74132 SCHMITT TRIGGER NAND GATES 触发器与⾮门7414 SCHMITT TRIGGER INVERTERS 触发器反向器74153 4-LINE TO 1 LINE SELECTOR 四选⼀74155 2-LINE TO 4-LINE DECODER 译码器74180 PARITY GENERATOR/CHECKER 奇偶发⽣检验74191 4-BIT BINARY COUNTER UP/DOWN 计数器7420 DUAL 4-INPUT NAND GATES 双四输⼊与⾮门7426 QUAD 2-INPUT NAND GATES 与⾮门7427 TRIPLE 3-INPUT NOR GATES 三输⼊或⾮门7430 8-INPUT NAND GATES ⼋输⼊端与⾮门7432 QUAD 2-INPUT OR GATES ⼆输⼊或门7438 2-INPUT NAND GATE BUFFER 与⾮门缓冲器7445 BCD-DECIMAL DECODER/DRIVER BCD译码驱动器7474 D-TYPE FLIP-FLOP D型触发器7475 QUAD LATCHES 双锁存器7476 J-K FLIP-FLOP J-K触发器7485 4-BIT MAGNITUDE COMPARATOR 四位⽐较器7486 2-INPUT EXCLUSIVE OR GATES 双端异或门74HC00 QUAD 2-INPUT NAND GATES 双输⼊与⾮门74HC02 QUAD 2-INPUT NOR GATES 双输⼊或⾮门74HC03 2-INPUT OPEN-DRAIN NAND GATES 与⾮门74HC04 HEX INVERTERS 六路反向器74HC05 HEX INVERTERS OPEN DRAIN 六路反向器74HC08 2-INPUT AND GATES 双输⼊与门74HC107 J-K FLIP-FLOP WITH CLEAR J-K触发器74HC109A J-K FLIP-FLOP W/PRESET J-K触发器74HC11 TRIPLE 3-INPUT AND GATES 三输⼊与门74HC112 DUAL J-K FLIP-FLOP 双J-K触发器74HC113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74HC123A RETRIGGERABLE MONOSTAB 可重触发单稳74HC125 TRI-STATE QUAD BUFFERS 四个三态门74HC126 TRI-STATE QUAD BUFFERS 六三态门74HC132 2-INPUT TRIGGER NAND 施密特触发与⾮门74HC133 13-INPUT NANDGATES ⼗三输⼊与⾮门74HC137 3-TO-8 DECODERS W/LATCHES 3-8线译码器74HC138 3-8 LINE DECODER 3线⾄8线译码器74HC139 2-4 LINE DECODER 2线⾄4线译码器74HC14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74HC151 8-CHANNEL DIGITAL MUX 8通道多路器74HC153 DUAL 4-INPUT MUX 双四输⼊多路器74HC154 4-16 LINE DECODER 4线⾄16线译码器74HC155 2-4 LINE DECODER 2线⾄4线译码器74HC157 QUAD 2-INPUT MUX 四个双端多路器74HC161 BINARY COUNTER ⼆进制计数器74HC163 DECADE COUNTERS ⼗进制计数器74HC164 SERIAL-PARALLEL SHIFT REG 串⼊并出74HC165 PARALLEL-SERIAL SHIFT REG 并⼊串出74HC166 SERIAL-PARALLEL SHIFT REG 串⼊并出74HC173 TRI-STATE D FLIP-FLOP 三态D触发器74HC174 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC175 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC181 ARITHMETIC LOGIC UNIT 算术逻辑单元74HC182 LOOK AHEAD CARRYGENERATR 进位发⽣器74HC190 BINARY UP/DN COUNTER ⼆进制加减计数器74HC191 DECADE UP/DN COUNTER ⼗进制加减计数器74HC192 DECADE UP/DN COUNTER ⼗进制加减计数器74HC193 BINARY UP/DN COUNTER ⼆进制加减计数器74HC194 4BIT BI-DIR SHIFT 4位双向移位寄存器74HC195 4BIT PARALLEL SHIFT 4位并⾏移位寄存器74HC20 QUAD 4-INPUT NAND GATE 四个四⼊与⾮门74HC221A NON-RETRIG MONOSTAB 不可重触发单稳74HC237 3-8 LINE DECODER 地址锁3线⾄8线译码器74HC242/243 TRI-STAT TRANSCEIVER 三态收发器74HC244 OCTAL 3-STATE BUFFER ⼋个三态缓冲门74HC245 OCTAL 3-STATE TRANSCEIVER 三态收发器74HC251 8-CH 3-STATE MUX 8路3态多路器74HC253 DUAL 4-CH 3-STATE MUX 4路3态多路器74HC257 QUAD 2-CH 3-STATE MUX 4路3态多路器74HC258 2-CH 3-STATE MUX 2路3态多路器74HC259 3-8 LINE DECODER 8位地址锁存译码器74HC266A 2-INPUT EXCLUSIVE NOR GATE 异或⾮74HC27 TRIPLE 3-INPUT NOR GATE三个3输⼊或⾮门74HC273 OCTAL D FLIP-FLOP CLEAR 8路D触发器74HC280 9BIT ODD/EVEN GENERATOR 奇偶发⽣器74HC283 4BIT BINARY ADDER CARRY 四位加法器74HC299 3-STATE UNIVERSAL SHIFT 三态移位寄存74HC30 8-INPUT NAND GATE 8输⼊端与⾮门74HC32 QUAD 2-INPUT OR GATE 四个双端或门74HC34 NON-INVERTER ⾮反向器74HC354 8-CH 3-STATE MUX 8路3态多路器74HC356 8-CH 3-STATE MUX 8路3态多路器74HC365 HEX 3-STATE BUFFER 六个三态缓冲门74HC366 3-STATE BUFFER INVERTER 缓冲反向器74HC367 3-STATE BUFFER INVERTER 缓冲反向器74HC368 3-STATE BUFFER INVERTER 缓冲反向器74HC373 3-STATE OCTAL D LATCHES 三态D型锁存器74HC374 3-STATE OCTAL D FLIPFLOP 三态D触发器74HC393 4-BIT BINARY COUNTER 4位⼆进制计数器74HC4016 QUAD ANALOG SWITCH 四路模拟量开关74HC4020 14-Stage Binary Counter 14输出计数器74HC4017 Decade Counter/Divider with 10 Decoded Outputs ⼗进制计数器带10个译码输出端74HC4040 12 Stage Binary Counter 12出计数器74HC4046 PHASE LOCK LOOP 相位监测输出器74HC4049 LEVEL DOWN CONVERTER 电平变低器74HC4050 LEVEL DOWN CONVERTER 电平变低器74HC4051 8-CH ANALOG MUX 8通道多路器74HC4052 4-CH ANALOG MUX 4通道多路器74HC4053 2-CH ANALOG MUX 2通道多路器74HC4060 14-STAGE BINARY COUNTER 14阶BIN计数74HC4066 QUAD ANALOG MUX 四通道多路器74HC4075 TRIPLE 3-INPUT OR GATE 3输⼊或门74HC42 BCD TO DECIMAL BCD转⼗进制译码器74HC423A RETRIGGERABLE MONOSTAB 可重触发单稳74HC4511 BCD-7 SEG DRIVER/DECODER 7段译码器74HC4514 4-16 LINE DECODER 4⾄16线译码器74HC4538A RETRIGGERAB MONOSTAB 可重触发单稳74HC4543 LCD BCD-7 SEG LCD⽤的BCD-7段译码驱动74HC51 AND OR GATE INVERTER 与或⾮门74HC521 8BIT MAGNITUDE COMPARATOR 判决定路74HC533 3-STATE D LATCH 三态D锁存器74HC534 3-STATE D FLIP-FLOP 三态D型触发器74HC540 3-STATE BUFFER 三态缓冲器74HC541 3-STATE BUFFER INVERTER三态缓冲反向器74HC58 DUAL AND OR GATE 与或门74HC589 3STATE 8BIT SHIFT 8位移位寄存三态输出74HC594 8BIT SHIFT REG 8位移位寄存器74HC595 8BIT SHIFT REG 8位移位寄存器出锁存74HC597 8BIT SHIFT REG 8位移位寄存器⼊锁存74HC620 3-STATE TRANSCEIVER 反向3态收发器74HC623 3-STATE TRANSCEIVER ⼋路三态收发器74HC640 3-STATE TRANSCEIVER 反向3态收发器74HC643 3-STATE TRANSCEIVER ⼋路三态收发器74HC646 NON-INVERT BUS TRANSCEIVER 总线收发器74HC648 INVERT BUS TRANCIVER 反向总线收发器74HC688 8BIT MAGNITUDE COMPARATOR 8位判决电路74HC7266 2-INPUT EXCLUSIVE NOR GATE 异或⾮门74HC73 DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器74HC74A PRESET/CLEAR D FLIP-FLOP 双D触发器74HC75 4BIT BISTABLE LATCH 4位双稳锁存器74HC76 PRESET/CLEAR JK FLIP-FLOP 双JK触发器74HC85 4BIT MAGNITUDE COMPARATOR 4位判决电路74HC86 2INPUT EXCLUSIVE OR GATE 2输⼊异或门74HC942 BAUD MODEM 300BPS低速调制解调器74HC943 300 BAUD MODEM 300BPS低速调制解调器74LS00 QUAD 2-INPUT NAND GATES 与⾮门74LS02 QUAD 2-INPUT NOR GATES 或⾮门74LS03 QUAD 2-INPUT NAND GATES 与⾮门74LS04 HEX INVERTING GATES 反向器74LS05 HEX INVERTERS OPEN DRAIN 六路反向器74LS08 QUAD 2-INPUT AND GATE 与门74LS09 QUAD 2-INPUT AND GATES OC 与门74LS10 TRIPLE 3-INPUT NAND GATES 与⾮门74LS109 QUAD 2-INPUT AND GATES OC 与门74LS11 TRIPLE 3-INPUT AND GATES 与门74LS112 DUAL J-K FLIP-FLOP 双J-K触发器74LS113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74LS114 NEGATIVE J-K FLIP-FLOP 负沿J-K触发器74LS122 Retriggerable Monostab 可重触发单稳74LS123 Retriggerable Monostable 可重触发单稳74LS125 TRI-STATE QUAD BUFFERS 四个三态门74LS13 QUAL 4-in NAND TRIGGER 4输⼊与⾮触发器74LS160 BCD DECADE 4BIT BIN COUNTERS 计数器74LS136 QUADRUPLE 2-INPUT XOR GATE 异或门74LS138 3-8 LINE DECODER 3线⾄8线译码器74LS139 2-4 LINE DECODER 2线⾄4线译码器74LS14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74LS151 8-CHANNEL DIGITAL MUX 8通道多路器74LS153 DUAL 4-INPUT MUX 双四输⼊多路器74LS155 2-4 LINE DECODER 2线⾄4线译码器74LS156 2-4 LINE DECODER/DEMUX 2-4译码器74LS157 QUAD 2-INPUT MUX 四个双端多路器74LS158 2-1 LINE MUX 2-1线多路器74LS160A BINARY COUNTER ⼆进制计数器74LS161A BINARY COUNTER ⼆进制计数器74LS162A BINARY COUNTER ⼆进制计数器74LS163A DECADE COUNTERS ⼗进制计数器74LS164 SERIAL-PARALLEL SHIFT REG 串⼊并出74LS168 BI-DIRECT BCD TO DECADE 双向计数器74LS1694BIT UP/DN BIN COUNTER 四位加减计数器74LS173 TRI-STATE D FLIP-FLOP 三态D触发器74LS174 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS175 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS190 BINARY UP/DN COUNTER ⼆进制加减计数器74LS191 DECADE UP/DN COUNTER ⼗进制加减计数器74LS192 DECADE UP/DN COUNTER ⼗进制加减计数器74LS193BINARY UP/DN COUNTER ⼆进制加减计数器74LS194A 4BIT BI-DIR SHIFT 4位双向移位寄存器74LS195A 4BIT PARALLEL SHIFT4位并⾏移位寄存器74LS20 QUAD 4-INPUT NAND GATE 四个四⼊与⾮门74LS21 4-INPUT AND GATE 四输⼊端与门74LS240 OCTAL 3-STATE BUFFER ⼋个三态缓冲门74LS244 OCTAL 3-STATE BUFFER ⼋个三态缓冲门74LS245 OCTAL 3-STATE TRANSCEIVER 三态收发器74LS253 DUAL 4-CH 3-STATE MUX 4路3态多路器74LS256 4BIT ADDRESS LATCH 四位可锁存锁存器74LS257 QUAD 2-CH 3-STATE MUX 4路3态多路器74LS258 2-CH 3-STATE MUX 2路3态多路器74LS27 TRIPLE 3-INPUT NOR GATES 三输⼊或⾮门74LS279 QUAD R-S LATCHES 四个RS⾮锁存器74LS28 QUAD 2-INPUT NOR BUFFER 四双端或⾮缓冲74LS283 4BIT BINARY ADDER CARRY 四位加法器74LS30 8-INPUT NAND GATES ⼋输⼊端与⾮门74LS32 QUAD 2-INPUT OR GATES ⼆输⼊或门74LS352 4-1 LINE SELECTOR/MUX 4-1线选择多路器74LS365 HEX 3-STATE BUFFER 六个三态缓冲门74LS367 3-STATE BUFFER INVERTER 缓冲反向器74LS368A 3-STATE BUFFER INVERTER 缓冲反向器74LS373 OCT LATCH W/3-STATE OUT三态输出锁存器74LS76 Dual JK Flip-Flop w/set 2个JK触发器74LS379 QUAD PARALLEL REG 四个并⾏寄存器74LS38 2-INPUT NAND GATE BUFFER 与⾮门缓冲器74LS390 DUAL DECADE COUNTER 2个10进制计数器74LS393 DUAL BINARY COUNTER 2个2进制计数器74LS42 BCD TO DECIMAL BCD转⼗进制译码器74LS48 BCD-7 SEG BCD-7段译码器74LS49 BCD-7 SEG BCD-7段译码器74LS51 AND OR GATE INVERTER 与或⾮门74LS540 OCT Buffer/Line Driver 8路缓冲驱动器74LS541 OCT Buffer/LineDriver 8路缓冲驱动器74LS74 D-TYPE FLIP-FLOP D型触发器74LS682 8BIT MAGNITUDE COMPARATOR 8路⽐较器74LS684 8BIT MAGNITUDE COMPARATOR 8路⽐较器74LS75 QUAD LATCHES 双锁存器74LS83A 4BIT BINARY ADDER CARRY 四位加法器74LS85 4BIT MAGNITUDE COMPARAT 4位判决电路74LS86 2INPUT EXCLUSIVE OR GATE 2输⼊异或门74LS90 DECADE/BINARY COUNTER ⼗/⼆进制计数器74LS95B4BIT RIGHT/LEFT SHIFT 4位左右移位寄存74LS688 8BIT MAGNITUDE COMPARAT 8位判决电路74LS136 2-INPUT XOR GATE 2输⼊异或门74LS651 BUS TRANSCEIVERS 总线收发器74LS653 BUS TRANSCEIVERS 总线收发器74LS670 3-STATE 4-BY-4 REG 3态4-4寄存器74LS73A DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器。