信号一致性测试

- 格式:pdf

- 大小:431.07 KB

- 文档页数:5

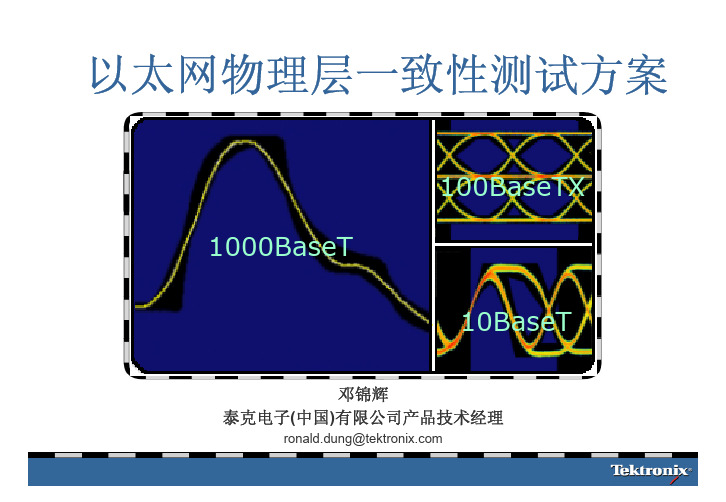

以太网物理层一致性测试方案100BaseTX1000BaseT10BaseT邓锦辉泰克电子(中国)有限公司产品技术经理ronald.dung@Xerox Altos 工作站与其他Xerox Altos2.94Mb/s的数据传输率, 并命名为Alto Aloha IEEE 802.3以太网的物理层种类:4DTE Power via MDI (Media Dependent Interface) :发送端透过以太网向远端设备供电410BaseT负责通道编码, 使用跳跃到”-“, “1”= 由”-“跳4100BaseTx PCS(Physical Coding Sublayer)–在速度或以上的以太网物理层里才采4MII层4 bit的输入, PCS层会编译成5 bit Code-Group的输出. 上图为4B/5B编码对照表3-Level Multiple Level Transition Encoding MLT-3编码方法MLT-3 的眼图–所有+1, 0, -1, 341000BaseT PCS(Physical Coding Sublayer)–进行研数据被分为两个子块4对线,并且同时收发,在全编码方法实现1000MB/s的MLT-34D-PAM54D-PAM5编码方法,+2,+1,0,-1,-2共5个幅度对2bit进行编码Intel 2002 Fall IDF时对以太网市场的预测:倍的数据传输率,增加了网络的带宽,支100BaseTx快10倍测试模式接着个最后是测试模式行模板测试,验证是否在规范所容许的范围内的要求ABDC F, GH, JTest Mode 1 Signal一按便自动测试所有点Template for Points A, B, C and D自动陈述测试结果是否通过?Template for Points F and H点击这里显示详细测试结果TDSET2软件TDSET2软件对模式1信号上的A,B,C,D共4点的峰值电压与它们之间的对称性,验证是否在峰值电压与对称性测试后的J点,测量它们的电压,验证插入的磁测试衰落时注意:F点后500ns的G点的电平Pt. F Pt. G首先测试不滤波的主控抖动, 若在不滤4不滤波的主控抖动4滤波的主控抖动测量时钟抖动的峰峰值是不滤波的主控抖动测试步骤4:对抖动波形进行滤波3.010ns4.000ns16.02nstxout pk-pk = 0.02ns –0.005ns = 0.015ns MDI 数据时钟测量MDI 数据相对于主控时钟的抖动J txout Pk-Pk 值4主控与从属有特殊的测试电缆相连起来主控与从属需要使用以下的特殊的测试电缆Test不滤波的从属抖动测试步骤5:对抖动波形进行滤波,3.010ns4.000ns16.02nspk-pk MDI 数据时钟测量从属MDI 数据相对于从属时钟的抖动J txout Pk-Pk 值准备完成1000BaseT物理层一致性测试任务TDS/CSA带宽示波器。

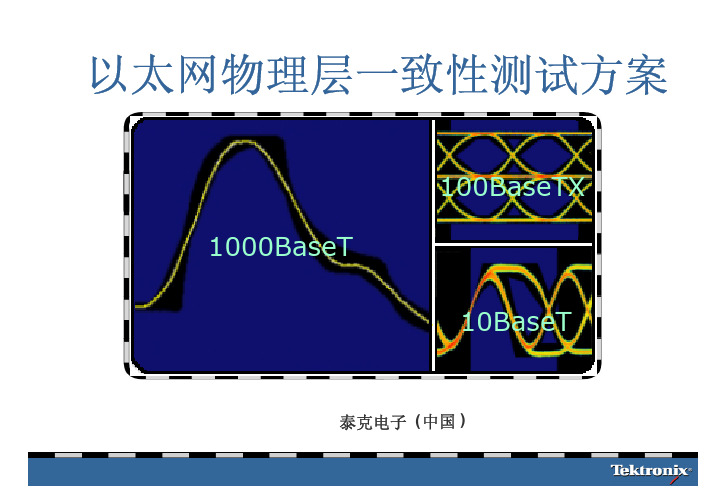

以太网物理层一致性测试方案100BaseTX1000BaseT10BaseT泰克电子(中国)Xerox Altos 工作站与其他Xerox Altos2.94Mb/s的数据传输率, 并命名为Alto Aloha IEEE 802.3以太网的物理层种类:4DTE Power via MDI (Media Dependent Interface) :发送端透过以太网向远端设备供电410BaseT负责通道编码, 使用跳跃到”-“, “1”= 由”-“跳4100BaseTx PCS(Physical Coding Sublayer)–在速度或以上的以太网物理层里才采4MII层4 bit的输入, PCS层会编译成5 bit Code-Group的输出. 上图为4B/5B编码对照表3-Level Multiple Level Transition Encoding MLT-3编码方法MLT-3 的眼图–所有+1, 0, -1, 341000BaseT PCS(Physical Coding Sublayer)–进行研数据被分为两个子块4对线,并且同时收发,在全编码方法实现1000MB/s的MLT-34D-PAM54D-PAM5编码方法,+2,+1,0,-1,-2共5个幅度对2bit进行编码Intel 2002 Fall IDF时对以太网市场的预测:倍的数据传输率,增加了网络的带宽,支100BaseTx快10倍测试模式接着个最后是测试模式行模板测试,验证是否在规范所容许的范围内的要求ABDC F, GH, JTest Mode 1 Signal一按便自动测试所有点Template for Points A, B, C and D自动陈述测试结果是否通过?Template for Points F and H点击这里显示详细测试结果TDSET2软件TDSET2软件对模式1信号上的A,B,C,D共4点的峰值电压与它们之间的对称性,验证是否在峰值电压与对称性测试后的J点,测量它们的电压,验证插入的磁测试衰落时注意:F点后500ns的G点的电平Pt. F Pt. G首先测试不滤波的主控抖动, 若在不滤4不滤波的主控抖动4滤波的主控抖动测量时钟抖动的峰峰值是不滤波的主控抖动测试步骤4:对抖动波形进行滤波3.010ns4.000ns16.02nstxout pk-pk = 0.02ns –0.005ns = 0.015ns MDI 数据时钟测量MDI 数据相对于主控时钟的抖动J txout Pk-Pk 值4主控与从属有特殊的测试电缆相连起来主控与从属需要使用以下的特殊的测试电缆Test不滤波的从属抖动测试步骤5:对抖动波形进行滤波,3.010ns4.000ns16.02nspk-pk MDI 数据时钟测量从属MDI 数据相对于从属时钟的抖动J txout Pk-Pk 值准备完成1000BaseT物理层一致性测试任务TDS/CSA带宽示波器。

串行数据物理层一致性测试系列之一一致性测试(compliance test)是PC行业为了满足PC的大规模生产所必须的、遵循相关电性能指标的step by step的测试。

以上是我个人对一致性测试的定义。

一致性测试的终极目的本不是为了产生测试报告,而是为了确保产品的一些关键接口的电性能指标满足要求,但在实际中,这种测试的终极目的似乎只为了产生测试报告。

一致性测试的自动化程度要求很高,希望操作过程越“傻瓜”越好。

一致性测试的测试项目繁多,我们往往不明白为什么要测试某些项目,更搞不明白这些项目差了一点会对产品的性能产生什么影响,譬如幅度对称性测试,要求正负幅度之差为5%以内,但如果测试出来的结果是幅值正负差为5.5%,怎么办?由于一致性测试的要求测试项目很多,在产品的开发调试阶段重点关注一些关键项目,如眼图、抖动测量。

一致性测试的一些共性问题有:示波器如何选择(示波器的带宽问题),理解各种测试项目的含义,如何将信号引到示波器(探头和夹具问题),如何使DUT发出测试码型(发包问题),测试报告,等等。

图一所示为一典型PC主板包括各种串行总线:PCI Express,SATA,FBDIMM,SAS,UWB,HDMI,USB,Ethernet(只是示意,标识的具体位置可能不对)。

此外,还有和HDMI相竞争的总线Display Port。

现在最热的当然是USB3.0。

各种总线都有自己的组织。

和这些组织搞好关系对于仪器厂家至关重要。

当然,这些组织的老大是Intel。

因此,和Intel搞好关系对于仪器厂家更是至关重要的。

下面我们列出这些组织及LeCroy目前和这些组织的关系。

1,LeCroy 是UNH -IOL组织(负责以太网)的特别贡献会员。

2,USB-IF很多年前就认证了LeCroy的测试方案,力科的2GHz 以上示波器都获得了认证。

下面是网站链接和拷屏截图:3,PCI-SIG很多年前就已批准了LeCroy的方案作为推荐方案,第四代示波器刚发布不久就批准为PCI-E 2.0的推荐方案。

CAN一致性测试CAN一致性测试在于缩小CAN网络中节点差异,保证CAN网络的环境稳定,有效提高CAN网络的抗干扰能力。

因此CAN节点的一致性测试就显得尤为重要。

随着新能源、智能网联等概念发展,车身CAN总线环境变得复杂及紊乱,CAN节点质量不稳定给主机厂安全性带来极大威胁。

所以,CAN一致性测试已成为保证CAN网络安全运行的重要手段,CAN一致性测试内容覆盖了物理层、链路层、应用层等测试需求,如表1 CAN一致性测试内容(节选)所示;其中包括了输入阈值、输出电压、采样点、位宽容忍度重点测试项目。

表1 CAN一致性测试内容(节选)一、输入阈值测试阈值测试分为隐形输入电压阈值和显性输入电压阈值。

节点Vdiff大于0.9V时必须识别显性,小于0.5V时必须识别隐性,在0.5V~0.9V 之间,属于不确定区域,Vdiff≤0.5V时,节点可以正常发送报文,否则说明节点工作处于异常状态;Vdiff>0.9V时,节点必须停止发送,如果不停止,说明节点依然识别成隐性电平,存在电平判断的误判;所以对设备进行输入阈值测试显得尤为重要。

测试目的在于检查DUT 的CAN_H 与CAN_L 的显/隐性输入电压阈值是否遵守ISO 11898-2 的定义。

具体输入电压阈值标准如表2 ISO 11898-2 输入电压阈值标准所示。

表2 ISO 11898-2 输入电压阈值标准1. 测试原理在表2 ISO 11898-2 输入电压阈值标准所示的总线负载和共模电压条件下,按照图1 隐性输入电压测试原理和图2 显形输入电压测试原理的测试原理进行隐/显性输入电压阈值测试。

图1 隐性输入电压测试原理图2 显形输入电压测试原理2. 判断依据DUT 在Vdiff≤0.5V(用户可自定义设置该范围)时,可以正常发送报文。

至少在Vdiff>0.9V (用户可输入)的情况下,DUT 应该停止发送帧。

二、输出电压测试CAN总线上面的信号幅值是接收节点能正确识别逻辑信号的保证;隐性状态下,若CAN_diff电压大于0.9V,则会使总线呈现持续显性状态,导致总线瘫痪;显性状态下,若CAN_diff电压低于1.5V,说明该节点驱动能力较弱,会导致显性电平判断错误,并且在强干扰环境容易出现电平翻转,导致总线故障;如图3 输出电压幅值引起错误所示。