运放稳定性之二:运放网络,SPICE分析

- 格式:pdf

- 大小:1.45 MB

- 文档页数:17

电压反馈运算放大器的稳定性分析及补偿技术1,介绍:电压反馈放大器(VFA)已经有60年的历史,但从第一天起,对电路的设计仍存在问题。

反馈系统是易变的和精密的,但总有不稳定的趋势。

运算放大器电路结构使用了一个高增益放大器,它的参数取决于外部的反馈元件,如果没有反馈元件,放大器的增益非常高。

最轻微的输入信号都会使输出饱合。

运放是一个通用元件,所以这个结构的研究要很细致,但结果在很多电压反馈电路中都是可用的。

电流反馈放大器(CFA)很象电压反馈放大器(VFA),但其间的差异很重要,在隔离反馈系统中应用时要确保CFA在掌控之中。

稳定性作为电子电路中的术语,常定义为实现无振荡状态,这是一个不准确不恰当的定义词汇。

稳定性是个相对概念,而其饱合使人们不易处理,因为相对地评判已经用尽,它很容易在一个电路之间画一条线,是振荡还是不振荡。

所以我们能了解为什么一些人相信振荡是稳定和不稳定之间的一条边界线。

反馈电路展示出一个拙劣的相位响应,过冲及振荡之前的振铃。

这些现象在电路设计时都要考虑到,而且是不希望有的。

本文不去涉及振荡器,于是相对的稳定性定义为一项性能。

根据此定义,当设计师决定在可接受的相对稳定的电路中有些折衷,相对的稳定性的测量是阻尼的比例(ζ)阻尼比的细节讨论见参考文件1。

阻尼比相对于相位移动是另一个稳定性的测量标准。

多数稳定电路都有较长的响应时间,低的带宽,高的精度及少的过冲。

欠稳定的电路有最快的响应时间,最高的带宽,低的精度及一些过冲。

放大器由有源元件诸如晶体管一类组成。

合适的晶体管参数象晶体管增益,提供一个漂移及初始的来自各方的非精密度。

所以放大器由这些元件组合时就存在了漂移和非精密状态。

而漂移和非精准要用负反馈来消除。

运放电路结构采用反馈系统使电路的传输函数与放大器特性无关。

做到了这一点,电路的传输函数就只取决于外部元件。

外部的无源元件几乎可以满足漂移和精度的规范,仅有成本和几何尺寸限制这些无源元件的使用。

运放稳定性分析环路稳定性基础引言本系列所采用的所有技术都将“以实例来定义”,而不管它在其他应用中能否用普通公式来表达。

为便于进行稳定性分析,我们在工具箱中使用了多种工具,包括数据资料信息、技巧、经验、SPICE仿真以及真实世界测试等,都将用来加快我们的稳定运放电路设计。

尽管很多技术都适用于电压反馈运放,但上述这些工具尤其适用于统一增益带宽小于20MHz的电压反馈运放。

选择增益带宽小于20MHz的原因是,随着运放带宽的增加,电路中的其他一些主要因素会形成回路,如印制板(PCB) 上的寄生电容、电容中的寄生电感以及电阻中的寄生电容与电感等。

我们下面介绍的大多数经验与技术并非仅仅是理论上的,而且是从利用增益带宽小于20MHz的运放、实际设计并构建真实世界电路中得来的。

本系列的第1部分回顾了进行稳定性分析所需的一些基本知识,并定义了将在整个系列中使用的一些术语。

波特图(曲线)基础幅度曲线的频率响应是电压增益改变与频率改变的关系。

这种关系可用波特图上一条以分贝(dB) 来表示的电压增益比频率(Hz) 曲线来描述。

波特幅度图被绘成一种半对数曲线:x轴为采用对数刻度的频率(Hz)、y轴则为采用线性刻度的电压增益(dB) ,y轴最好是采用方便的每主格45°刻度。

波特图的另一半则是相位曲线(相移比频率),并被描绘成以“度”来表示的相移比频率关系。

波特相位曲线亦被绘成一种半对数曲线:x轴为采用对数刻度的频率(Hz)、y轴为采用线性刻度的相移(度),y轴最好是采用方便的每主格45°刻度。

幅度波特图要求将电压增益转换成分贝(dB) 。

进行增益分析时,我们将采用以dB(定义为20Log10A)表示的电压增益,其中A为以伏/伏表示的电压增益。

在电压增益波特图上,增益随频率变化的斜线可定义成按+20dB/decade或-20dB/decade增加或减小。

另一种描述同样斜线的方法是按+6dB/octave 或-6dB/octave增加或减小(参见图1.4)以下推导证明了20dB/decade与6dB/octave的等效性:?A(dB) = A(dB) at fb – A(dB) at fa?A(dB) = [Aol(dB) - 20log10(fb/f1)] – [Aol(dB) - 20log10(fa/f1)]?A(dB) = Aol(dB) - 20log10(fb/f1) – Aol(dB) + 20log10(fa/f1)]?A(dB) = 20log10(fa/f1) – 20Log10(fb/f1)]?A(dB) = 20log10(fa/fb)?A(dB) = 20log10(1k/10k) = -20dB/decade?A(dB) = 20log10(fb/fc)?A(dB) = 20log10(10k/20k) = -6db/octave-20dB/decade = -6dB/octave因此:+20dB/decade = +6dB/octave -20dB/decade = -6dB/octave+40dB/decade = +12dB/octave -40dB/decade = -12dB/octave+60dB/decade = +18dB/Octave -60dB/decade = -18dB/Octave极点à单个极点响应在波特图(幅度或增益曲线)上具有按-20dB/decade 或-6db/octave斜率下降的特点。

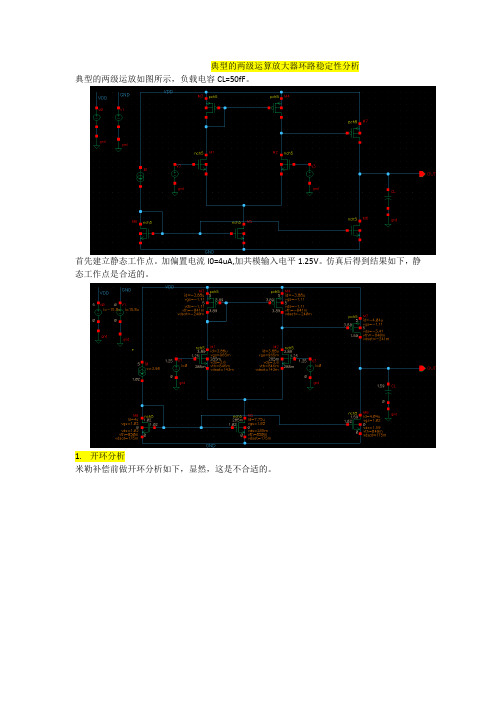

典型的两级运算放大器环路稳定性分析典型的两级运放如图所示,负载电容CL=50fF。

首先建立静态工作点。

加偏置电流I0=4uA,加共模输入电平1.25V。

仿真后得到结果如下,静态工作点是合适的。

1.开环分析米勒补偿前做开环分析如下,显然,这是不合适的。

加米勒补偿电容Cc=200fF,做开环分析如下,显然,这也是不合适的。

这是由于电路中存在零点造成的。

加入调零电阻Rz=40K,,仿真结果如下。

可以看出,,,相位裕度为40度,不够。

可通过加大补偿电容来进一步分裂p1,p2主次极点。

(已尝试过加米勒补偿电容Cc=300fF可以得到大于60度的相位裕度)。

但是本次设计的运放用在负反馈环路中,故只需要负反馈环路是稳定的就达到设计标准。

理论计算。

查看各管子的静态工作点。

,,,即。

,,,即。

,。

理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,,理论值与仿真结果非常接近。

,,理论值与仿真结果40度偏差较大。

2.在负反馈环路中做环路稳定性分析:从上图可以看出,加入反馈电阻网络R1,R2后就打破了原有的静态工作点:主要是反馈电阻网络R1,R2中的电流由M7管提供,所以M7管的静态工作点打破了,即运放的第二级跨导GmⅡ,输出电阻R2都变了。

从波特图中可以看出相位裕度为77度,满足设计标准。

理论计算:查看各管子的静态工作点。

,,,即。

,,,即。

,。

理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,理论值与仿真结果非常接近。

,,理论值与仿真结果77度偏差较大。

此结果可能是由于gm7变大,原来的调零电阻RZ过大造成的。

现在改变调零电阻Rz=25K,,仿真结果如下:此时,相位裕度为63度,满足设计标准。

3.改用大电感大电容仿真环路增益:仿真方法如上图所示,将环路断开,加入大电感L0=1GH通直流以建立直流工作点,并且断开交流通路,加入大电容C3=1GF通交流小信号V8。

从仿真结果图中可以看出相位裕度为70度。

不同的仿真方式所得到的结果略有误差。

运放的稳定性仿真分析上期文章《运放11-运放稳定性评估举例》文末提到了,如果我们有(放大器)的Sp(ic)e模型,可以借助(仿真)软件直接仿真电路的稳定性——可以直接得到波特图曲线,这一期就专门来看看具体怎么玩。

我们还是以上期的电路为例子,也就是下面这个电路:这里面的放大器TLV9062,使用的是(TI)官网的S(pi)ce模型,上期没有告诉大家如何使用LTspice导入第三方文件,这里先详细介绍下LTspice怎么用吧(我主要用这个软件做仿真,如果已经知道怎么导入第三方模型的兄弟,可以先跳过下面这一小节)。

LTspice导入TI的TLV9062的模型详细步骤1、TI官网(下载)tlv9062的spice模型,将文件tlv9062放置到库目录下面2、按下面步骤添加理想模型opamp2,放置好器件3、按快捷键“T”,选择“SPICE directive”,输入“.include tlv9062.lib”,点击“OK”4、右键运放,将opamp2改成“tlv9062”,这个模型就可以使用了学会了怎么添加第三方模型,我们下面就正式进入正题——如何仿真稳定性仿真的原理以下图为例,这个放大10倍的电路如何仿真稳定性呢?从前几期文章我们知道,稳定性分析的基本原理就是看环路增益,最直观的莫过于画出环路增益的波特图。

仿真原理就是依据这个:我们让(信号)在环路里面跑一圈,输出与输入的比值就是环路增益。

那如何求呢?容易想到,我们断开环路的一处节点,断开后就会得到两个端点,我们从一个端点注入信号Vin,那么信号跑一圈之后,在另外一个端点就会得到一个信号Vout,按照前面所说的,环路增益=Vout/Vin,我们使用软件画出Vout/Vin的曲线,这个曲线也就是环路增益曲线,通过曲线,我们就可以判断电路是否稳定了。

上面这一段话换成实操就是:1、去掉电路原本的激励输入,即V1两端短接2、剪开环路:剪开输出端到反馈(电阻)(一般都是剪开这里),得到两个端点,反馈那边命名为Vin,另外一个端点命名为Vout 如下图所示:我们在仿真软件里面直接运行右边的电路是否可行呢?答案是不行的,因为断开了反馈环路之后,这个运放的静态工作点受到了影响,即直流偏置不对,因此呢,我们还要把电路改造一下。

运算放大器的稳定性第2部分(共15部分):运放网络,SPICE分析作者:Tim Green,德州仪器公司2.0 引言本系列第2部分将着重分析运放电路(尤其是两种常见运放网络)的稳定性。

重要的是必须在进行SPICE仿真前先进行1阶分析(主要用您的经验来进行人工分析)。

请记住,如果您不掌握仿真前看到的东西,则电路仿真程序将导致GIGO(“垃圾进垃圾出”)。

我们将用SPICE环路增益测试法来进行,以便绘制Aol曲线、1/β曲线及环路增益曲线的波特图。

另外,我们还将采用易于构建的运放交流SPICE模型,以便对任何运放电路的交流稳定性进行快速分析。

在本系列中,我们将采用称为TINA的通用SPICE仿真软件来分析运放电路的稳定性并给出相应的结果。

通常将此软件称为Tina SPICE,您可以在上找到它的各种版本。

尽管所给出的一些SPICE技巧是针对TINA的,但您也会发现,您采用的其他SPICE软件也可从这些技巧中获益。

2.1 SPICE环路增益测试图2.0为SPICE环路增益测试的详细示意图。

LT提供一个直流闭环电路,因为每一个交流SPICE分析都要求有一个直流SPICE分析。

在进行交流SPICE分析时,随着频率增加,CT将逐渐变成短路而LT将逐渐变成开路,因此,可用一个SPICE程序来运行所有有关运放交流稳定性的信息。

利用图2.0给出的公式,很容易从SPICE 后处理上得到运放Aol、环路增益以及1/β幅度与相位曲线。

尽管有其他一些方法可用来“打破环路”并用SPICE来进行交流分析,但图2.0所示方法证明是一种误差最小以及在SPICE中造成数学差别最小的方法。

Op Amp AolOp Amp Aol1/β= dB[VM(3) / VM(1)]1/βPhase = VP(3) –VP(1)图2.0 SPICE环路增益测试图字:运放Aol增益=dB[VM(2)/VM(1)]运放Aol相位=[VP(2)-VP(1)]环路增益=dB[VM(3)/VM(2)]环路增益相位=[VP(3)-VP(2)]1/β=dB[VM(3)/VM(1)]1/β相位=[VP(3)-VP(1)]。

●Hello,and welcome to the TI Precision Lab supplement for op amp stability.●This lab will walk through detailed calculations,SPICE simulations,and real-worldmeasurements that greatly help to reinforce the concepts established in the stability video series.●你好,欢迎来到TI Precision Labs(德州仪器高精度实验室)的运放稳定性环节。

●这个实验会包括计算,SPICE仿真和实际测试。

这些环节帮助大家对视频中的概念加深理解。

●The detailed calculation portion of this lab can be done by hand,but calculationtools such as MathCAD or Excel can help greatly.●The simulation exercises can be performed in any SPICE simulator,since TexasInstruments provides generic SPICE models of the op amps used in this lab.However,the simulations are most conveniently done in TINA-TI,which is a free SPICE simulator available from the Texas Instruments website.TINA simulation schematics are embedded in the presentation.●Finally,the real-world measurements are made using a printed circuit board,orPCB,provided by Texas Instruments.If you have access to standard lab equipment,you can make the necessary measurements with any oscilloscope, function generator,Bode plotter,and±15V power supply.However,we highly recommend the VirtualBench from National Instruments.The VirtualBench is an all-in-one test equipment solution which connects to a computer over USB or Wi-Fi and provides power supply rails,analog signal generator and oscilloscope channels,and a5½digit multimeter for convenient and accurate measurements.This lab is optimized for use with the VirtualBench.●本实验的计算可以通过實際計算,如果使用Mathcad或者Excel这样工具会更好。

运算放大器的稳定性以及输入电容Ron Mancini[著]Kenny Kuang[译]Michael Chow[校]【声明】此文版权为Ti公司的Ron Mancini先生,原文名为Op amp stability and input capacitance,由于译者水平有限,时间匆忙,难免会有疏漏以及待斟酌之处,望各位热心的资深网友批评指正。

引言运算放大器的不稳定性可以通过外部的RC 网络进行补偿。

虽然有上千种不同的运放,但是他们都可以归结为两类:无补偿的和内部补偿的。

无补偿的运放通常需要外部的补偿来达到稳定性;而内部补偿也只是在无外部补偿网络的有限情况下是稳定的。

内部补偿的运放可能在下面几种情况下处于非稳态:驱动容性负载,在反相输入端加电容,在反馈回路中加入了引起相位变化的元件。

制作振荡电路就是利用反馈回路中的相移,这已经超出了本文的范畴。

输入电容很难避免,因为运放的引脚存在寄生电容,因此很多内部补偿的运放电路需要外部的补偿网络来保持稳定性。

输出电容的形式是以某种负载的方式出现的——电缆,转换器的输入电容或者滤波器的输入电容——而且在缓冲器结构中减小稳定性。

稳定性理论回顾图1中所示的运算放大器的理论是从参考文献1,第6章中摘录的。

环路增益A β非常关键,因为只有它才能决定了电路的稳定性。

为了稳定性分析,输入全都接地,因此输入电路和信号源对稳定性没有影响。

式1是当Z=R 时的环路增益方程。

GF GaR A R R β=+ (1)留心式1:它的简易性误导了人们,因为它简单的假设了A=a ,而这在所有的情况下都是不实际的。

稳定性可以简单的从一个环路增益-频率图中得出。

临界点位于环路增益为0dB (增益为1)的地方,因为一个电路的增益必须≥1时才变得不稳定。

相位裕度(已测得的相位角与180°的差值)可以在0dB 点计算出来。

这里我们用一个颇具代表性的TLV278x 系列运算放大器的开环增益曲线作为例子,如图2所示。

利用Pspice模型分析放大器环路的稳定性放大器放大器放大器的稳定性,但评估一个较为复杂的电路是否稳定,难度可能会大得多。

本文使用常见的Pspice宏模型结合一些简单的电路设计技巧来提高设计工程师的设计能力,以确保其设计的实用性与稳定性。

导致放大器不稳定的原因在任何相关频率下,只要环路增益不转变为正反馈,则闭环系统稳定。

环路增益是一个相量,因而具有幅度和相位特性。

环路由理想的负反馈转变为正反馈所带来的额外相移即是最常见的不稳定因素。

环路增益相位的“相关”频率,一般出现在环路增益大于或等于0dB之处。

图1:总等效噪声密度-反馈电阻关系曲线.的放大器电路,通过断开环路,测量信号在环路中传播一次所产生的相移,即可推算出电路的稳定情况.以下例子介绍的方法可利用仿真软件,运算放大器宏模型以及Pspice提供的理想元器件来实现。

图2:跨阻抗放大器。

高速低噪声跨阻放大器(TIA)稳定性示例我们以一个跨阻放大器(TIA)为例,通过分析其稳定性来阐述我们将要推荐的技术。

TIA广泛应用在工业领域和消费领域,例如LIDAR(光探测和测距)、条形码扫描仪、工厂自动化等。

设计工程师遇到的挑战是,在不会造成衰减和老化的情况下,如何最大化信噪比(SNR),以及如何获得足够的速度/带宽来传递所需的信号.图2为采用了LMH6629的放大器示意图,这款超高速(GBWP=4GHz)低噪声(0。

69nV/RtHz)器件具有+10V/V的最小稳定增益(COMP引脚连至VCC)的。

LMH6629的补偿(COMP)输入可以连至VEE,从而进一步将最小稳定增益降低到4V/V。

为获得最大的转换速率和带宽(小信号和大信号),在这个例子中,COMP引脚被连接到VCC。

可获得的带宽与放大器GBWP直接相关,与跨阻增益(RF)和光电二极管内的寄生电容成反比。

确定一个给定放大器所使用的反馈电阻(RF)有一个简单方便的办法:在使用了LMH6629的情况下,总等效输入电流噪声密度“ini”与RF的关系.图中的“in”是LMH6629的输入噪声电流,“en”是LMH6629的输入噪声电压,“k”是波尔兹曼常数,而“T”是用℃表示的绝对温度。

运放稳定性的SPICE仿真SPICE是一种检查电路潜在稳定性问题的有用工具。

本文将介绍一种使用SPICE工具来检查电路潜在稳定性的简单方法。

图1是使用OPA211 搭建的一个同相放大器,在许多应用中,只是对图1做了较小的变动。

R3和C1构成了输入级滤波器。

R4是电路的输出电阻,当运放输出级连接到其它外部电路时,R4起到保护作用。

CL用来等效5英尺电缆。

该电路的小信号阶跃响应或者方波的响应曲线是检查潜在稳定性问题的最快捷和最简单的方法。

图2是仿真电路。

值得注意的是电路输入端连接到地,输入测试信号源直接连接到运放的同相输入端。

输入级的滤波器将延缓输入信号的边沿。

如果你想知道一个钟是如何产生铃声的,你应该使用一个铁锤敲击它,而不是一个橡皮棒。

响应曲线是在运放的输出端探测,而不是电路的Vout节点。

R4和CL构成了滤波器以至于Vout节点不能真正地显示出运放的过冲。

为了检查稳定性,我们需要知道运放是如何工作的。

注意到输入信号的幅度是1mV(在运放输出端的幅度是4mV)。

我们希望得到小信号的响应曲线。

若输入信号是大信号,则会涉及到压摆率的问题,将减小过冲,不能真正地反应潜在的不稳定性。

从仿真结果可以看出,在运放的输出端有接近27%的过冲,较大的过冲会导致运放在任何条件下都是不稳定的。

假设这是一个二阶稳定系统,它意味着接近38度的相移裕量。

另外,注意到频率响应曲线中存在相当大的尖峰,这是另一个潜在的不稳定的迹象。

幅度峰值在14MHz时出现,其正好是时域上振铃周期的倒数。

普遍认为,当信号的过冲小于或等于20%时,相移裕量大于或。

运放稳定性第1部分(共15部分):环路稳定性基础1.0 引言本系列所采用的所有技术都将“以实例来定义”,而不管它在其他应用中能否用普通公式来表达。

为便于进行稳定性分析,我们在工具箱中使用了多种工具,包括数据资料信息、技巧、经验、SPICE 仿真以及真实世界测试等,都将用来加快我们的稳定运放电路设计。

尽管很多技术都适用于电压反馈运放,但上述这些工具尤其适用于统一增益带宽小于20MHz 的电压反馈运放。

选择增益带宽小于20MHz 的原因是,随着运放带宽的增加,电路中的其他一些主要因素会形成回路,如印制板 (PCB) 上的寄生电容、电容中的寄生电感以及电阻中的寄生电容与电感等。

我们下面介绍的大多数经验与技术并非仅仅是理论上的,而且是从利用增益带宽小于20MHz 的运放、实际设计并构建真实世界电路中得来的。

本系列的第1部分回顾了进行稳定性分析所需的一些基本知识,并定义了将在整个系列中使用的一些术语。

9Data Sheet Info 9Tricks 9Rules-Of-Thumb 9Tina SPICE Simulation9TestingGoal:EASILY Tricks & Rules-Of-Thumb apply for Voltage FeedbackOp Amps, Unity Gain Bandwidth <20MHzTo learn how to analyze and design Op Amp circuits for guaranteed Loop Stability using Data Sheet Info, Tricks, Rules-Of-Thumb, Tina SPICE Simulation, and Testing.Note:图1.0 稳定性分析工具箱图字(上、下):数据资料信息、技巧、经验、Tina SPICE 仿真、测试;目的:学习如何用数据资料信息、技巧、经验法则、Tina SPICE 仿真及测试来“更容易地”分析和设计运放,以确保环路稳定性;注:用于统一增益带宽小于20MHz 的电压反馈运放的技巧与经验法则。

运放稳定性第5部分(共15部分):单电源缓冲器电路的实际设计作者:Tim Green,德州仪器公司本系列的第5部分将着重讨论“实际”应用,我们到目前为止所学会的技巧和经验都将得到应用,帮助我们方便地稳定一个复杂的电路。

我们将设计一个通用单电源缓冲放大器(将2.1V 缓冲至4.1V参考),5V单电源供电使它能够线性地工作,可提供较大的输出电流(>13mA),并在 -40°C 至 +125°C工作温度范围的飘移为0.4V。

虽然可将该电路用于许多应用中,但我们仍将简要介绍一下促使给出这个设计的原因,并解释为何没有现成的电路可用来完成此项工作。

我们这里采用综合技术来开发器件网络,以提供一个证明对许多运放应用都有益的稳定电路。

技术背景:在实际应用中,惠斯通电桥的一个常见应用就是压力测量。

如图 5.1所示,随着所加压力变化,很多这种压力传感器都具有明显的二阶非线性特性。

图5.1 典型实际传感器输出比所加压力图字(上、下):室温下电桥输出与压力关系、理想传感器、实际传感器;坐标轴字: X轴:压力、Y轴:Vexc=1V时的电桥输出(V/V或Vbridge)除了随所加压力变化而产生的非线性外,许多压力传感器随温度变化在偏移量和范围上也有非线性特性。

用来校正这些误差的一种现代解决方法是在压力传感器中内置电子电路,然后将电子电路与压力传感器作为一个模块,随着温度的变化进行数字校准。

一种适用于此类用途的IC是由德州仪器公司提供的Burr-Brown产品PGA309(如图 5.2所示)。

此输出电压已经过数字校准的传感器,其信号调整IC包含有一个模拟传感器线性化电路,该电路将输出电压的一部分反馈至传感器的电压激励引脚,从而以20:1的改良比例对二阶非线性进行线性化。

因此,V EXC引脚将随传感器所加压力的变化而对其电压进行调整。

此电路的一个局限就是其传感器激励引脚V EXC,在工作温度范围内限制在5mA最大输出电流上。

2.1 CMOS模拟集成电路基本单元2.1.1 MOS场效应管的基本结构绝缘栅场效应管又叫作MOS场效应管,意为金属-氧化物-半导体场效应管。

图2.1为MOS场效应管的结构和电路符号。

图中的N型硅衬底是杂质浓度低的N型硅薄片。

在它上面再制作两个相距很近的P区,分别引为漏极和源极,而由金属铝构成的栅极则是通过二氧化硅绝缘层与N型衬底及P型区隔离。

这也是绝缘栅MOS场效应管名称的由来。

因为栅极与其它电极隔离,所以栅极是利用感应电荷的多少来改变导电沟道去控制漏源电流的。

MOS场效应管的导电沟道由半导体表面场效应形成。

栅极加有负电压,而N型衬底加有正电压。

由于铝栅极和N型衬底间电场的作用,使绝缘层下面的N型衬底表面的电子被排斥,而带正电的空穴被吸引到表面上来。

于是在N型衬底的表面薄层形成空穴型号的P型层,称为反型层,它把漏源两极的P区连接起来,构成漏源间的导电沟道。

沟道的宽窄由电场强弱控制。

MOS场效应管的栅极与源极绝缘,基本不存在栅极电流,输入电阻非常高。

[20,21]图2.1MOS场效应管的结构和电路符号Fig.2.1 Structure and circuit symbol that MOS Field-Effect Transistor 场效应管有P型和N型之分。

这里的P型或N型,指的是导电沟道是P型还是N 型,即导电沟道中是空穴导电还是电子导电。

因为场效应管中只有一种载流子参加导电,所以又常称为“单极型晶体管”。

P型沟道和N型沟道的MOS场效应管又各分为“耗尽型”和“增强型”两种。

耗尽型指栅极电压为零时,就存在导电沟道,漏源中间有一定电流。

增强型MOS场效应管,则只有在栅极电压大于零的情况下,才存在导电沟道。

2.1.2 MOS场效应管的模型化MOS管的大信号(直流)特性可以用它的电流方程来描述。

以N沟道增强型MOS管为例,特性曲线和电流方程如图2.2所示。

图2.2 特性曲线和电流方程Fig.2.2 Characteristic property curve and electric current equation如果栅源偏置电压GS V 大于MOS 管的阈值电压T V ,则在P 型衬底的表面由于静电感应会产生大量的电子,形成导电沟道。

利用Pspice分析放大器环路的稳

虽然在较低频率下可以较轻松地检查一个简单放大器的稳定性,但评估一个较为复杂的电路是否稳定,难度可能会大得多。

本文使用常见的Pspice宏模型结合一些简单的电路设计技巧来提高设计工程师的设计能力,

以确保其设计的实用性与稳定性。

导致放大器不稳定的原因

在任何相关频率下,只要环路增益不转变为正反馈,则闭环系统稳定。

环路增益是一个相量,因而具有幅度和相位特性。

环路由理想的负反馈转变

为正反馈所带来的额外相移即是最常见的不稳定因素。

环路增益相位的相关

频率,一般出现在环路增益大于或等于0dB之处。

运放稳定性第1部分(共15部分):环路稳定性基础作者:Tim Green ,TI 公司Burr-Brown 产品战略发展经理1.0 引言本系列所采用的所有技术都将“以实例来定义”,而不管它在其他应用中能否用普通公式来表达。

为便于进行稳定性分析,我们在工具箱中使用了多种工具,包括数据资料信息、技巧、经验、SPICE 仿真以及真实世界测试等,都将用来加快我们的稳定运放电路设计。

尽管很多技术都适用于电压反馈运放,但上述这些工具尤其适用于统一增益带宽小于20MHz 的电压反馈运放。

选择增益带宽小于20MHz 的原因是,随着运放带宽的增加,电路中的其他一些主要因素会形成回路,如印制板 (PCB) 上的寄生电容、电容中的寄生电感以及电阻中的寄生电容与电感等。

我们下面介绍的大多数经验与技术并非仅仅是理论上的,而且是从利用增益带宽小于20MHz 的运放、实际设计并构建真实世界电路中得来的。

本系列的第1部分回顾了进行稳定性分析所需的一些基本知识,并定义了将在整个系列中使用的一些术语。

9Data Sheet Info 9Tricks 9Rules-Of-Thumb 9Tina SPICE Simulation9TestingGoal:EASILY Tricks & Rules-Of-Thumb apply for Voltage FeedbackOp Amps, Unity Gain Bandwidth <20MHzTo learn how to analyze and design Op Amp circuits for guaranteed Loop Stability using Data Sheet Info, Tricks, Rules-Of-Thumb, Tina SPICE Simulation, and Testing.Note:图1.0 稳定性分析工具箱图字(上、下):数据资料信息、技巧、经验、Tina SPICE 仿真、测试;目的:学习如何用数据资料信息、技巧、经验法则、Tina SPICE 仿真及测试来“更容易地”分析和设计运放,以确保环路稳定性;注:用于统一增益带宽小于20MHz 的电压反馈运放的技巧与经验法则。

工程师设计运算放大器时,经常使用SPICE仿真来检查所设计电路的稳定性。

SPICE仿真在高速放大器应用中尤为常用,因为微小的电容和电感都很容易影响电路的稳定性。

稳定性分析的典型方法是在反馈回路中插入交流断点,以便使用交流分析测量环路增益(Aol×β)响应,该方法几乎适用于所有SPICE仿真器。

不过,反馈网络插入断点的具体位置,可能会对仿真的准确性产生较大的影响。

本文将利用OPA607运算放大器,阐释工程师在反馈网络中最常用的两个插入位置的优缺点。

方法一:在输出端断开循环该稳定性分析方法中,断开了放大器输出端的反馈回路。

这是一种相当简单和流行的方法。

图1显示了这种方法的典型示例。

图1:稳定性仿真电路在输出端断开回路。

本文资料来源:德州仪器运算放大器非常有效地展示了两种方法之间的差异;让我们来探讨一下原因。

在图1的电路中,环路在输出端使用1TH电感器断开。

重要的是要使用一只非常大的电感器来断开回路,而不是直接完全断开连接,这样仿真仍然可以计算用于分析的直流工作点,但对于交流仿真来说似乎是开路。

如果没有电感器,仿真可能无法找到用于仿真的工作点,或者会找到一个不准确的工作点,无法由于环路在输出端断开,而输入端连接到反馈网络的输出端,从输入源到放大器输出端的传递函数,将等于反馈因子(β)乘以放大器的开环增益(Aol),通常称为环路增益。

然后,为了获得相位裕度,可以运行AC仿真,并评估幅度为0dB以上时的环路增益相位。

图2所示为10MHz到100MHz的稳定性仿真结果,相位裕度约为82度。

图2:使用方法一获得的稳定性仿真结果。

方法二:在反相节点断开回路出了输出端断开反馈网络的另一个合乎逻辑的位置是放大器的反相输入。

图3显示了类似于图1的稳定性仿真示例电路,但断开环路的位置是放大器的输入端,而不是输出端。

图3:稳定性仿真电路在输入端断开回路。

在图3的电路中,注意添加到电路反馈回路的两个额外电容器(Ccm和Cdiff)。

运放稳定性21 23运放稳定性21-23现在,我们必须测量如图10.6所示的zo(小信号ac开环输出阻抗)。

该tinaspice测试电路将测试空载opa177的zo。

r2和r1以及lt为低通滤波器函数提供了一条ac通道,这样,使得我们能将dc短路和ac开路一起并入反馈电路。

dc工作点在输出端显示为接近零伏,这也就是说,opa177没有电流流入或流出。

此时,通过运用1apkac电流生成器(我们能够扫视10mhz至1mhz的ac频率范围),zo的测量工作就可以轻松完成。

最后,得出测量结果zo=vout(如果将测量结果的单位从db转换为线性或对数,那么vout也将为以欧姆为单位的zo)。

图10.6短程zo测试电路:发射极追随器从图10.7中,我们可以看出,opa177zo是双极发射极跟随器输出级所独有的特征,而且这种输出级的ro在opa177单位增益带宽之内,是控制输出阻抗的专门组件。

opa177的ro为60欧姆。

图10.7开环输出阻抗:发射极追随器图10.8zo外部模型:发射极跟随器为了并使1/β分析的情况包含在zo与riso、cl、cf以及rf之间相互作用的影响结果内,我们需将zo从运算放大器的宏模型中分离出来,以便于弄清楚电路中所须要的节点。

这种构想例如图10.8右图。

u1将提供更多了产品说明书中的aol曲线,并从riso、cl、cf以及rf的各种影响中获得缓冲器。

图10.9zo外部模型详图:发射极跟随器通过例如图10.9右图的zo外部模型,我们能测量zo与riso、cl、rf以及cf之间相互作用对1/β的影响。

在zo外部模型中,设置ro=roopa177,实际测量值60欧姆。

压控电压源vcv1将运算放大器宏模型u1从ro、riso、cl、cf以及rf中隔绝开去。

将vcv1设置为x1,以保证产品说明书中的aol增益维持不变。

由于我们必须在稳定性状况最糟的情况下(只存有cl以及我们排序得出结论的短程zo[此时ro=60欧姆])分析这种电路,因此,务必确定各种小的dc功率。

多级运算放大器的频率补偿分析Bo yang 2009-5-3 由于单级运算放大器cascode不能满足低电压的要求,而且短沟道效应和深亚微米CMOS的本征增益下降,所以要使用多级放大,这样就涉及到频率补偿的问题。

大部分的频率补偿拓扑结构都是采用极点分离和零极点抵消技术(使用电容和电阻)。

对于两级运算放大器而言这样的补偿无论是在理论分析还是在实际电路中都是可行的,但是对于多级放大器而言,要考虑的因素很多(电容面积,功耗,压摆率等)。

而且理论的分析不一定都适用于实际的电路。

所以对于多级放大器的频率补偿,这里给出了几种拓扑结构。

由于系统结构,传输函数都很复杂,所以在分析这些拓扑结构之前先给出一些假设条件:1):假设每一级的增益都远远大于1;2):假设负载电容和补偿电容都大于寄生集总电容;3):每一级之间的寄生电容忽略不计。

以上这些假设都是很容易满足,而且在大部分电路中都是满足这些条件条件的。

一single stage对于单级放大器而言,其频率响应比较好,只有一个左半平面得极点,没有零点,所以整个系统是稳定的。

极点位置为:。

其增益带宽积为GBW=gmL/CL.所以可以通过增大跨导,减小输出电容的方式来增大带宽。

实际上它的相位裕度没有90度,是因为存在着寄生的零极点。

二这些寄生的零极点于信号路径上的偏置电流和器件的尺寸有关,所以单位增益带宽也不能无限制的增加,而是等于寄生最小极点或者零点的一半为比较合适的,而且大的偏置电流和小的器件尺寸对于稳定性是必要的二 two stage对于两级的运放,就是采用简单的米勒补偿(SMC)。

其补偿的结构如下所示:对于这种结构的传递函数可以表述如下从传递函数中很容易知道零极点位置。

其中一个右半平面得零点和两个极点。

为了保证系统稳定性,次极点和零点要在比单位增益频率大的地方,这样就要求Cm很大并把主极点推的很低,这样增益带宽积就要减小,要保持同样的速度即单位增益带宽,就要求大的功耗(增加跨导)通常选择次极点在单位增益频率两倍的位置。

运放稳定性之二:运放网络,SPICE分析作者:Tim Green,TI公司2.0 引言本系列第2部分将着重分析运放电路(尤其是两种常见运放网络)的稳定性。

重要的是必须在进行SPICE仿真前先进行1阶分析(主要用您的经验来进行人工分析)。

请记住,如果您不掌握仿真前看到的东西,则电路仿真程序将导致GIGO ("垃圾进垃圾出")。

我们将用SPICE环路增益测试法来进行,以便绘制Aol曲线、1/ 曲线及环路增益曲线的波特图。

另外,我们还将采用易于构建的运放交流SPICE模型,以便对任何运放电路的交流稳定性进行快速分析。

在本系列中,我们将采用称为TINA的通用SPICE仿真软件来分析运放电路的稳定性并给出相应的结果。

通常将此软件称为Tina SPICE,您可以在 上找到它的各种版本。

尽管所给出的一些SPICE技巧是针对TINA的,但您也会发现,您采用的其他SPICE软件也可从这些技巧中获益。

2.1 SPICE环路增益测试图2.0为SPICE环路增益测试的详细示意图。

LT提供一个直流闭环电路,因为每一个交流SPICE分析都要求有一个直流SPICE分析。

在进行交流SPICE分析时,随着频率增加,CT将逐渐变成短路而LT将逐渐变成开路,因此,可用一个SPICE 程序来运行所有有关运放交流稳定性的信息。

利用图2.0给出的公式,很容易从SPICE后处理上得到运放Aol、环路增益以及1/β幅度与相位曲线。

尽管有其他一些方法可用来"打破环路"并用SPICE来进行交流分析,但图2.0所示方法证明是一种误差最小以及在SPICE中造成数学差别最小的方法。

2.2 运放网络与1/β图2.1给出了两种常见的运放网络--ZI 与ZF。

我们将首先单独对这两种网络进行1阶分析,如果与我们的预测结果一致,则再用Tina SPICE来对运放电路进行仿真与验证。

1阶分析的关键是采用我们在本系列第1部分中介绍的直观器件模型与少许直觉。

2.2 ZF运放网络让我们先对图2.2所示ZF网络进行1阶分析。

这是一个运放电路中的反馈网络,其中Cp在低频上为开路,且低频1/β变成如图所示的简单RF/RI。

而在其他极端频率上(例如高频),Cp为短路且高频1/β变成(Rp//RF)/RI。

但当Cp短路时,由于Rp<<RF,故Rp应在反馈电阻中占优势,因此我们将高频增益近似为Rp/RI。

请注意,由于在运放反馈路径中有一个电抗元件--电容,因此我们知道在传输函数中的某处必定有几个极点和/或零点。

在Cp量值与并联阻抗量值相匹配的频率上(这里RF占优势),我们可以预计在1/β曲线上会有一个极点。

反馈电阻将变小,因此VOUT必定开始减小。

现在,在Cp量值与串联电阻Rp量值相匹配的频率上,我们预计会有一个零点,因为随着Cp接近短路,净反馈电阻将不再变小,而VOUT则会随频率的增加而变得平坦。

因此通过1阶分析我们可以预测出现极点与零点位置以及低频与高频1/β幅度。

为验证1阶分析,我们用Tina SPICE构造的ZF分析电路示于图2.3中。

VIN设置为直流0V,交流源选项则选择为将交流幅度设置为1。

我们的交流分析设置成从10Hz至10MHz,并要求保留100个数据点与幅度/相位数据点用于后处理。

为进行"SPICE环路增益测试",我们采用了带方便电压检测点(N1、N2及N3)的L1、C1 与 VIN。

从此电路上,我们可看出:Aol = N2/N1及1/Beta = N3/ N1。

Tina SPICE 仿真的"默认结果"如图2.4所示。

没有像我们感兴趣的ZF 1/Beta 曲线与运放Aol曲线那么有用。

因此为获得所期望的曲线,我们将执行如图2.5所示的"后处理计算"。

用户自定义函数Aol被指定为计算公式N2/N1(用于Aol曲线),而Beta1(只所以采用这个代号是因为Tina SPICE中不认1/Beta)则被指定为计算公式N3/N1(用于1/Beta曲线)。

现在我们得出如图2.6所示用于Aol 及Beta1的计算结果。

通过在右击我们不再需要的幅度与相位图中的每一个波形(例如N1、N2及N3),我们能清除所得到的曲线窗口并删除这些不需要的波形。

经过这种清理后,再右击每一条曲线的Y轴并选择"默认范围"。

到目前为止,除我们的曲线不熟悉以及没有使其容易看到20db/decade幅度斜线及45 /decade相位斜线的刻度外,一切都很好。

击x轴并选择"属性",将弹出一个窗口。

现在选择用于定标的正确"滴答"数的奥秘是计算所绘出的频率范围种的十倍频程数并加1。

如上所述,对于10Hz -10MHz 的频率范围,有6个十倍频程(亦即:10 至100、100至1k、1k至10k、10k 至100k、100k至1M以及1M 至10M)。

现在频率轴看起来就像是我们熟悉的半对数曲线。

现在,我们希望对幅度曲线的y轴进行再定标,以获得更加熟悉的20dB/格刻度。

我们的"增益再定标"技巧如图2.8所示。

右击y轴并选择"属性",将弹出一个窗口。

现在选择用于定标的适当"滴答"数的奥秘是,先将"下极限"设置为最近,即使增加20dB也小于所示的默认"下极限"。

然后再将"上极限"设置为最近,即使增加20dB也大于所示的默认"上极限"。

从新的"下极限"上减去新的"上极限"并除以20。

将结果加1,我们即算出了获得我们熟悉的20dB/格y轴定标所需的适当"滴答"数。

此外,为便于对相位曲线读数,我们将y轴再定标为更为熟悉的45 /格刻度。

我们的"相位再定标"技巧如图2.9所示。

右击y轴并选择"属性",将弹出一个窗口。

现在选择用于定标的适当"滴答"数的奥秘是,先将"下极限"设置为最近,即使增加45 也小于所示的默认"下极限"。

然后再将"上极限"设置为最近,即使增加45 也大于所示的默认"上极限"。

从新的"下极限"上减去新的"上极限"并除以45。

将结果加1,我们即算出了获得我们熟悉的45 /格y轴定标所需的适当"滴答"数。

ZF最佳定标Tina SPICE仿真结果示于图2.10。

紫线表示我们的1阶分析预测。

游标设置成偏离低频1/Beta -3dB处与偏离高频1/Beta +3dB处的精确幅度差。

1阶分析结果与预测虽然不精确,但肯定优于强大及直观的交流稳定性分析结果。

2.2 运放网络ZI让我们先对图2.11所示ZI网络进行1阶分析。

这是一个运放电路中的输入网络,其中Cn在低频上为开路,且低频1/β变成如图所示的简单RF/RI。

而在其他极端频率上(例如高频),Cn为短路且高频1/β变成(RF//RI)/Rn。

但当Cp短路时,由于Rn<<RI,故Rn应在输入电阻中占优势,因此我们将高频增益近似为RF/Rn。

请注意,由于在运放输入路径中有一个电抗元件--电容,因此我们知道在传输函数中的某处必定有几个极点和/或零点。

在Cn量值与并联阻抗量值相匹配的频率上(这里RI占优势),我们可以预计在1/β曲线上会有一个零点。

输入电阻将变小,故VOUT开始增加。

现在,在Cn量值与串联电阻Rn量值相匹配的频率上,我们预计会有一个极点,因为随着Cn接近短路,净输入电阻将不再变小,而VOUT 则会随频率的增加而变得平坦。

因此通过1阶分析,我们可以预计出现极点与零1/β幅度。

点位置以及低频与高频为验证1阶分析,我们用Tina SPICE构造的ZI分析电路示于图2.12中。

VIN 设置为直流0V,交流源选项则选择为将交流幅度设置为1。

我们的交流分析设置成从10Hz至10MHz,并要求保留100个数据点与幅度/相位数据点用于后处理。

为进行"SPICE环路增益测试",我们采用了带方便电压检测点(N1、N2及N3)的L1、C1 与 VIN。

从此电路上我们可看出:Aol = N2/N1及1/Beta = N3/ N1。

ZI最佳定标Tina SPICE仿真结果示于图2.13。

紫线表示我们的1阶分析预测。

游标设置为偏离低频1/Beta +3dB处与偏离高频1/Beta -3dB处的精确幅度差。

1阶分析结果与预测虽不精确,但肯定优于功能强大及直观的交流稳定性分析结果。

2.3 简单运放交流SPICE 模型正如我们所看到的,SPICE 可以是一种用来检查1阶分析的强大分析工具。

但对于交流稳定性分析,它要求我们用运放模型来构建电路。

有时我们没有SPICE 模型,但却拥有我们准备使用的运放数据资料。

例如,假设我们没有OPA364(单电源、RRIO 及CMOS 运放,由德州仪器公司提供的Burr-Brown 产品)的运放模型。

其数据资料给出的开环增益与相位曲线如图2.14所示。

CMOS 运放的共同特点是,低频开环幅度与负载无关。

这就是上面给出的默认10k?与100k? 负载例子。

从该曲线的相位部分,我们用"对数定标技术"(参见本系列第1部分)可确定-45 处于的频率为29Hz。

OPA364的统一增益带宽在7.4MHz 频率上测得。

我们首先用双极点方法来制定一个简单运放交流模型。

我们将在相位下降为-135 的频率上设置第二个极点fp1。

图2.15为OPA364的简单运放交流SPICE 模型。

关键频率器件为用来形成fp0 与 fp1的元件。

请注意,压控电压源VCV1、VCV2及VCV3在频率元件之间提供完美的缓冲,并防止它们互相作用或加载。

其他重要元件是RO。

RO 为运放交流小信号、开环输出阻抗。

我们将在本系列的第3部分详细对其进行详细研究--我们将讨论如何从厂商提供的数据资料或通过测量来获得RO。

对于我们目前的讨论,我们将给此OPA364交流模型的RO 分配一个160 的值。

此模型将在SPICE 快速运行,且如果我们主要关心的是获得一种稳定性良好的设计,则它能为我们提供所需的一切。

图2.15还显示,我们通过带方便电压检测点(VM、VOA 及VOUT)的LT、CT 及VIN 来使用"SPICE 环路增益测试"。

从该电路我们可看出Aol = VOA/VM。

简单运放交流SPICE模型的最佳定标Tina SPICE仿真结果示于图2.16中。