波形采集储存与回放系统毕业论文

- 格式:doc

- 大小:458.50 KB

- 文档页数:61

波形采集、存储与回放系统的设计作者:钟秀娟来源:《软件工程师》2013年第10期摘要:本系统利用MSP430F149单片机控制,可以同时采集单极性和双极性两路周期信号,并存储到FLASH存储器,系统断电重启后,能连续回放已采集的信号,同时测量信号周期和电平并显示。

本设计主要有输入电路模块、信号放大处理模块、单片机控制电路模块、D/A转换模块和输出模块等组成。

本系统特点是功耗低,高输入阻抗,低输出阻抗,回放信号与原信号误差小,能显示信号周期和高低电平。

关键词:MSP430F149单片机;A/D转换器;D/A7524转换器中图分类号:TP274.2 文献标识码:A1 总体方案设计及框图本系统主要由输入电路(集成运放和整形电路)部分、A/D转换电路模块、单片机及显示电路模块、D/A转换(DA7524转换电路)和输出电路模块[1]。

输入信号经电平移位电路,经A/D转换后存入储存器并实时显示,回放时经D/A转换,显示在示波器上。

具体框图如图1所示。

2 电路的设计与流程图设计(1)采样信号处理通过电阻分压方式实现电压的零点偏置,将电压整体抬高。

电阻分压方式具有结构简单,成本低的优点,且允许幅值较大的双极性模拟信号在板内传输,在外界干扰一定的时候,提高了信噪比[2]。

对于MSP430F149内部的积分型ADC而言,电阻分压方式的输入阻抗较大,为保证片内电容的充电时间,以达到应有的测量精度,需相应延长采样的时间。

(2)输入电路的设计由于MSP430F149内置的模数转换器(ADC)只能对低于3.3V的电压采样,而系统要求能完成对A通道高电平约4V,低电平接近0V信号的采样,所以系统在输入部分设计了一个同相比例运放电路,将输入信号衰减一倍,使之达到单片机对电压的采样要求。

(3)整形电路频率测量时,利用MSP430F149单片机捕获输入信号上升沿,计算两个上升沿之间的时间差,即信号的周期。

但设计的电路是正弦信号,有上升沿,不能达到电路的测量要求,所以本系统设计了一个整形电路,将正弦波信号转换为同频率的方波信号输出,以使单片机能准确捕捉到每一个上升沿信号。

数字化语音存储与回放系统设计摘要本文介绍了一种以单片机为核心控制单元的数字化语音存储与回放系统的组成以及系统软硬件的设计。

该系统的基本原理是对语音信号的录制和回放的数字化控制。

该系统以AT89C52单片机为微处理器,实现对系统的控制以及数据的处理。

系统采用闪存28F512作为外部数据存储器来存放语音数据,以满足能够较长时间存储语音信息。

语音采集部分采用ADC0809进行模数转换,语音回放部分采用DAC0832实现数模转换,并通过键盘等接口电路实现人机交互,单片机工作在中断查询模式,能够快速响应按键要求,以控制信号的采集、存储和回放等。

同时,外围电路辅以带通滤波器和增益、功率放大等电路对信号进行滤波放大,以保证信息的高质量存储与回放。

关键词:数字化存储,回放,数字滤波,采样,模/数转换目录1绪论 (1)1.1课题背景 (1)1.2课题研究的意义 (1)1.3数字化处理的前景 (1)1.4课题任务要求 (2)1.5本文的主要内容 (3)2系统总体方案设计 (4)3硬件部分设计 (7)3.1拾音器 (7)3.2放大器的设计 (7)3.2.1前置增益放大器 (7)3.2.2输出功率放大器 (8)3.3滤波器设计 (9)3.4单片机选型 (12)3.4.1AT89C52介绍 (12)3.4.2引脚简介 (13)3.4.3主要功能及其特性 (14)3.4.4中断 (14)3.5采样保持电路 (15)3.6 D/A转换器DAC0832 (15)3.6.1DAC0832内部结构及引脚 (16)3.6.2 DAC0832工作方式 (16)3.7 A/D转换电路设计 (18)3.7.1 A/ D转换的常用方法 (18)3.7.2 ADC0809的主要特性和结构 (18)3.7.3 ADC0809管脚功能及定义 (19)3.7.4 ADC0809工作方式 (20)3.8键盘电路 (22)3.9存储器的选取 (23)4软件设计 (26)4.1编程工具软件Keil C51 (26)4.2 Protrus软件设计 (26)4.3软件程序的设计 (27)4.3.1程序总体流程图 (27)4.3.2子程序设计 (28)4.3.3系统仿真 (30)5结论 (32)6致谢 (33)参考文献 (34)附录 (36)外文资料 (41)外文翻译 (48)1绪论1.1课题背景语音信号处理是信息科学的一个重要分支,伴随着大规模集成技术的高度发展以及计算机技术的飞速前进,推动了语音信号处理技术的快速发展。

收稿日期:2012-01作者简介:李德尧(1966—),男,副教授,研究方向为自动控制技术。

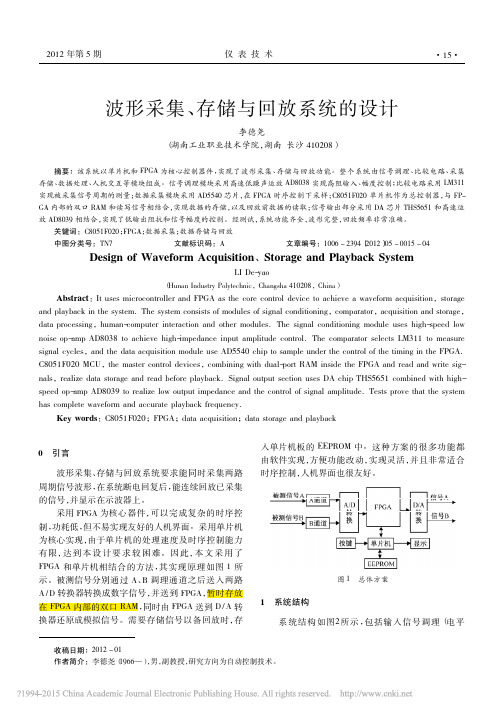

波形采集、存储与回放系统的设计李德尧(湖南工业职业技术学院,湖南长沙410208)摘要:该系统以单片机和FPGA 为核心控制器件,实现了波形采集、存储与回放功能。

整个系统由信号调理、比较电路、采集存储、数据处理、人机交互等模块组成。

信号调理模块采用高速低躁声运放AD8038实现高阻输入、幅度控制;比较电路采用LM311实现被采集信号周期的测量;数据采集模块采用AD5540芯片,在FPGA 时序控制下采样;C8051F020单片机作为总控制器,与FP-GA 内部的双口RAM 和读写信号相结合,实现数据的存储,以及回放前数据的读取;信号输出部分采用DA 芯片THS5651和高速运放AD8039相结合,实现了低输出阻抗和信号幅度的控制。

经测试,系统功能齐全,波形完整,回放频率非常准确。

关键词:C8051F020;FPGA ;数据采集;数据存储与回放中图分类号:TN7文献标识码:A文章编号:1006-2394(2012)05-0015-04Design of Waveform Acquisition 、Storage and Playback SystemLI De-yao(Hunan Industry Polytechnic ,Changsha 410208,China )Abstract :It uses microcontroller and FPGA as the core control device to achieve a waveform acquisition ,storage and playback in the system.The system consists of modules of signal conditioning ,comparator ,acquisition and storage ,data processing ,human-computer interaction and other modules.The signal conditioning module uses high-speed low noise op-amp AD8038to achieve high-impedance input amplitude control.The comparator selects LM311to measure signal cycles ,and the data acquisition module use AD5540chip to sample under the control of the timing in the FPGA.C8051F020MCU ,the master control devices ,combining with dual-port RAM inside the FPGA and read and write sig-nals ,realize data storage and read before playback.Signal output section uses DA chip THS5651combined with high-speed op-amp AD8039to realize low output impedance and the control of signal amplitude.Tests prove that the system has complete waveform and accurate playback frequency.Key words :C8051F020;FPGA ;data acquisition ;data storage and playback0引言波形采集、存储与回放系统要求能同时采集两路周期信号波形,在系统断电回复后,能连续回放已采集的信号,并显示在示波器上。

波形采集、存储与回放系统的设计钟秀娟【期刊名称】《软件工程师》【年(卷),期】2013(000)010【摘要】This system uses MSP430F149 MCU control, can simultaneously capture two unipolar and bipolar periodic signal, and stored in FLASH memory, the system is rebooted, continuous playback of the acquired signal, the signal cycle and level measurement and display. This design has an input circuit module, a signal amplification processing module, the MCU control circuit module, D/A converter and output modules and other components. The system is characterized by low power consumption, high input impedance, low output impedance, the playback signal with the original signal error is small, can display signal cycles and high and low.%本系统利用MSP430F149单片机控制,可以同时采集单极性和双极性两路周期信号,并存储到FLASH存储器,系统断电重启后,能连续回放已采集的信号,同时测量信号周期和电平并显示。

本设计主要有输入电路模块、信号放大处理模块、单片机控制电路模块、D/A转换模块和输出模块等组成。

怀化学院本科毕业论文(设计)任务书论文题目波形采集、存储与回放系统(硬件设计)学生姓名黄津毅系别物理与信息工程系专业电子信息科学与技术指导老师姓名张仁民职称讲师题目来源1.科学技术□ 2.生产实践□ 3.社会经济□4.自拟□ 5.其他√毕业论文(设计)内容要求:设计并制作一个波形采集、存储与回放系统,示意图如图1所示。

该系统能同时采集两周期信号波形,要求系统断电恢复后,能连续回放已采集的信号,显示在示波器上。

图1 系统示意图主要参考资料:[1] 马明建,周长城.数据采集于处理技术.第二版.西安:西安电子科技大学出版社,2005.[2] 周浩敏.信号处理技术基础.第一版.北京:北京航空航天大学出版社,2001.[3] PICMG 2.0 R3.0 CompactPCI Specification October 1,1999.[4] 杨跃江.3U_导冷VPX信号采集、处理系统解决方案.深圳:研祥智能科技股份有限公司,2011.[5] Xilinx 7 Series FPGAS : Breakthrough Power and Performance, Dramatically Reduceddevelopment Time毕业论文(设计)工作计划:进度安排工作内容2011年10月15日-2011年11月25日文献资料查阅2011年11月26日-2012年01月15日方案论证与系统方案仿真2012年01月16日-2012年02月16日硬件电路的设计2012年02月17日-2012年03月20日单元模块电路调试2012年03月21日-2012年05月10日联调与毕业论文的撰写接收任务日期2012 年10月15日要求完成任务日期2012 年05 月10日学生(签名)年月日指导教师(签名)年月日系主任(签名)年月日说明:本表为学生毕业论文(设计)指导性文件,由指导教师填写,一式两份,一份交系(部)存档备查,一份发给学生。

FPGA数据采集与回放系统设计论文FPGA数据采集与回放系统设计论文在个人成长的多个环节中,大家或多或少都会接触过论文吧,论文是我们对某个问题进行深入研究的文章。

怎么写论文才能避免踩雷呢?下面是小编为大家整理的FPGA数据采集与回放系统设计论文,欢迎阅读,希望大家能够喜欢。

1系统及其原理基于通用信号处理开发板,利用FPGA技术控制AD9233芯片对目标模拟信号采样,再将采样量化后的数据写入USB接口芯片CY7C68013的FIFO中,FIFO写满后采用自动触发工作方式将数据传输到PC机。

利用VC++6.0软件编写上位机实现友好的人机交互界面,将传输到PC机上的数据进行储存和实时回放。

本系统主要实现以下两大功能:1)ADC模块对目标模拟信号进行采样,利用FPGA技术将采样后的数据传输到USB接口芯片CY7C68013的FIFO中存储。

2)运用USB2.0总线数据传输技术,将雷达回波信号数据传输到PC 机实时回放。

分为应用层、内核层和物理层3部分。

应用层和内核层主要由软件实现。

应用层采用VC++6.0开发用户界面程序,为用户提供可视化操作界面。

内核层基于DriverWorks和DDK开发系统驱动程序,主要起应用软件与硬件之间的桥梁作用,把客户端的控制命令或数据流传到硬件中,同时把硬件传输过来的数据进行缓存。

物理层主要以FPGA为核心,对USB接口芯片CY7C68013进行控制,通过USB2.0总线实现对中频信号采集。

系统设计采用自底向上的方法,从硬件设计开始逐步到最终的应用软件的设计。

2硬件设计FPGA在触发信号下,控制ADC采样输入信号,并存入FIFO中。

当存满时,将数据写入USB接口芯片CY7C68013,同时切换另一块FIFO接收ADC转换的数据,实现乒乓存储,以提高效率。

FPGA模块的一个重要作用是控制USB接口芯片CY7C68013。

当ADC采样后,数据进入FPGA模块,FPGA控制数据流将其写入CY7C68013的FIFO中,以便于USB向PC机传输。

波形采集、存储与回放系统波形采集、存储与回放系统——武汉东湖学院陈鹏、费?、何凯摘要本设计以STM32F103ZET6作为控制芯片,把波形采集分为A、B 两个通道,对A通道的输入信号进行衰减,对B通道的输入信号进行放大,然后采用内部集成的高速AD对信号进行实时采样,方式为上升沿内触发,可以实现波形的单次和多次触发存储和回放显示,以及频率、周期、峰-峰值的测量和显示,并具有掉电存储功能。

整个系统操作简便,界面友好,达到了较好的性能指标。

关键字:STM32、波形采集、波形存储、波形回放一、系统方案1.1题目要求及相关指标分析题目的要求是将待测信号进行数字存储,并通过普通示波器将被测信号显示出来。

由于被测信号为模拟信号,存储过程为数字方式,故应该将模拟信号进行量化处理,然后存储到存储器中,当需要显示的时候,从存储器输出数据并恢复为模拟信号,然后送往普通示波器进行显示。

本设计的重点是模拟信号的处理与采样、数字信号的存储、系统的控制三个方面。

1.2系统设计与框图:系统整体设计框图如图1-1所示。

模拟信号通过信号调理模块(阻抗变换、固定衰减/放大、触发电路)将模拟信号的幅值大小调理到高速AD的输入范围0——3.3V。

同时,两路信号经比较器得到方波,送处理器STM32进行测频。

处理器测得输入信号频率后控制内部AD以输入信号频率的80倍速率采样。

在STM32内部增加波形存储控制模块,当满足触发条件时ARM对AD转换得到的数据进行存储。

图1-1系统整体设计图图1图1图1 A通道信号调理B通道信号调理存储、显示与控制STM32F103ZET6比较器比较器A通道信号调理输出B通道信号调理输出内部集成A\D 内部集成D\A 键盘显示二、理论分析与计算 2.1 A/D采样频率选择采用内部集成A/D,采样频率由输入信号的频率决定,在输入信号的一个周期内采集80个点,那么,通过式(2.1),可以求出采样频率,其中为信号频率。

基于单片机的波形采集、存储与回放系统设计作者:梁丽来源:《中国教育技术装备》2016年第18期摘要系统以单片机为核心,以低功耗运放构成输入输出电路,选用外部低功耗存储芯片作存储,软件系统控制外部A/D转换器实现对输入信号的采集、数据存储,并通过外部D/A 转换器实现对已采集信号的回放,系统的各种信息及采集波形信息由液晶显示输出。

关键词单片机;接口电路;波形采集中图分类号:G642 文献标识码:B文章编号:1671-489X(2016)18-0032-021 前言采用AT89C52单片机作为整个控制核心,通过软件编程实现对模拟信号的采集、存储数据的输出以及各种测量、逻辑控制的功能。

现从系统单元电路设计、单片机与外部设备的接口电路设计和系统软件设计的角度,阐述基于单片机的波形采集、存储与回放系统的设计思想。

2 单元电路设计通道调理电路将ADC0809转换器的基准电压输入端接至+5 V电源,它可对0~5 V的模拟信号进行转换。

A通道输入信号是单极性的,输入电压范围为0~4 V,符合A/D转换器对输入信号的要求。

A通道的输入、输出电路均选用电压跟随器,电压跟随器具有输出电压跟随输入电压、输入阻抗高、输出阻抗低的特点,使得整个通道的放大倍数为1。

B通道输入信号是双极性的,输入电压范围为-50~+50 mV。

为此,在B通道输入端需将信号电压由双极性转换为单极性,并调理为0~4 V 电压输出,以匹配A/D转换器的输入电压范围;在B通道输出端则需将信号电压的极性和幅度范围进行还原。

B通道输入电路如图1所示,它由三级运放构成:第一级运放构成电压跟随器;第二级运放构成反相比例电路,其交流放大倍数为-40,作用是将信号电压由-50~+50 mV 调理到+2~-2 V范围内;第三级运放构成反相求和电路,其交流放大倍数为-1,调节电位器给信号电压+2 V的电平平移,将双极性信号转换为单极性,即将信号电压由+2~-2 V调理到0~4 V范围内。

波形采集储存与回放系统毕业论文目录第一章方案设计与论证 (1)1.1要求 (1)1.1.1基本要求 (1)1.1.2发挥部分 (2)1.3方案论证 (2)1.3.3方案一 (2)1.3.4方案二 (2)1.3.5方案三 (3)第二章理论分析与计算 (4)2.1主芯片分析 (4)2.2 ADC12模块 (5)2.3扫描速度与采样频率的关系 (5)2.4信号采样技术的基本原理 (5)2.4.1实时采样 (5)2.4.2顺序采样 (6)2.4.3随机采样 (6)第三章系统设计与框图 (7)3.1输入输出电路 (8)3.1.1 A路输入 (8)3.1.2 A路输出 (8)3.1.3 B路输入 (9)3.1.4 B路输出 (9)3.2电源电路 (10)3.3 MSP430F1479最小系统 (10)3.4显示与控制模块 (11)3.5掉电保护电路控制 (12)第四章软件设计 (13)第五章系统测试 (14)5.1测试仪器 (14)5.2输入阻抗 (14)5.3测试方案 (14)5.3.1基本要求测试 (14)5.3.2发挥部分测试 (15)第六章实验结果分析与讨论 (16)6.1实验结果 (16)第七章结论及意义 (18)参考文献 (19)致谢 (20)附录 (21)第一章方案设计与论证设计并制作一个波形采集、存储与回放系统,示意图如图 1 所示。

该系统能同时采集两路周期信号波形,要求系统断电恢复后,能连续回放已采集的信号,显示在示波器上1.1要求1.1.1基本要求(1)能完成对 A 通道单极性信号(高电平约 4V、低电平接近 0V)、频率约 1kHz 信号的采集、存储与连续回放。

要求系统输入阻抗不小于10 k?,输出阻抗不大于1k?。

(2)采集、回放时能测量并显示信号的高电平、低电平和信号的周期。

原信号与回放信号电平之差的绝对值≤50 mV,周期之差的绝对值≤5%。

(3)系统功耗≤50mW,尽量降低系统功耗,系统不允许使用电池。

1.1.2发挥部分(1)增加 B 通道对双极性、电压峰峰值为 100mV、频率为 10Hz~10kHz 信号的采集。

可同时采集、存储与连续回放A、B两路信号,并分别测量和显示A、B两路信号的周期。

B通道原信号与回放信号幅度峰峰值之差的绝对值≤10 mV,周期之差的绝对值≤5%。

(2)A、B两路信号的周期不相同时,以两信号最小公倍周期连续回放信号。

(3)可以存储两次采集的信号,回放时用按键或开关选择显示指定的信号波形。

1.2题目要求及相关指标分析题目的要求是将待测信号进行数字存储,并通过普通示波器将被测信号显示出来。

由于等测信号为模拟信号,存储过程为数字方式,故应该将模拟信号进行量化处理,然后存储到存储器中,当需要显示的时候,从存储器读出数据并恢复为模拟信号,并送往普通示波器Y输入端,在X输入端加入相应的扫描信号,采有X-Y方式观察信号的波形。

因此,设计的重点是模拟信号的处理与采样、数字信号的存储、普通示波器的显示控制、系统的控制4个方面。

1.3方案论证1.3.3方案一以单片机89s51为系统核心,以外部AD、存储、DA等器件实现信号的采集、存储与回放功能,整个系统简单灵活,便于实现,但无法完成对高速信号的处理,而且功率消耗过大。

1.3.4方案二以带有IP核的FPGA/CPLD完成对信号的采集、存储、显示以及AD\DA转化等功能,由IP核实现人机交互及信号处理等功能。

该方案结构紧凑、可以实现复杂测量与控制只是操作过于繁琐、系统功耗也很大。

1.3.5方案三核心采用MSP430F149单片机,利用单片机部的12位高精度AD转换器实现对信号的采集,采用外挂AT24C512存储信号数据,并由D/A完成DA功能转换,配合相应的输入输出电路完成相应的电压转换,1602液晶显示输出相应的各项信息,整个电路需要的相应外围电路少,功耗低简洁易行经过以上各个方案的分析比较,次设计采用方案三第二章理论分析与计算题目的要求是将待测信号进行数字存储,并通过普通示波器将信号显示出来,由于被测信号为模拟信号,存储过程为数字方式,故应将模拟信号进行量化处理,然后存储到存储器中,当需要显示的时候,从存储器读出数据并回复成模拟信号,并送到普通示波器的Y输入端,在X输入端加上相应的扫描信号,采用x-y方式观察信号的波形。

因此,设计的重点是模拟信号的处理与采样,数字信号的存储、普通示波器的显示控制,系统的控制四方面2.1主芯片分析MSP430是TEAXS INSTRUMENTS(TI)生产的16位单片机的统称,该系列是一种RISC结构的16位单片机,其突出特点是功耗极低(在3V、1Mhz的工作方式下,电流消耗是250uA休眠方式只有0.1uA的电流);其次是他的部资源相当丰富全系列中总共包含以下模块:12-bit、8通道A\D转换,带3-10个单独的捕获、比较功能的定时器Timer-A和Timer-B,1-2路USART通信口,多至160段LED驱动,硬件乘法器,模拟信号比较器,FLL频率锁相环,2-3个时钟系统等等。

以上片资源,可以极大限度的简化本题的设计。

2.2ADC12模块MSP430单片机的ADC12模块是一个12位的A/D转换模块,具有高速度,通用性等特点。

它具有5大功能模块,都可以独立配置,即具有采样、保持的ADC 功能核;可控制的转换存储;可控制的参考电平发生器;可控制和选择的时钟;可控制的采样及转换时序电路。

ADC12的主要特点是最大的采样速度达到200Ksps:转换为12位精度,1位差分非线性,1位积分非线性:8个可配置的外部信号采集通道。

2.3扫描速度与采样频率的关系假设扫描速度为t s/div,每格点数为n采样频率为fs,则:fs=n/t,当t=20的时候,针对不同的扫描速度,可得到不同的采样频率。

在一定的情况下扫描速度的改变是通过改变采样频率来实现的。

对应10KHz的正弦波采样频率为200KHz时每周期可采集20个点,由采集值可以很好的恢复采集前的信号,按照系统结构,只需要2通道的A/D采样输入信号的最高频率为10KHz。

以MSP430D149为核心,外挂一个防掉电保护的EEPROM就可以完成系统设置的要求,系统功耗也能控制在要求之中。

2.4信号采样技术的基本原理采样分实时采样和非实时采样两种。

从一个信号波形中取得所需样点称为实时采样。

从被测信号许多相邻波形上取得样点,以表示一个信号波形称为非实时采样,或者称为等效采样。

其实,对于非实时采样,还可以每隔10个、100个甚至更多个波形上取一个样点。

这样更有利于观测高速信号,当然这种高速信号必须是重复的。

2.4.1实时采样实时采样是数字信号采集技术的最直接应用。

在这种方法下,示波器根据一次触发事件连续的捕获被测量波形的n个采样数据,而后屏幕上显示波形的每个点都是在一次采样周期中获取的,它可以完成单次非重复信号的捕捉。

实时采样有三个重点特点:(1)示波器先将一段完整的波形数据存入存储器,然后再进行显示和分析。

(2)在触发事件前,示波器开始对信号进行连续采样。

(3)自动完成多信号的同时采样。

能够观测触发前信号的能力称为负触发延迟,它在故障分析中特别有用。

2.4.2顺序采样顺序采样是对每一个信号周期仅采样一个点,用步进延迟的方法,对每个周期信号波形的不同点进行采样,从而获取整个波形的采样数据2.4.3随机采样与顺序采样相对应,随机采样的采样脉冲是由一个独立电路产生,它和被测信号是不相关的。

因此,随机采样有三个特点:(4)样点在信号波形上的排列是随机的。

(5)可以观测到触发前的信号。

随机采样过程中样点在信号波形上的位置是无序的,即时随机的,但是在对这些样点进行屏幕显示时必须反映原波形的变化规律。

否则,测量将没有实用价值。

因此,在采样过程中应该同时记录各个采样点在信号波形上的相对位置。

第三章系统设计与框图系统整体设计框图如图所示。

模拟信号通过信号调理模块(阻抗变换、程控放大、触发电路),将模拟信号的幅值大小调理到高速AD(AD9225)的输入围0—4V。

然后通过AD9225对信号进性采样。

我们采用外部有源晶振作为高速AD的采样时钟来控制恒定的采样率4MHz(晶振的固有振荡频率),在FPGA部增加波形存储控制模块,当满足触发条件时FPGA以下抽样的方式对AD转换得到的数据进行存储,抽样频率由可水平分辩率来控制(若为AUTO功能,则与信号的频率有关)。

将抽样的数据分别存储到双口RAM中,在送入行列扫描电路(2片DAC0800)前经过了波形显示控制模块,它的作用是对RAM的数据及读入起始地址的进行处理。

从而实现波形在模拟示波器上的左右平移。

同时在FPGA部实现了512点的FFT计算,成功得分析了输入信号的频谱。

3.1输入输出电路3.1.1A路输入A路输入:系统要求A路输入信号为单极性(0-4V),而单片机设置A/D参考电平为2.5V,因此需要将输入信号变换为0-2.5V之,采集后在单片机部再做相应的运算处理,计算出相应的真正输入值,从而显示A路的最大值和最小值。

如图输入信号经过UIA同向跟随后,经R7做相应衰减送入单片机A/D进行采样,适当调节R7就可以进入A/D的值限幅在0-2.5V之3.1.2A路输出为保证回复A路信号(0-4V),故运放供电电压必须用5V供电,而D/A输出最高只能达到 2.5V,故该电路需要具有一定的放大功能,且要有一定的过滤作用。

这样才可以将D/A所产生的高频干扰滤除3.1.3B路输入系统要求D路输入信号为双极性(100mV VPP),因此需要将100mV放大至单片机A/D所所能判别的围,这样可以提高系统对B路信号的分辨率,同时需要将输入双极性信号转换为单极性信号,这样才能便于单片机识辨,图中VRF为1/2单片机A/D参考电压即1.25V,这样做的目的是给熟人信号加上一个1.25V 的片子电压之后再进行放大,如图输入信号经过U1B同向放大至0-2.5V后送给单片机A/D采样,适当调节R14即可改变放大器的放大倍数。

3.1.4B路输出为保证B路信号(100mV VPP),输出采用电容交流隔直,而D/A输出为输入信号经放大后采集到的信号,其VPP可达到2.5V,故用R38进行相应衰减,适当调整E38可以输出幅值与输入一致,U28为1:1同向放大,可将D/A所能产生的高频干扰滤波,C11可将单极性信号转为双极性信号,与输入保持一致。

3.2电源电路TPS78001将5V转为3.3V供给单片机工作,5V用于运放和液晶以及24C512工作。

3.3MSP430F1479最小系统单片机最小系统,或称为最小应用系统,是指用最少的元件组成的单片机可以工作的系统。

对于MSP430系列单片机来说,最小系统一般应该包括:单片机、晶振电路、复位电路。