半导体器件物理(第六章)_93140777

- 格式:pdf

- 大小:842.32 KB

- 文档页数:44

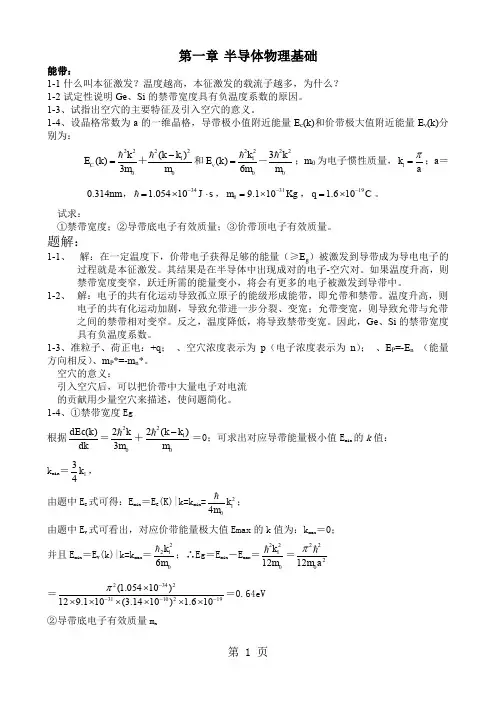

第一章 半导体物理基础能带:1-1什么叫本征激发?温度越高,本征激发的载流子越多,为什么?1-2试定性说明Ge 、Si 的禁带宽度具有负温度系数的原因。

1-3、试指出空穴的主要特征及引入空穴的意义。

1-4、设晶格常数为a 的一维晶格,导带极小值附近能量E c (k)和价带极大值附近能量E v (k)分别为:2222100()()3C k k k E k m m -=+和22221003()6v k k E k m m =-;m 0为电子惯性质量,1k a π=;a =0.314nm ,341.05410J s -=⨯⋅,3109.110m Kg -=⨯,191.610q C -=⨯。

试求:①禁带宽度;②导带底电子有效质量;③价带顶电子有效质量。

题解:1-1、 解:在一定温度下,价带电子获得足够的能量(≥E g )被激发到导带成为导电电子的过程就是本征激发。

其结果是在半导体中出现成对的电子-空穴对。

如果温度升高,则禁带宽度变窄,跃迁所需的能量变小,将会有更多的电子被激发到导带中。

1-2、 解:电子的共有化运动导致孤立原子的能级形成能带,即允带和禁带。

温度升高,则电子的共有化运动加剧,导致允带进一步分裂、变宽;允带变宽,则导致允带与允带之间的禁带相对变窄。

反之,温度降低,将导致禁带变宽。

因此,Ge 、Si 的禁带宽度具有负温度系数。

1-3、准粒子、荷正电:+q ; 、空穴浓度表示为p (电子浓度表示为n ); 、E P =-E n (能量方向相反)、m P *=-m n *。

空穴的意义:引入空穴后,可以把价带中大量电子对电流的贡献用少量空穴来描述,使问题简化。

1-4、①禁带宽度Eg 根据dk k dEc )(=2023k m +2102()k k m -=0;可求出对应导带能量极小值E min 的k 值: k min =143k , 由题中E C 式可得:E min =E C (K)|k=k min =2104k m ;由题中E V 式可看出,对应价带能量极大值Emax 的k 值为:k max =0;并且E min =E V (k)|k=k max =22106k m ;∴Eg =E min -E max =221012k m =222012m a π =23423110219(1.05410)129.110(3.1410) 1.610π----⨯⨯⨯⨯⨯⨯⨯=0.64eV②导带底电子有效质量m n2222200022833C d E dk m m m =+=;∴ 22023/8C n d E m m dk == ③价带顶电子有效质量m ’ 22206V d E dk m =-,∴2'2021/6V n d E m m dk ==- 掺杂:2-1、什么叫浅能级杂质?它们电离后有何特点?2-2、什么叫施主?什么叫施主电离?2-3、什么叫受主?什么叫受主电离?2-4、何谓杂质补偿?杂质补偿的意义何在?题解:2-1、解:浅能级杂质是指其杂质电离能远小于本征半导体的禁带宽度的杂质。

半导体器件物理教案课件PPT第一章:半导体物理基础知识1.1 半导体的基本概念介绍半导体的定义、特点和分类解释n型和p型半导体的概念1.2 能带理论介绍能带的概念和能带结构解释导带和价带的概念讲解半导体的导电机制第二章:半导体材料与制备2.1 半导体材料介绍常见的半导体材料,如硅、锗、砷化镓等解释半导体材料的制备方法,如拉晶、外延等2.2 半导体器件的制备工艺介绍半导体器件的制备工艺,如掺杂、氧化、光刻等解释各种制备工艺的作用和重要性第三章:半导体器件的基本原理3.1 晶体管的基本原理介绍晶体管的结构和工作原理解释n型和p型晶体管的概念讲解晶体管的导电特性3.2 半导体二极管的基本原理介绍半导体二极管的结构和工作原理解释PN结的概念和特性讲解二极管的导电特性第四章:半导体器件的特性与测量4.1 晶体管的特性介绍晶体管的主要参数,如电流放大倍数、截止电流等解释晶体管的转移特性、输出特性和开关特性4.2 半导体二极管的特性介绍半导体二极管的主要参数,如正向压降、反向漏电流等解释二极管的伏安特性、温度特性和频率特性第五章:半导体器件的应用5.1 晶体管的应用介绍晶体管在放大电路、开关电路和模拟电路中的应用解释晶体管在不同应用电路中的作用和性能要求5.2 半导体二极管的应用介绍半导体二极管在整流电路、滤波电路和稳压电路中的应用解释二极管在不同应用电路中的作用和性能要求第六章:场效应晶体管(FET)6.1 FET的基本结构和工作原理介绍FET的结构类型,包括MOSFET、JFET等解释FET的工作原理和导电机制讲解FET的输入阻抗和输出阻抗6.2 FET的特性介绍FET的主要参数,如饱和电流、跨导、漏极电流等解释FET的转移特性、输出特性和开关特性分析FET的静态和动态特性第七章:双极型晶体管(BJT)7.1 BJT的基本结构和工作原理介绍BJT的结构类型,包括NPN型和PNP型解释BJT的工作原理和导电机制讲解BJT的输入阻抗和输出阻抗7.2 BJT的特性介绍BJT的主要参数,如放大倍数、截止电流、饱和电流等解释BJT的转移特性、输出特性和开关特性分析BJT的静态和动态特性第八章:半导体存储器8.1 动态随机存储器(DRAM)介绍DRAM的基本结构和工作原理解释DRAM的存储原理和读写过程分析DRAM的性能特点和应用领域8.2 静态随机存储器(SRAM)介绍SRAM的基本结构和工作原理解释SRAM的存储原理和读写过程分析SRAM的性能特点和应用领域第九章:半导体集成电路9.1 集成电路的基本概念介绍集成电路的定义、分类和特点解释集成电路的制造工艺和封装方式9.2 集成电路的设计与应用介绍集成电路的设计方法和流程分析集成电路在电子设备中的应用和性能要求第十章:半导体器件的测试与故障诊断10.1 半导体器件的测试方法介绍半导体器件测试的基本原理和方法解释半导体器件测试仪器和测试电路10.2 半导体器件的故障诊断介绍半导体器件故障的类型和原因讲解半导体器件故障诊断的方法和步骤第十一章:功率半导体器件11.1 功率二极管和晶闸管介绍功率二极管和晶闸管的结构、原理和特性分析功率二极管和晶闸管在电力电子设备中的应用11.2 功率MOSFET和IGBT介绍功率MOSFET和IGBT的结构、原理和特性分析功率MOSFET和IGBT在电力电子设备中的应用第十二章:光电器件12.1 光电二极管和太阳能电池介绍光电二极管和太阳能电池的结构、原理和特性分析光电二极管和太阳能电池在光电子设备中的应用12.2 光电晶体管和光开关介绍光电晶体管和光开关的结构、原理和特性分析光电晶体管和光开关在光电子设备中的应用第十三章:半导体传感器13.1 温度传感器和压力传感器介绍温度传感器和压力传感器的结构、原理和特性分析温度传感器和压力传感器在电子测量中的应用13.2 光传感器和磁传感器介绍光传感器和磁传感器的结构、原理和特性分析光传感器和磁传感器在电子测量中的应用第十四章:半导体器件的可靠性14.1 半导体器件的可靠性基本概念介绍半导体器件可靠性的定义、指标和分类解释半导体器件可靠性的重要性14.2 半导体器件可靠性的影响因素分析半导体器件可靠性受材料、工艺、封装等因素的影响14.3 提高半导体器件可靠性的方法介绍提高半导体器件可靠性的设计和工艺措施第十五章:半导体器件的发展趋势15.1 纳米晶体管和新型存储器介绍纳米晶体管和新型存储器的研究进展和应用前景15.2 新型半导体材料和器件介绍石墨烯、碳纳米管等新型半导体材料和器件的研究进展和应用前景15.3 半导体器件技术的未来发展趋势分析半导体器件技术的未来发展趋势和挑战重点和难点解析重点:1. 半导体的基本概念、分类和特点。

半导体器件物理教案课件PPT第一章:半导体简介1.1 半导体的定义与特性1.2 半导体材料的分类与应用1.3 半导体的导电机制第二章:PN结与二极管2.1 PN结的形成与特性2.2 二极管的结构与工作原理2.3 二极管的应用电路第三章:晶体三极管3.1 晶体三极管的结构与类型3.2 晶体三极管的工作原理3.3 晶体三极管的特性参数与测试第四章:场效应晶体管4.1 场效应晶体管的结构与类型4.2 场效应晶体管的工作原理4.3 场效应晶体管的特性参数与测试第五章:集成电路5.1 集成电路的基本概念与分类5.2 集成电路的制造工艺5.3 常见集成电路的应用与实例分析第六章:半导体器件的测量与测试6.1 半导体器件测量基础6.2 半导体器件的主要测试方法6.3 测试仪器与测试电路第七章:晶体二极管的应用7.1 二极管整流电路7.2 二极管滤波电路7.3 二极管稳压电路第八章:晶体三极管放大电路8.1 放大电路的基本概念8.2 晶体三极管放大电路的设计与分析8.3 晶体三极管放大电路的应用实例第九章:场效应晶体管放大电路9.1 场效应晶体管放大电路的基本概念9.2 场效应晶体管放大电路的设计与分析9.3 场效应晶体管放大电路的应用实例第十章:集成电路的封装与可靠性10.1 集成电路封装技术的发展10.2 常见集成电路封装形式与特点10.3 集成电路的可靠性分析与提高方法第十一章:数字逻辑电路基础11.1 数字逻辑电路的基本概念11.2 逻辑门电路及其功能11.3 逻辑代数与逻辑函数第十二章:晶体三极管数字放大器12.1 数字放大器的基本概念12.2 晶体三极管数字放大器的设计与分析12.3 数字放大器的应用实例第十三章:集成电路数字逻辑家族13.1 数字逻辑集成电路的基本概念13.2 常用的数字逻辑集成电路13.3 数字逻辑集成电路的应用实例第十四章:半导体存储器14.1 存储器的基本概念与分类14.2 随机存取存储器(RAM)14.3 只读存储器(ROM)与固态硬盘(SSD)第十五章:半导体器件物理在现代技术中的应用15.1 半导体器件在微电子技术中的应用15.2 半导体器件在光电子技术中的应用15.3 半导体器件在新能源技术中的应用重点和难点解析重点:1. 半导体的定义、特性及其导电机制。

半导体器件物理教案课件PPT第一章:半导体简介1.1 半导体的概念与分类介绍半导体的定义解释N型和P型半导体讲解半导体材料的分类及性质1.2 半导体的导电特性说明半导体的导电原理探讨半导体导电性的影响因素分析N型和P型半导体的导电特性第二章:PN结的形成与特性2.1 PN结的形成讲解PN结的形成过程说明PN结的形成机制探讨PN结的平衡状态2.2 PN结的特性分析PN结的伏安特性讲解PN结的击穿现象探讨PN结的势垒结构和电荷分布第三章:二极管的结构与特性3.1 二极管的结构介绍二极管的结构及组成讲解P型和N型半导体对接形成二极管的过程探讨二极管的掺杂浓度和材料选择3.2 二极管的特性分析二极管的伏安特性讲解二极管的正向和反向导通条件探讨二极管的动态响应特性和温度特性第四章:二极管的应用4.1 整流电路讲解二极管整流电路的原理分析整流电路的电压和电流波形探讨整流电路的效率和输出特性4.2 滤波电路介绍二极管滤波电路的原理分析滤波电路的频率响应特性探讨滤波电路的应用场景和效果4.3 稳压电路讲解二极管稳压电路的原理分析稳压电路的稳压特性探讨稳压电路的选用和设计要点第五章:晶体三极管的结构与特性5.1 晶体三极管的结构介绍晶体三极管的结构及组成讲解PNP和NPN型晶体三极管的结构特点探讨晶体三极管的制造工艺和材料选择5.2 晶体三极管的特性分析晶体三极管的伏安特性讲解晶体三极管的工作原理探讨晶体三极管的电流放大效应和输出特性第六章:晶体三极管的应用6.1 放大电路讲解晶体三极管放大电路的原理分析放大电路的电压和电流波形探讨放大电路的输入和输出特性6.2 开关电路介绍晶体三极管开关电路的原理分析开关电路的转换特性探讨晶体三极管在开关电路中的应用和选择第七章:场效应晶体管的结构与特性7.1 场效应晶体管的结构介绍场效应晶体管的结构及组成讲解MOSFET和JFET的结构特点探讨场效应晶体管的制造工艺和材料选择7.2 场效应晶体管的特性分析场效应晶体管的伏安特性讲解场效应晶体管的工作原理探讨场效应晶体管的电流放大效应和输出特性第八章:集成电路的基本原理8.1 集成电路的构成介绍集成电路的构成要素讲解集成电路的制造工艺探讨集成电路的分类和应用领域8.2 集成电路的设计与制造分析集成电路的设计流程讲解集成电路的制造步骤探讨集成电路的设计原则和制造技术第九章:常用集成电路应用实例9.1 放大集成电路讲解放大集成电路的原理与应用分析放大集成电路的性能指标探讨放大集成电路在实际电路中的应用实例9.2 数字集成电路介绍数字集成电路的原理与应用分析数字集成电路的逻辑功能探讨数字集成电路在数字系统中的应用实例第十章:半导体器件的发展与新技术10.1 半导体器件的发展历程回顾半导体器件的发展历程分析不期半导体器件的特点和突破探讨半导体器件未来发展趋势10.2 半导体新技术介绍半导体新技术的研究方向分析半导体新技术的应用前景探讨半导体新技术对半导体产业的影响重点和难点解析重点环节1:半导体的导电特性需要重点关注半导体导电原理和影响导电性的因素,因为这是理解后续半导体器件工作的基础。

半导体器件物理进展第六章其它特殊半导体器件简介Introduction to other Special Semiconductor Devices本章内容提要:LDMOS、VDMOS等高压功率器件 IGBT功率器件简介SOI器件与集成电路电荷耦合器件的原理与应用1. LDMOS、VDMOS功率器件(1)MOSFET作为功率器件的优势:MOSFET为多子(多数载流子)器件,电流温度系数为负值(由迁移率随温度的变化引起),不会发生双极型功率器件的二次击穿现象(由Iceo,β随温度的升高而引起);没有少子(少数载流子)的存贮效应,开关响应速度较快;栅极输入阻抗较高,所需的控制功率较小;具有一定的功率输出能力,可与控制电路集成在一起,形成Smart Power IC,例如LCD显示器的高压驱动电路(Driver)。

(2)MOSFET的击穿特性:(A)导通前的击穿:源漏穿通:早期的解释:随着源漏电压增大,→源漏耗尽区不断展宽,直至相碰到一起,→导致发生源漏穿通效应(这里仍然采用的是平面PN结耗尽区的概念,尽管可能不是十分准确);目前的理解:由于DIBL效应引起的源漏穿通,与器件的沟道长度及沟道掺杂分布有关,其特点是(与PN结的击穿特性相比)击穿特性的发生不是非常急剧,换句话说,器件的击穿特性不是十分陡直的硬击穿,而是比较平缓的软击穿特性。

漏端PN结击穿:比单纯的非MOSFET漏区的PN结击穿电压要低(原因:受场区离子注入、沟道区调开启离子注入等因素的影响),由于侧向双极型晶体管的放大作用,使得BV PN 有所下降(类似BV CEO 小于BV CBO ),不同点在于MOS器件的衬底(相当于BJT器件的基区)不是悬空的,而是接地(只是接地电阻可能偏大),这种击穿特性的特点是雪崩电流的发生比较急剧,发生雪崩效应之前的反向电流也很小。

(B )导通后的击穿:主要是由于侧向双极型晶体管效应所导致,特别是由于器件衬底电流的影响,将使源衬PN 结出现正偏现象,致使侧向双极型晶体管效应更为严重。

MOSFET导通后的击穿现象:(C)提高MOSFET击穿电压的有效方法:在器件的漏区周围增加低掺杂的过渡区,以减小漏端峰值电场强度,从而提高器件的击穿电压。

(3)高压MOS器件结构的电场分析:N-区的作用:当高压MOS器件截止时,N-区为耗尽层的过渡区;当器件导通时,N-区则相当于一个串联电阻。

器件截止时的漏端电场分析:N-区的耗尽是从器件沟道的末端逐步展开的,假定最后所加的源漏电压VDS 刚好将N-区完全耗尽,按照平面PN结近似,则漏端耗尽区中的最大电场强度为:S DD M LqN Eε=高压MOS器件漏端电场分布情况分析:漏端耗尽区中的最大电场为S DD M LqN Eε=假定外加电压基本上都降落在N-区上(这对应于单边突变PN结、沟道截止的情况,是一个基本合理的假设),则相应的所加源漏电压V DS 为:S D D DSL qN V ε22≈由此得到:SDSD M V qNE ε2=器件发生击穿时,其最大电场是确定的,即为半导体材料的击穿电场强度,对硅材料,即:cm V E E C M /1055×≈=由此得到器件的击穿电压为:DCS DS qN E BV 22ε=关于器件N-区的优化:为确保所需的击穿电压,N-区的掺杂浓度要足够低,N-区的长度也要足够长;但是N-区的掺杂浓度过低,N-区的长度过长,将会使器件的串联电阻大大增加。

一般在进行高压MOS 器件的优化设计时,依据击穿时的最大电场强度,按照所需的击穿电压首先确定N-区的掺杂浓度,然后再求出对应的N-区长度。

由上式可见,在MOS 器件N-区长度L D 足够长的前提下,适当降低N-区的掺杂浓度,可以提高器件的最大击穿电压。

(4)DDD(Double Diffused Drain)器件结构与漏阱过渡方案:主要优点:如图所示,器件的漏端PN结处于全保护状态,即不但保护了沟道-漏端PN结的击穿,也保护漏-衬PN结的击穿。

串联的耗尽型MOS器件的作用:减小串联电阻,但不影响截止时的过渡区;另外耗尽型MOS器件的饱和特性可大大减小源漏电流的上翘现象。

(5)LDMOS(Lateral Double-Diffused MOS)器件:器件结构特点:采用源区双扩散结构,利用P型杂质比N型杂质扩散速度快的特点,由二者的扩散结深之差形成器件的导电沟道和有效沟道长度,另外结构上在器件漏端包含一个串联的耗尽型NMOS器件。

性能特点:可提供高压、大电流和中等输出功率,另外器件结构上容易形成较大的栅-漏寄生电容,具有米勒效应(Miller Effect),对器件的高频性能会有较大的负面影响。

(6)VDMOS(Vertical Double -Diffused MOS)器件:性能特点:通过多单元组合和外延层厚度及掺杂浓度的优化,可望提供高电压、大电流和中等的输出功率(通常高于LDMOS器件)。

器件结构特点:同样采用双扩散结构,利用P型杂质比N型杂质扩散速度快的特点,由二者的扩散结深之差形成器件的导电沟道和有效沟道长度,但其漏极为衬底(在垂直方向),因此该结构仅适用于高压、大电流的分立器件,不利于单片集成化。

(7)实际CMOS工艺中的高压MOS器件实现方案:2.IGBT(绝缘栅双极型晶体管,Insulated Gate Bipolar Transistor)功率器件简介(1)器件基本结构:类似VDMOS器件,只是将N+衬底改换成了P+衬底,这种改换巧妙地将双极型器件中的电导调制效应引入到了N型漂移区中,从而大大降低了器件的导通电阻。

其中的发射极(Emitter)有时也称作阴极(Cathode),收集极(Collector)有时也称作阳极(Anode)。

右图所示为IGBT器件中一个单元的剖面结构示意图国际电工委员会IEC在其TC(CO)1339号文件中对IGBT器件中的各个区域做了如下的命名规定,即继续沿用MOSFET的命名原则,将上述N+区称为源区或源极,N-外延层称为漏区,源区和漏区之间的P型区称为亚沟道区(Sub-channel region),控制栅仍称为栅极,P+衬底称为漏注入区(Drain Injector)或漏极,这是IGBT器件特有的功能区,它与漏区及亚沟道区一起构成了一个PNP型的双极型晶体管,并起到发射区的作用,向漏区注入空穴,进行电导调制,从而降低IGBT器件的通态压降。

另外,为了兼顾传统的习惯,IEC同时也规定,源区或源极(S)也可称为发射极(E),漏极(D)也可称为收集极(C)。

IGBT器件的等效电路:IGBT器件的等效电路可由一个NMOS晶体管和一个PNP 型的双极晶体管构成。

注意:图中In 为通过NMOS晶体管的沟道电子电流给PNP型双极晶体管基区提供的基极电子电流。

IGBT器件在电路中常用的符号(2)工作原理分析:反向关断状态:当收集极上外加的电压相对于发射极为负值时,器件下方的PN结J 1将处于反偏状态,因此无电流流过IGBT器件,外加的反向负电压主要降落在N型漂移区上,故器件对反向负电压具有较高的反向阻断能力;正向关断状态:当收集极上外加的电压相对于发射极为正值时,如果器件的栅极电压为零(即栅极与发射极相连),此时器件上部的PN结J 2将处于反偏状态,因此仍然无电流流过器件,外加的正向电压也同样是主要降落在N型漂移区上,器件也同样具有较高的正向阻断能力;正向导通状态:当收集极上外加的电压相对于发射极为正值,且栅极相对于发射极的电压也足够高,使得栅极下面的P型区表面达到反型,此时电子由N+发射区流向N型漂移区,给垂直结构的PNP晶体管提供基极电流。

由于该PNP双极型晶体管的发射结J 1处于正偏状态,通过晶体管的放大作用,器件具有较强的正向电流导通能力;通过金属连线将PN结J 3短路,从而使寄生的PNPN晶闸管效应得到抑制,保证器件可以有效地关断;IGBT由于出色地将MOSFET和双极型晶体管的优点结合在一起,它自二十世纪八十年代诞生以来,已经逐步发展成为最受瞩目的高压功率器件之一。

3. SOI器件与集成电路SOI技术(绝缘层上硅,Silicon On Insulator),最早是从SOS(蓝宝石上硅,Silicon On Sapphire)技术发展过来,目前制备SOI材料的技术主要有ELO (外延横向过生长,Epitaxial Lateral Overgrowth)、SIMOX(注氧隔离,Separation by IMplantation of Oxygen)和SDB(硅片直接键合,Silicon Direct Bonding)等方法。

SOI技术的优点:利于三维集成,可望实现高密度集成电路;源漏PN结寄生电容减小,便于实现超高速;抗辐射,可用于航天和军事武器装备中;彻底消除了体硅CMOS器件结构中所固有的Latch-up效应。

辐射对半导体器件造成的影响主要分两大类:硬损伤和软失效。

硬损伤主要是由各种高能射线对器件造成的辐射损伤和特性退化;软失效则是当高能粒子穿过器件中的耗尽区,沿着其运动轨迹将激发大量电子-空穴对,产生光电流,从而造成电路中的动态信息丢失甚至静态逻辑翻转。

在SOI器件中,由于没有大面积的阱区,仅有垂直的源漏PN结侧面,结面积很小,且衬底是绝缘层,无电流通路,因此其抗辐射能力较强。

SOI器件中彻底消除了体硅CMOS电路中固有的寄生PNPN结构,因此从根本上杜绝了Latch-up效应的发生,提高了电路的可靠性。

厚膜SOI器件与薄膜SOI器件:(部分耗尽SOI器件与全耗尽SOI器件,即Partially Depleted 器件和Fully Depleted器件,简称PD SOI和FD SOI,区别在于硅薄膜中是否存在中性区。

)背栅耦合效应:所谓背栅耦合效应,是指SOI上的硅薄膜与绝缘衬底的界面处以及背面氧化层中往往会有正电荷存在,这样就会对器件的沟道有影响,特别是对于SIMOX的SOI衬底,其背面氧化层的厚度一般不是很大,背栅效应就会更加明显。

对于厚膜SOI器件(部分耗尽器件),由于存在中性屏蔽区,所以背栅一般不会影响表面沟道,但是有可能会形成背面的漏电沟道;对于薄膜SOI器件(全耗尽器件),一共有四方面的电荷(源PN结电荷、漏PN结电荷、表面栅界面电荷与栅电荷、背栅电荷)共同决定器件的开启电压,但是基本上不存在背面的漏电沟道。

SOI器件的漏电分析:SOI器件通常漏电流比较大,其原因主要是:(1)SOI薄膜材料的缺陷密度比较高,其中少数载流子的寿命较短,导致的产生电流较大;(2)器件有源区边缘的表面存在较多缺陷,因此有源区边缘处往往存在漏电通道;(3)厚膜SOI器件的背面存在寄生沟道漏电等。