模拟IC基础学习(二)-模拟IC电路设计问题

- 格式:docx

- 大小:15.49 KB

- 文档页数:1

第1篇引言:集成电路(IC)设计是一项复杂而精细的工作,要求设计者具备深厚的理论知识、丰富的实践经验以及出色的逻辑思维能力。

为了帮助您了解自己在IC设计领域的智力水平,我们特别设计了以下智力测试题。

请您认真作答,完成后可对自己的设计能力有一个初步的认识。

第一部分:基础知识1. 选择题- 下列哪个选项不是IC设计中所使用的制造工艺?A. CMOSB. TTLC. ECLD. LED2. 填空题- 在IC设计中,版图(Layout)是电路的__________,而原理图(Schematic)则是电路的__________。

3. 简答题- 简述CMOS工艺的基本原理。

第二部分:逻辑分析与设计1. 选择题- 下列哪个电路可以实现逻辑与功能?A. OR门B. AND门C. NOT门D. XOR门- 在组合逻辑电路中,如果某一输入变量经过不同途径传输后,到达电路中某一汇合点的时间有先有后,这种现象称为__________。

3. 简答题- 解释竞争与冒险现象,并说明如何消除它们。

第三部分:版图设计1. 选择题- 下列哪个工具常用于IC版图设计?A. Altium DesignerB. CadenceC. OrCADD. Pro/ENGINEER2. 填空题- 在版图设计中,为了防止寄生效应,通常需要将__________与__________保持一定的距离。

3. 简答题- 简述版图设计中的规则检查(DRC)和设计规则约束(DRC)。

第四部分:IC制造1. 选择题- 下列哪个步骤是IC制造过程中的关键步骤?A. 光刻B. 化学气相沉积C. 离子注入D. 刻蚀- 在IC制造中,__________是将电路图形转移到硅片上的关键步骤。

3. 简答题- 简述IC制造过程中可能遇到的问题及解决方法。

第五部分:模拟IC设计1. 选择题- 下列哪个电路属于模拟电路?A. 741运算放大器B. 555定时器C. 74LS00D. 74HC002. 填空题- 在模拟IC设计中,__________是放大信号的关键元件。

模拟IC设计知识分享(1)最近刚好要考AAIC了,于是就想着怎么把考试的知识点总结起来分成章节。

本来想画成思维导图,但一是很多公式很多图,二是知识点间相互都有联系,也着实不太好具象化。

模拟电路就是折中的艺术,硬要画成放射状也是有点难为我了。

不如就写成文章,不仅能帮助我learning by teaching,说不定也能造福点后人。

MOS管作为模拟IC的基础组成部分,掌握MOS的各项特性是重中之重。

但由于MOS管其实是一个特性非常复杂,且无法用一个简单模型做出概括的非线性器件,我们也有必要对其进行一定的简化。

我们首先介绍MOS的基本结构和简化模型。

一、MOS管三维结构MOS管符号[1]典型的NMOS拥有四个端口,分别是栅极(gate),源极(source),漏极(drain)和衬底(body/bulk)。

MOS管是一种将电压转化为电流的器件,可以简单理解为一个压控电流源,以栅极和源极间的电压控制流过漏极和源极的电流。

根据各个端口间电压的不同,MOS管还可以分为三个工作区域,分别为截止区(cut-off region),线性区/三极管区(triode region)和饱和区(saturation region)。

我们可能已经了解MOS管可以用作开关,也可以对信号进行放大。

当MOS管用作开关时,它就工作在线性区;而当用作放大器时,它需要工作在饱和区。

在进一步分析每个工作区域的特性和条件之前,我们首先把这个抽象模型和实际世界的MOS管这一半导体器件对应起来。

NMOS管三维结构[2]上图所示是一个NMOS的结构图。

器件制作在p型衬底(substrate)上,两个n离子掺杂区形成源极和漏极,并通过金属引出。

早期MOS管的栅极由金属层制成(如图,这也是MOSFET名字中第一个M-Metal的由来),但现今大部分的MOS 管采用多晶硅(poly)来制作栅极,而名字却没有随之修改。

当然多晶硅和金属制作栅极各有利弊,还请详见半导体物理一书。

全差分高增益放大器的设计一、设计产品名称全差分高增益放大器二、设计目的1.掌握模拟集成电路的基本设计流程;2.掌握Cadence基本使用方法;3.学习模拟集成电路版图的设计要点;4.培养分析、解决问题的综合能力;5.掌握模拟集成电路的仿真方法;6.熟悉设计验证流程方法。

三、设计内容全差分高增益放大器(Full-differential OTA)是一种非常典型的模拟IP, 在各类模拟信号链路、ADC.模拟滤波器等重要模拟电路中应用广泛, 是模拟IC 设计人员必需掌握的一种基础性IP 设计。

采用华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 设计一款全差分高增益放大器电路, 完成电路图设计、前仿真、Layout 设计和物理验证(DRC&LVS)。

考虑以下OTA 架构:图1 OTA架构四、电路设计思路模拟集成电路的设计分为前端与后端, 设计流程可以分为明确性能要求、选择电路结构、计算器件参数、原理图绘制、前仿真、版图绘制、DRC设计规则检查、LVS版图与电路图一致性检查、寄生参数提取及后仿真、流片测试。

本次实验使用基于华大九天Aether 全定制IC 设计平台及其自带的0.18um PDK, 实现模拟集成电路全差分高增益放大器的全流程设计与仿真。

(1)性能指标:需要验证三种PVT Corner:a) 电源电压1.8V, 温度27℃, corner 为TT;b) 电源电压1.6V, 温度80℃, corner 为SS;c) 电源电压2.0V, 温度-40℃, corner 为FF;要求各Corner 下开环技术指标(含Cload=10fF):①放大器开环DC 增益Av0≥90dB;②0dB 带宽BW0≥500MHz;③相位裕度Phase Margin≥50°。

④DC 抑制比PSRR-0≥60dB, (3*2=6 分)⑤10MHz 时抑制比PSRR-10M≥45dB。

数字ic设计流程与模拟IC1. 首先是使用HDL语言进行电路描述,写出可综合的代码。

然后用仿真工具作前仿真,对理想状况下的功能进行验证。

这一步可以使用Vhdl或Verilog作为工作语言,EDA工具方面就我所知可以用Synopsys的VSS(for Vhdl)、VCS(for Verilog)Cadence的工具也就是著名的Verilog-XL和NC Verilog2.前仿真通过以后,可以把代码拿去综合,把语言描述转化成电路网表,并进行逻辑和时序电路的优化。

在这一步通过综合器可以引入门延时,关键要看使用了什么工艺的库这一步的输出文件可以有多种格式,常用的有EDIF格式。

综合工具Synopsys的Design Compiler,Cadence的Ambit3,综合后的输出文件,可以拿去做layout,将电路fit到可编程的片子里或者布到硅片上这要看你是做单元库的还是全定制的。

全定制的话,专门有版图工程师帮你画版图,Cadence的工具是layout editor单元库的话,下面一步就是自动布局布线,auto place & route,简称apr cadence的工具是Silicon Ensembler,Avanti的是Apollo layout出来以后就要进行extract,只知道用Avanti的Star_rcxt,然后做后仿真,如果后仿真不通过的话,只能iteration,就是回过头去改。

4,接下来就是做DRC,ERC,LVS了,如果没有什么问题的话,就tape out GDSII格式的文件,送制版厂做掩膜板,制作完毕上流水线流片,然后就看是不是work 了做DRC,ERC,LVSAvanti的是Hercules,Venus,其它公司的你们补充好了btw:后仿真之前的输出文件忘记说了,应该是带有完整的延时信息的设计文件如:*.VHO,*.sdfRTL->SIM->DC->SIM-->PT-->DC---ASTRO--->PT----DRC,LVS--->TAPE OUT1。

EE笔试/面试题目集合分类--IC设计基础1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

(仕兰微面试题目)2、FPGA和ASIC的概念,他们的区别。

(未知)答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点模拟电路1、基尔霍夫定理的内容是什么?(仕兰微电子)2、平板电容公式(C=εS/4πkd)。

(未知)3、最基本的如三极管曲线特性。

(未知)4、描述反馈电路的概念,列举他们的应用。

(仕兰微电子)5、负反馈种类(电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈);负反馈馈的优点(降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用)(未知)6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子)7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。

(未知)8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。

(凹凸)9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺点,特别是广泛采用差分结构的原因。

(未知)10、给出一差分电路,告诉其输出电压Y+和Y-,求共模分量和差模分量。

(未知)11、画差放的两个输入管。

(凹凸)12、画出由运放构成加法、减法、微分、积分运算的电路原理图。

并画出一个晶体管级的运放电路。

(仕兰微电子)13、用运算放大器组成一个10倍的放大器。

模拟IC设计-我的成长经历我想讲讲自己的成长历程,主要是技术能力是怎么提升的。

先简单介绍一下。

本人一直从事audio dac/adc的,也就是sigma delta dac/adc,在audio中,dac远比adc重要,所以重点还是在dac上。

目前dac的水平是做到了100多个db的动态范围,关键在于功耗很低面积很小,是在公司原来70多个db的基础上,不仅将性能做到了100多个db,还将功耗面积都大大减少了,性能功耗面积全面超出了国外知名的IP供应商。

你买mp3之类的东西,你说是播放重要还是录音重要呢?所以dac比adc重要。

我不是什么大牛,只不过有点心得感悟,拿出来分享而已。

写得不好,见笑了。

在学校的时候我一直想做个程序设计师,自己摸索编程(编称对一个模拟电路设计工程师来说是很重要的,后面会提到),毕业后却成了模拟电路设计师。

实际的我的专业不是计算机也不是微电子。

刚进公司时实际上只懂得一点点带隙基准的设计,实际上连ac/tran仿真都没有弄明白,还不知道电路一定要经过tran仿真,密勒补偿也不知道是什么意思。

现在回想起来笑死人了。

刚分给项目组时,主管在忙项目,刚好项目遇到瓶颈,他又不喜欢带人,觉得我又用不上,干脆就分给我一个课题:研究一下classd吧,现在挺火的,研究好了你就是专家了,公司没有人研究过。

于是我就开始了长达半年多的放羊式的工作生涯,大部分的基础都是在这个时候建立的。

在这些时间内我干吗呢?看看拉扎维,gray的书,发现跟classd也没什么关系阿,在网上找paper,看了将近100多篇,还是没有头绪,毕竟paper中的垃圾太多了,找出真正好的paper不容易。

后来终于找到TI的一篇classd论文,讲得很好,于是试着做电路,并且开始仿真。

后面我将讲一些自己感觉对学习模拟电路真正有用的方法。

说的没错,机遇还是很重要的,重要的是自己善于把握机遇。

人生就这样,什么时间段就做什么事情,如果把握不住,以后就再没有这么好的时光了,珍惜现在非常重要。

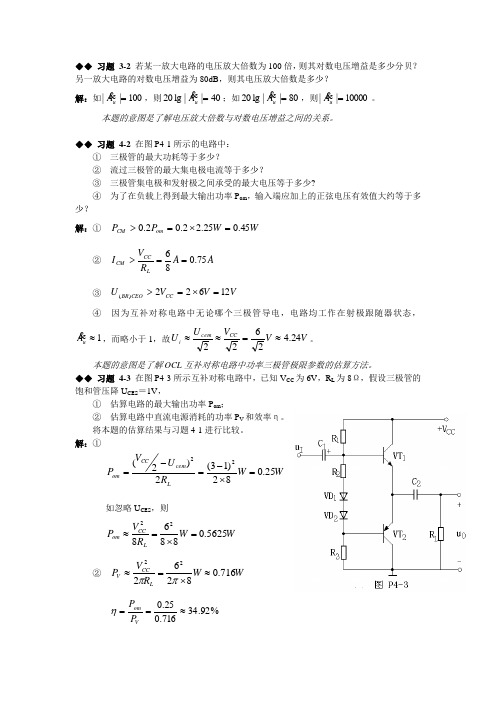

◆◆ 习题 3-2 若某一放大电路的电压放大倍数为100倍,则其对数电压增益是多少分贝?另一放大电路的对数电压增益为80dB ,则其电压放大倍数是多少?解:如100||=u A ,则40||lg 20=u A ;如80||lg 20=u A ,则10000||=uA 。

本题的意图是了解电压放大倍数与对数电压增益之间的关系。

◆◆ 习题 4-2 在图P4-1所示的电路中:① 三极管的最大功耗等于多少?② 流过三极管的最大集电极电流等于多少?③ 三极管集电极和发射极之间承受的最大电压等于多少?④ 为了在负载上得到最大输出功率P om ,输入端应加上的正弦电压有效值大约等于多少?解:① W W P P om CM 45.025.22.02.0=⨯=>② A A R V I L CC CM 75.086==>③ V V V U CC CEO BR 12622)(=⨯=>④ 因为互补对称电路中无论哪个三极管导电,电路均工作在射极跟随器状态,1≈u A ,而略小于1,故V V V U U CC cem i24.42622≈=≈≈。

本题的意图是了解OCL 互补对称电路中功率三极管极限参数的估算方法。

◆◆ 习题 4-3 在图P4-3所示互补对称电路中,已知V CC 为6V ,R L 为8Ω,假设三极管的饱和管压降U CES =1V ,① 估算电路的最大输出功率P om ;② 估算电路中直流电源消耗的功率P V 和效率η。

将本题的估算结果与习题4-1进行比较。

解:①W W R U V P Lcem CCom 25.082)13(2)2(22=⨯-=-=如忽略U CES ,则W W R V P L CC om 5625.0886822=⨯=≈② W W R V P L CC V 716.0826222≈⨯=≈ππ %92.34716.025.0≈==V om P P η如忽略U CES ,则%56.78716.05625.0≈==V om P P η 可见,在同样的VCC 和RL 之下,OCL 电路的Pom 比OTL 电路大得多(大约为4倍)。

模拟IC设计知识分享IC设计是指集成电路的设计,也是一项复杂的工作。

在IC设计中,需要涉及到多个领域的知识,例如电路设计、物理学、数学和计算机科学等等。

本文将模拟一个IC设计知识分享,介绍IC设计的基本概念和流程。

首先,我将介绍IC设计的基本概念。

IC是Integrated Circuit的缩写,即集成电路。

集成电路是一种将多个电子元件(如晶体管、电阻、电容等)集成在一块半导体芯片上的电路。

IC设计是指设计这些芯片的电路。

IC设计的流程可以大致分为几个步骤。

首先是需求分析,根据客户的需求和设计规范,确定设计的目标和功能。

然后是电路设计,根据需求确定电路的结构和参数,并进行电路仿真和优化。

接下来是版图设计,将电路布局在芯片上,并进行布线。

最后是芯片制造和测试,将设计好的电路制造出来,然后进行测试和确认。

在进行电路设计时,需要掌握一些基本的电路知识。

例如,需要了解各种基本的电路元件的特性,如晶体管的工作原理、电容的充放电过程等等。

同时还需要掌握一些常用的电路拓扑结构,如放大器、滤波器、振荡器等等。

此外,还需要了解一些常用的电路设计工具,如Spice软件,用于电路仿真和优化。

在进行版图设计时,需要了解一些物理学知识。

例如,需要了解芯片制造工艺,如光刻、薄膜沉积、离子注入等等。

同时还需要了解一些布局和布线规则,以确保电路的稳定性和可靠性。

在进行芯片制造和测试时,需要了解一些微电子学和电子测试的知识,以确保芯片的质量和性能。

除了电路设计的知识之外,还需要掌握一些计算机科学的知识。

例如,需要掌握一些编程语言,如Verilog HDL或VHDL,用于描述和模拟电路。

同时,还需要掌握一些计算机辅助设计工具,如EDA软件,用于电路设计和版图设计。

总结一下,IC设计是一项复杂而多学科交叉的工作。

它需要掌握电路设计、物理学、数学和计算机科学等多个领域的知识。

同时,还需要掌握一些电路设计工具和计算机辅助设计工具。

希望通过这次模拟的IC设计知识分享,能够对IC设计感兴趣的人提供一些参考和了解。

写下这个标题,自己都觉得太大了,BS自己一个:)IC设计毕竟覆盖了RF、Analog、Digital、SOC、MEMS等各个门类,想要说的比较清楚实在是太难了,这里只是凭自己的一点经验介绍给大家一点学习方法。

昨晚看到这个帖子:请教关于数字IC和模拟IC设计这2个方向的选择,个人觉得做数字、模拟或者RF,关键还是看你喜好了,至于钱途怎样还要看你个人的发展了,数字也有做的很好的,模拟和RF也有做的差的,当然这两者拿的钱自然也是有差距的。

所以希望大家还是选择自己感兴趣的,在这基础上不断提高自己的设计水平。

Layout做的好也是相当来钱的哦^_^总有同学要问:前端设计和后端设计是怎么区分的啊?对模拟电路而言,实际上可以简单的把Layout之前的工作都可以看作前端设计,Layout以及之后的工作看作后端设计,但是Layout之后post-simulation还是要由前端工程师完成;对于数字电路,目前数字电路的前端设计可以看作为代码综合前的所有工作,后端包括了综合,到P&R,以及STA的整个过程,目前数字电路的前后端工具都已经十分成熟,如candence和synopsys都能够提供整套的设计工具。

下面主要针对模拟、数字以及我所了解的SOC设计知识向大家简要介绍一下:模拟IC设计:目前国内大多数模拟IC设计采用逆向设计方法,逆向设计的好处在于:通过对于别人电路的学习和分析,能够锻炼你的电路分析能力;通过芯片解剖,能学习先进的半导体工艺技术。

当然,长期的逆向设计将会遏制你的创新能力,国内模拟设计的目标是通过从逆向设计慢慢转向初步乃至全部的正向设计,逐渐缩小与国外模拟设计的差距。

模拟电路设计工程师成长期较长,约为5-7年(数字电路设计工程师约为3-5年),作为一个合格的模拟集成电路设计工程师,个人觉得所具备的知识应该包括:首先应该是器件物理:包括半导体物理、晶体管原理等等,器件的导电原理是整个电路设计的基础,晶体管的各个工作区,电流电压方程,影响器件参数的各个因素都应该十分熟悉,如对于Bipolar管,在设计中你需要它工作在饱和区、放大区、还是截止区,你对其放大倍数和电流能力要求是什么?影响其放大倍数和电流能力的主要因素有哪些?它的寄生参数对于你管子性能有何影响?击穿特性又如何?……相信这些在半导体物理和晶体管原理中都能找到答案;其次是工艺知识,模拟电路的设计需要对于工艺具有相当深刻的理解,如设计一个运放,根据所给的参数指标,你是选择CMOS、BIPOLAR还是BICMOS工艺?在所选工艺中,你所需要的各种器件Foundry是否都能够提供,各种器件的参数是否能满足你设计的要求?不能满足的话,你应该采用何种替代方法或是能够调整哪些工艺参数得到满足你设计要求的器件?当你调整工艺参数后,对你器件的其它的参数是否有影响,对你的后端Layout是否产生影响?等等一系列的问题的解决都需要你对工艺的透彻理解;然后才是电路,现在市场上介绍电路的书已经很多了,模拟设计的四大宝典也不必向大家罗嗦了。

模拟ic校招知识点总结一、电路基础。

1. 基本电路元件。

- 电阻:理解电阻的定义(R = (V)/(I)),不同类型电阻(如碳膜电阻、金属膜电阻等)的特性。

在模拟电路中,电阻用于分压、限流等操作。

例如,在一个简单的分压电路中,根据串联电阻的电压分配原理V_1=(R_1)/(R_1 + R_2)V_in。

- 电容:电容的定义C=(Q)/(V),其储存电场能量的特性。

电容在模拟电路中有滤波、耦合等作用。

在一阶RC低通滤波器中,截止频率f_c=(1)/(2π RC),它可以滤除高频信号。

- 电感:电感的定义L=(varPhi)/(I),它储存磁场能量。

在模拟电路中,电感常用于滤波(如LC滤波器)等,不过在集成电路中,由于电感占用面积大,使用相对较少。

2. 基尔霍夫定律。

- 基尔霍夫电流定律(KCL):所有进入某节点的电流的总和等于所有离开这节点的电流的总和。

例如,对于一个有三条支路的节点,I_1+I_2 - I_3=0。

- 基尔霍夫电压定律(KVL):沿着闭合回路所有元件两端的电势差(电压)的代数和等于零。

在一个简单的串联电路中,V_R1+V_R2-V_in=0。

3. 戴维南定理和诺顿定理。

- 戴维南定理:任何一个线性含源一端口网络,对外电路来说,可以用一个电压源和电阻的串联组合来等效置换;该电压源的电压等于这个一端口网络的开路电压,电阻等于这个一端口网络内全部独立电源置零后的输入电阻。

- 诺顿定理:任何一个线性含源一端口网络,对外电路来说,可以用一个电流源和电导的并联组合来等效置换;电流源的电流等于这个一端口网络的短路电流,电导等于把这个一端口网络内全部独立电源置零后的输入电导。

二、半导体物理基础(人教版教材相关内容)1. 半导体材料。

- 本征半导体:纯净的、不含杂质的半导体称为本征半导体,如硅(Si)和锗(Ge)。

本征半导体中存在着电子和空穴两种载流子,它们是成对产生的,在热激发下,价带中的电子跃迁到导带,从而在价带中留下空穴。

一、传说中的模拟电路设计四大名著模拟电路设计在我看来是微电子领域一个集基础理论知识和创造性于一身的绝学。

就像一盘棋,别人给你准备好了棋子,如何摆出千变万化的阵势完全在于你的功力和才能。

如今的模电设计已经处在这样的层面,完备的仿真计算工具将设计者从繁琐的数据运算中解放出来。

只要你有足够的理论基底和创造性,配以对信号处理的理解和公式推算的驾驭能力,一个个完美的设计方案就会应运而生。

传说,模拟电路设计有四大名著,分别出自Berkeley的P.R.GRAY, GIT的Phillip E. Allen, UCLA的Behzad Razavi,以及Toronto的David Johns。

而其中,P.R.GRAY的著作堪称该领域的Bible。

耶和华的圣经只有一部,模电的圣经却不止Razavi一本。

要说模电的书,那可真是遍地都是,经典的也不在少数。

但个人以为,最好的有2本。

第一当然是Razavi的Design of Analog CMOS Integrated Circuits, 完美的cmos入门教材。

Berkeley的Analysis and design of analog integrated circuits很多人都评价要超过Razavi。

但是里面bipolar和CMOS并行,看得太累,至今也没完整读过。

第二本是最近才发现的,就是Willy Sansen的Analog Design Essentials。

觉得这本书的思想很多独辟蹊径,公式推理少,偏重理解,很有启发性,涵盖范围又广。

1. P.R.Gray的书这本书被业界誉为模拟IC的Bible,盛名之下,必无虚士。

现在已经出到第四版,作者无一例外是业界大牛,该书论述严谨,思路清晰,对电路分析透彻,定义严格明确,无愧Bible之名。

作为一个初学者,这是必读的一本书,虽然有中译本,但是建议去看英文原版,因为翻译实在不是太好。

该书对基本电路的分析细致深刻,但是个人觉得它写的最为引人入胜的是反馈和补偿两章,讲的很透,还有噪声一章也是几本书中讲得最详细的,对英文比较好的初学者,建议读这本书。

哈尔滨理工大学软件学院模拟IC课程设计报告课程模拟IC设计题目二级运算放大器专业集成电路设计与集成班级集成10-2班学生唐贝贝学号1014020227指导老师陆学斌2013年6月14日目录1.课程设计目的…………………………………………………2.课程设计题目描述和要求……………………………………3.课程设计具体内容……………………………………………3.1 设计过程分析……………………………………………3.2使用软件…………………………………………………3.3 原理图……………………………………………………3.4 仿真网表…………………………………………………3.5波形分析…………………………………………………4.心得体会………………………………………………………一、课程设计目的1.熟悉并掌握Hspice与cosmosScope软件的使用。

2.熟练应用Hspice仿真网表并修改分析网表,学会用comosScope查看分析波形。

3.锻炼学生独立完成二级运算放大器的能力。

4. 在扎实的基础上强化实践能力,把模拟IC理论实践化。

二、课程设计题目描述和要求设计指标:静态功耗:小于5mw开环增益:大于70dB单位增益带宽大于5MHz相位裕量:大于60度转换速率(SR)大于20V/us共模抑制比:大于60dB电源抑制比:大于70dB输入失调:小于1mV负载电容:2-4pF要求:1、手工计算出每个晶体管的宽长比。

通过仿真验证设计是否正确,保证每个晶体管的正常工作状态。

2、使用Hspice工具得到电路相关参数仿真结果,包括:幅频和相频特性(低频增益,相位裕度,单位增益带宽)、CMRR、PSRR、共模输入输出范围、SR等。

3、每个学生应该独立完成电路设计,设计指标比较开放,如果出现雷同按不及格处理。

4、完成课程设计报告的同时需要提交仿真文件,包括所有仿真电路的网表,仿真结果。

5、相关问题参考教材第六章,仿真问题请查看HSPICE手册。

模拟IC基础学习(二):模拟IC电路设计问题

很多时候,我们在初期设计或者优化电路时,满脑子想的都是性能如何能一点一点提高,而忽略了所谓的模拟设计的一些基本考虑;待到版图设计时已经晚矣。

那个时候再去修改基本设计无疑是不值得,要么耗费精力,要们前功尽弃。

作为教训,如果我们能够在设计初期,就带着这些基本考虑,那么在选择基本器件的时候,就会有的放矢,知道一个大概的合理的选取范围,有利于版图设计和优化。

1. 晶体管最小沟长为工艺最小特征尺寸的4-5倍,用来减小沟长调制效应。

2.目前模拟设计仍然是使晶体管工作在饱和区,故应使Vgs 大于Vt约30%。

3. 应把大管分成小晶体管,使其宽/长特征尺寸

第1页共1页。