4-存储器详解

- 格式:ppt

- 大小:231.00 KB

- 文档页数:36

存储器的工作原理引言概述:存储器是计算机系统中至关重要的组成部份,它用于存储和检索数据。

了解存储器的工作原理对于理解计算机系统的运行机制至关重要。

本文将详细介绍存储器的工作原理,包括存储器的分类、存储单元的结构和存储器的操作原理。

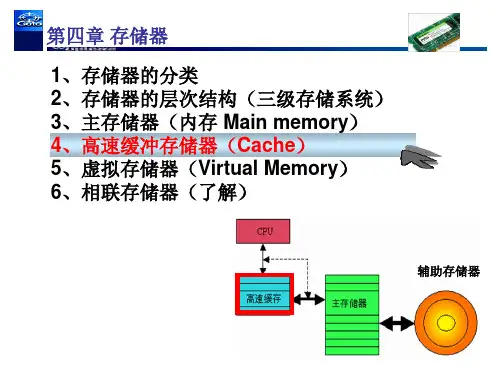

一、存储器的分类1.1 主存储器主存储器是计算机系统中最重要的存储器之一。

它用于存储当前正在执行的程序和数据。

主存储器通常是由一系列存储单元组成的,每一个存储单元都有一个惟一的地址。

主存储器可以按字节、字、块等不同的粒度进行访问。

1.2 辅助存储器辅助存储器是主存储器之外的存储器,用于长期存储程序和数据。

辅助存储器的容量通常比主存储器大得多,但其访问速度较慢。

常见的辅助存储器包括硬盘驱动器、光盘和闪存等。

1.3 高速缓存高速缓存是位于主存储器和中央处理器(CPU)之间的存储器层次结构中的一层。

它用于存储最近被访问的数据和指令,以提高计算机系统的性能。

高速缓存的容量较小,但其访问速度非常快。

二、存储单元的结构2.1 存储单元的基本组成存储单元是存储器中的最小单元,用于存储一个二进制位(0或者1)。

它通常由一个触发器或者闪存电路组成。

触发器是一种能够存储和保持数据的电路,而闪存电路是一种非易失性存储器,能够在断电后保持数据。

2.2 存储单元的编址方式存储单元可以通过地址进行访问。

常见的编址方式包括直接编址、间接编址和相对编址。

直接编址是指通过存储单元的惟一地址直接访问数据。

间接编址是指通过一个地址指针来访问数据。

相对编址是指通过相对于当前指令地址的偏移量来访问数据。

2.3 存储单元的组织方式存储单元可以按照不同的组织方式进行罗列。

常见的组织方式包括线性组织、矩阵组织和多维组织。

线性组织是指存储单元按照线性序列进行罗列。

矩阵组织是指存储单元按矩阵形式进行罗列。

多维组织是指存储单元按多维数组进行罗列。

三、存储器的操作原理3.1 存储器的读取操作存储器的读取操作是指从存储单元中检索数据。

实 验 __四__【实验名称】存储器【目的与要求】1. 计数器2. 存放器的使用3. 掌握ROM 和RAM 的工作原理4. 学会对ROM 和RAM 存取数据【实验容】1. 顺序地址修改器741612. 八D 触发器74273b3. ROM4. RAM5. 将74161作为读ram 低4位的地址来用【操作步骤】1、计数器〔顺序地址修改器〕74161,实际上是一个为可预置的4位二进制同步计数器计数器,74161的去除端是异步的。

当去除端CLRN 为低电平时,不管姓 名成 绩实验日期任课教师时钟端CLK状态如何,即可完成去除功能。

74161的预置是同步的。

当置入控制器LDN为低电平时,在CLOCK上升沿作用下,输出端QA-QD与数据输入端A -D相一致。

对于54/74161,当CLK由低至高跳变或跳变前,如果计数控制端ENP、ENT为高电平,那么LOAD应防止由低至高电平的跳变,而54/74LS161无此种限制。

74161的计数是同步的,靠CLK同时加在四个触发器上而实现的。

当ENP、ENT均为高电平时,在CLK上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。

对于54/74161,只有当CLK为高电平时,ENP、ENT才允许由高至低电平的跳变,而54/74LS161的ENP、ENT跳变与CLK无关。

74161有超前进位功能。

当计数溢出时,进位输出端〔RCO〕输出一个高电平脉冲,其宽度为QA的高电平局部。

在不外加门电路的情况下,可级联成N位同步计数器。

对于54/74LS161,在CLK出现前,即使ENP、ENT、CLRN发生变化,电路的功能也不受影响。

管脚图:功能表:1 1 1 1 ↑××××计数CO2 CO2=QD·QC·QB·QA1 1 0 ××××××保持CO3 CO3=ENT·QD·QC·QB·QA1 1 ×0 ×××××保持0仿真电路图如下:仿真结果如下:由仿真结果可以看出:CLK每来一个上升沿,计一次数。

实验四存储器管理1、目的与要求本实验的目的是让学生熟悉存储器管理的方法,加深对所学各种存储器管理方案的了解;要求采用一些常用的存储器分配算法,设计一个存储器管理模拟系统,模拟内存空间的分配和释放。

2、实验内容①设计一个存放空闲块的自由链和一个内存作业分配表,存放内存中已经存在的作业。

②编制一个按照首次适应法分配内存的算法,进行内存分配。

③同时设计内存的回收以及内存清理(如果要分配的作业块大于任何一个空闲块,但小于总的空闲分区,则需要进行内存的清理,空出大块的空闲分区)的算法。

3.实验环境①PC兼容机②Windows、DOS系统、Turbo c 2。

0③C语言4.实验提示一、数据结构1、自由链内存空区采用自由链结构,链首由指针freep指向,链中各空区按地址递增次序排列.初启动时整个用户内存区为一个大空区,每个空区首部设置一个区头(freearea)结构,区头信息包括:Size 空区大小Next 前向指针,指向下一个空区Back 反向指针,指向上一个空区Adderss 本空区首地址2、内存分配表JOBMA T系统设置一个MA T,每个运行的作业都在MAT中占有一个表目,回收分区时清除相应表目,表目信息包括:Name 用户作业名Length 作业区大小Addr 作业区首地址二、算法存储分配算法采用首次适应法,根据指针freep查找自由链,当找到第一块可满足分配请求的空区便分配,当某空区被分配后的剩余空闲空间大于所规定的碎片最小量mini时,则形成一个较小的空区留在自由链中。

回收时,根据MAT将制定分区链入自由链,若该分区有前邻或后邻分区,则将他们拼成一个较大的空区。

当某个分配请求不能被满足,但此时系统中所有碎片总容量满足分配请求的容量时,系统立即进行内存搬家,消除碎片.即将各作业占用区集中下移到用户内存区的下部(高地址部分),形成一片连续的作业区,而在用户内存区的上部形成一块较大的空闲,然后再进行分配。

存储器基础知识概览存储器是计算机中用于存储和提取数据的设备,也被称为内存。

在计算机系统中,存储器扮演着至关重要的角色,对于计算机的性能和效率有着重要影响。

本文将概览存储器的基础知识,包括存储器的分类、工作原理以及主要的存储器类型。

一、存储器的分类按照存储介质的不同,存储器可以分为两大类:主存储器和辅助存储器。

1. 主存储器:主存储器是计算机中直接与CPU进行数据交互的存储器,常见的主存储器包括随机存取存储器(RAM)和只读存储器(ROM)。

RAM具有读写功能,它能快速地存储和提取数据,但是数据存储是临时的,断电后数据会丢失。

而ROM则用于存储固定的数据和程序,内容不会因断电而丢失。

2. 辅助存储器:辅助存储器用于长期存储数据和程序,主要包括硬盘、固态硬盘、光盘和磁带等。

相较于主存储器,辅助存储器的存储容量更大,但是读写速度较慢。

二、存储器的工作原理存储器的工作原理可以简单描述为:数据从CPU传输到存储器,存储器进行存储或提取操作,然后将数据返回给CPU。

1. 写操作:当CPU需要向存储器写入数据时,它会向存储器发送写操作指令和待写入的数据。

存储器接收到指令后,将数据写入指定的地址中,以便后续读取。

2. 读操作:当CPU需要从存储器读取数据时,它会向存储器发送读操作指令和待读取数据的地址。

存储器接收到指令后,将指定地址的数据读取出来,并发送给CPU进行处理。

三、主要的存储器类型存储器的类型包括RAM、ROM以及一些特殊的存储器,如高速缓存(Cache)和虚拟内存(Virtual Memory)等。

1. RAM(随机存取存储器):RAM是计算机系统中最常见的存储器类型,它具备读和写的功能,并且数据可以快速访问。

RAM又可以分为静态RAM(SRAM)和动态RAM(DRAM)两种类型。

SRAM 的读取速度更快,但成本较高;DRAM的存储密度更高,更适合于大容量存储。

2. ROM(只读存储器):ROM用于存储无需修改的数据和程序,内容通常是出厂时被写入的。

第4章存储器1. 解释概念:主存、辅存、Cache、RAM、SRAM、DRAM、ROM、PROM、EPROM、EEPROM、CDROM、Flash Memory。

答:主存:主存储器,用于存放正在执行的程序和数据。

CPU可以直接进行随机读写,访问速度较高。

辅存:辅助存储器,用于存放当前暂不执行的程序和数据,以及一些需要永久保存的信息。

Cache:高速缓冲存储器,介于CPU和主存之间,用于解决CPU和主存之间速度不匹配问题。

RAM:半导体随机存取存储器,主要用作计算机中的主存。

SRAM:静态半导体随机存取存储器。

DRAM:动态半导体随机存取存储器。

ROM:掩膜式半导体只读存储器。

由芯片制造商在制造时写入内容,以后只能读出而不能写入。

PROM:可编程只读存储器,由用户根据需要确定写入内容,只能写入一次。

EPROM:紫外线擦写可编程只读存储器。

需要修改内容时,现将其全部内容擦除,然后再编程。

擦除依靠紫外线使浮动栅极上的电荷泄露而实现。

EEPROM:电擦写可编程只读存储器。

CDROM:只读型光盘。

Flash Memory:闪速存储器。

或称快擦型存储器。

2. 计算机中哪些部件可以用于存储信息?按速度、容量和价格/位排序说明。

答:计算机中寄存器、Cache、主存、硬盘可以用于存储信息。

按速度由高至低排序为:寄存器、Cache、主存、硬盘;按容量由小至大排序为:寄存器、Cache、主存、硬盘;按价格/位由高至低排序为:寄存器、Cache、主存、硬盘。

3. 存储器的层次结构主要体现在什么地方?为什么要分这些层次?计算机如何管理这些层次?答:存储器的层次结构主要体现在Cache-主存和主存-辅存这两个存储层次上。

Cache-主存层次在存储系统中主要对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于Cache的速度,而寻址空间和位价却接近于主存。

主存-辅存层次在存储系统中主要起扩容作用,即从程序员的角度看,他所使用的存储器其容量和位价接近于辅存,而速度接近于主存。

ddr4寻址原理(一)DDR4寻址原理一、背景介绍•DDR4(Double Data Rate 4)是一种高速存储器,广泛应用于计算机系统中。

•DDR4的寻址原理是指在访问存储器时,如何定位存储器的具体位置。

二、DDR4基本概念1.存储单元:DDR4存储器由许多存储单元组成,每个存储单元用于存储一个数据位。

2.存储单元地址:每个存储单元都有一个唯一的地址,用于寻址和访问该存储单元。

3.地址总线:地址总线是用于传输存储单元地址的信号线。

4.数据总线:数据总线是用于传输数据的信号线。

三、DDR4寻址原理1.内存地址空间:DDR4存储器有一个内存地址空间,用于定位存储单元的位置。

2.地址位数:DDR4的地址位数决定了内存地址空间的大小,也决定了DDR4能够寻址的最大容量。

3.地址转换:DDR4寻址原理中的一项重要任务是将逻辑地址转换为物理地址。

4.地址解码:DDR4的内存控制器通过地址解码电路,将逻辑地址转换为对应的存储单元地址。

5.地址映射:DDR4还会使用地址映射技术将逻辑地址映射到物理地址,提高内存的利用率。

四、DDR4寻址过程1.地址传输:CPU通过地址总线传输逻辑地址给内存控制器。

2.地址解码:内存控制器使用地址解码电路将逻辑地址转换为存储单元地址。

3.地址映射:根据地址映射表,将存储单元地址转换为物理地址。

4.访问存储单元:内存控制器通过数据总线将数据读取或写入存储单元。

五、DDR4寻址原理的优化1.行地址和列地址:DDR4内存将地址分为行地址和列地址,通过行地址选择特定的行,再通过列地址选择特定的列,以提高访问效率。

2.预取技术:DDR4内存采用预取技术,根据访问模式预先加载一定数量的数据到缓存中,减少等待时间。

3.超级扇出驱动技术:DDR4内存还采用超级扇出驱动技术,提高存储单元的响应速度。

六、总结DDR4寻址原理是通过地址总线和数据总线将CPU的逻辑地址转换为物理地址,以访问存储单元。