D触发器原理D触发器电路图

- 格式:doc

- 大小:149.00 KB

- 文档页数:3

维持阻塞D 触发器电路结构及工作原理描述边沿触发器只是在CP 的某一边沿(上升沿或下降沿)时刻才能对所作用的输入信号产生响应,即只有在CP 边沿时输入信号才有效(输出状态与输入有关),而其他时间触发器都处于保持状态。

可见,这种触发器不会有空翻现象,并且抗干扰能力增强,工作更可靠。

边沿触发器有上升沿触发和下降沿触发两种。

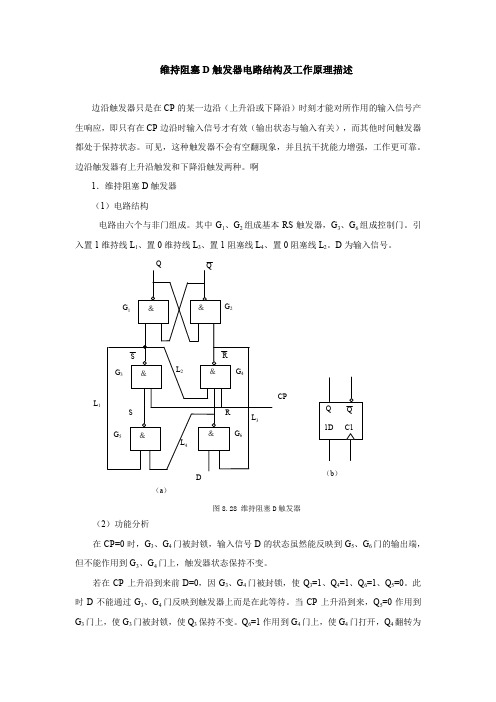

啊1.维持阻塞D 触发器 (1)电路结构电路由六个与非门组成。

其中G 1、G 2组成基本RS 触发器,G 3、G 6组成控制门。

引入置1维持线L 1、置0维持线L 3、置1阻塞线L 4、置0阻塞线L 2。

D 为输入信号。

图8.28 维持阻塞D 触发器(2)功能分析在CP =0时,G 3、G 4门被封锁,输入信号D 的状态虽然能反映到G 5、G 6门的输出端,但不能作用到G 3、G 4门上,触发器状态保持不变。

若在CP 上升沿到来前D =0,因G 3、G 4门被封锁,使Q 3=1、Q 4=1、Q 6=1、Q 5=0。

此时D 不能通过G 3、G 4门反映到触发器上而是在此等待。

当CP 上升沿到来,Q 5=0作用到G 3门上,使G 3门被封锁,使Q 3保持不变。

Q 6=1作用到G 4门上,使G 4门打开,Q 4翻转为QQDCP(a )L 1(b )0,使触发器输出Q=0、Q=1。

无论CP上升沿到来前触发器状态如何,只要D=0,但CP 上升沿到来后,触发器状态变为0。

同时Q4=0通过置0维持线L3反馈到G6门的输入端,将G6门封锁,即在CP=1期间,无论D如何变化,触发器状态保持0不变。

若在CP上升沿到来前D=1,因G3、G4门被封锁,使Q3=1、Q4=1、Q6=0、Q5=1。

此时Q6、Q5的状态不能通过G3、G4门反映到触发器上。

触发器保持原状态。

当CP上升沿到来,Q6、Q5的状态反映到触发器上,Q6=0,G4门被封锁,使Q4保持不变。

Q3翻转为0,使触发器输出Q=1、Q=0。

无论CP上升沿到来前触发器状态如何,只要D=1,CP上升沿到来后,触发器状态变为1。

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

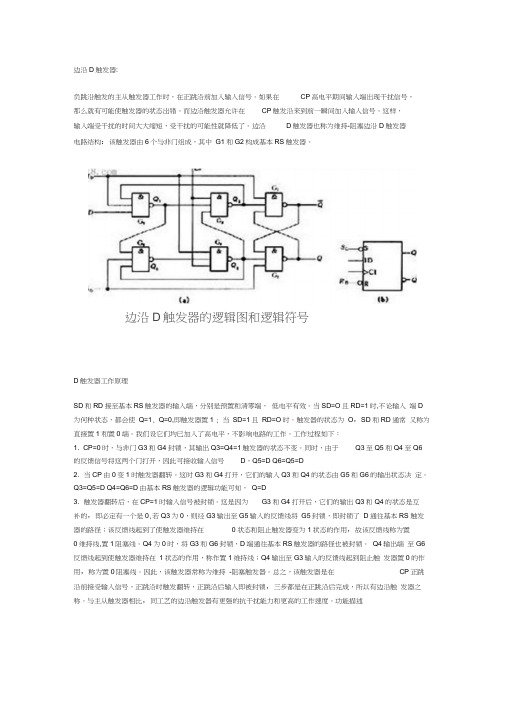

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD =0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6 =Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q =D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q 3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

边沿D 触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

D触发器工作原理:SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。

边沿D触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态岀错。

而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器电路结构:该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

边沿D触发器的逻辑图和逻辑符号D触发器工作原理SD和RD接至基本RS触发器的输入端,分别是预置和清零端,低电平有效。

当SD=O且RD=1时,不论输入端D 为何种状态,都会使Q=1, Q=0,即触发器置1 ; 当SD=1且RD=O时,触发器的状态为O,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1. CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D Q6=Q5=D2. 当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D Q4=Q6=D由基本RS触发器的逻辑功能可知,Q=D3. 触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输岀至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

边沿D 触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

D触发器工作原理:SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)(图点击,或下载后可放大)----------------------原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

d触发器电路工作原理一、引言d触发器是数字电路中常用的一种基本触发器。

它能够存储一个位的状态,并在时钟信号的作用下进行状态的改变。

d触发器在各种数字电路和计算机系统中都有广泛的应用,如存储器、寄存器、计数器等。

因此,了解d触发器电路的工作原理对于理解和设计数字电路至关重要。

二、d触发器电路结构d触发器电路由几个关键的部分组成,包括输入端d、时钟信号端clk、输出端q和反相输出端q'。

其中,d端用于输入数据,clk端用于提供时钟信号,q端用于输出数据,q'端用于输出数据的反相信号。

d触发器电路的基本结构如下所示:(这里不要输出图片链接)d触发器电路的工作原理可以通过以下几个步骤来解释:1. 初始状态:假设d触发器电路处于初始状态,q端和q'端都处于特定的状态,且与输入d无关。

2. 时钟信号作用:当时钟信号clk发生变化时,d触发器电路开始工作。

3. 数据输入:在时钟信号作用下,如果输入端d的电平为高电平,则d触发器会将这个高电平的数据存储到内部的存储单元中;如果输入端d的电平为低电平,则d触发器会将之前存储的数据保持不变。

4. 数据输出:根据输入端d的电平,d触发器将存储的数据通过输出端q输出,同时通过反相输出端q'输出数据的反相信号。

5. 状态保持:一旦数据存储到d触发器中,无论输入端d的电平如何变化,d触发器都会保持存储的数据,直到下一次时钟信号的作用。

四、d触发器电路的应用d触发器电路在数字电路和计算机系统中有着广泛的应用。

以下是一些常见的应用场景:1. 存储器:d触发器被广泛用于存储器中,用于存储和读取数据。

2. 寄存器:多个d触发器可以组成寄存器,用于存储和传输多位数据。

3. 计数器:d触发器可以用于构建计数器电路,实现数字计数功能。

4. 时序电路:d触发器可以用于构建时序电路,实现各种时序逻辑功能。

五、总结d触发器电路是数字电路中常用的一种基本触发器,具有存储一个位的能力,并能在时钟信号的作用下进行状态的改变。

D触发器工作原理引言概述:D触发器是数字电路中常用的一种触发器,它具有存储和时序控制的功能。

本文将详细介绍D触发器的工作原理,包括其基本原理、实现方式、时序图和应用场景。

一、D触发器的基本原理:1.1 逻辑门实现:D触发器可以通过逻辑门电路实现。

其中最常用的是与门和非门组成的结构,也可以通过与非门或者与或者非门等组合实现。

1.2 存储功能:D触发器具有存储功能,它可以存储输入信号的状态,并在时钟信号的作用下保持输出状态不变。

1.3 边沿触发:D触发器可以根据时钟信号的上升沿或者下降沿来触发输出状态的变化,分为上升沿触发和下降沿触发两种类型。

二、D触发器的实现方式:2.1 RS触发器:D触发器可以通过RS触发器实现。

RS触发器由两个交叉连接的与非门组成,其中一个与非门的输出连接到另一个与非门的输入,另一个与非门的输出连接到第一个与非门的输入。

2.2 JK触发器:D触发器也可以通过JK触发器实现。

JK触发器由两个交叉连接的与非门和一个与门组成,其中一个与非门的输出连接到与门的输入,另一个与非门的输出连接到另一个与非门的输入。

2.3 T触发器:D触发器还可以通过T触发器实现。

T触发器由两个交叉连接的与非门和一个异或者门组成,其中一个与非门的输出连接到异或者门的一个输入,另一个与非门的输出连接到异或者门的另一个输入。

三、D触发器的时序图:3.1 上升沿触发时序图:D触发器在时钟信号的上升沿触发时,输入信号的状态将在上升沿之前保持不变,并在上升沿之后更新到输出。

3.2 下降沿触发时序图:D触发器在时钟信号的下降沿触发时,输入信号的状态将在下降沿之前保持不变,并在下降沿之后更新到输出。

3.3 延迟时间:D触发器的输出状态更新存在一定的延迟时间,这取决于时钟信号的频率和触发器的特性。

四、D触发器的应用场景:4.1 时序电路:D触发器在时序电路中广泛应用,可以实现各种时序逻辑功能,如计数器、寄存器等。

4.2 控制电路:D触发器可以用于控制电路中,实现状态的存储和控制信号的生成。

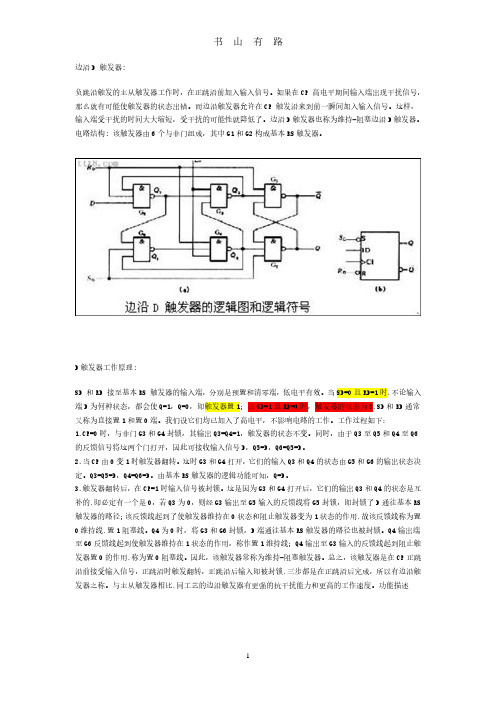

边沿D 触发器:

负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

D触发器工作原理:

SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:

1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

总之,该触发器是在CP正跳

沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。

与主从触发器相比,同工艺的边沿触发器有更强的抗干扰能力和更高的工作速度。

功能描述

2.特征方程 Qn+1=D

3状态转移图

脉冲特性:

1.建立时间:由下图维持阻塞触发器的电路可见,CP信号是加到门G3和G4上的,因而在CP上升沿到达之前门G5和G6输出端的状态必须稳定地建立起来。

输入信号到达D端以后,要经过一级门电路的传输延迟时间G5的输出状态才能建立起来,而G6的输出状态需要经过两级门电路的传输延迟时间才能建立,因此D端的输入信号必须先于CP的上升沿到达,而且建立时间应满足: tset≥2tpd。

2.保持时间:由下图可知,为实现边沿触发,应保证CP=1期间门G6的输出状态不变,不受D端状态变化的影响。

为此,在D=0的情况下,当CP上升沿到达以后还要等门G4输出的低电平返回到门G6的输入端以后,D 端的低电平才允许改变。

因此输入低电平信号的保持时间为tHL≥tpd。

在 D=1的情况下,由于CP上升沿到达后G3的输出将G4封锁,所以不要求输入信号继续保持不变,故输入高电平信号的保持时间tHH=0。

3.传输延迟时间:由图工作波形图不难推算出,从CP上升沿到达时开始计算,输出由高电平变为低电平的传输延迟时间tPHL和由低电平变为高电平的传输延迟时间tPLH分别是:tPHL=3tpd tPLH=2tpd

维持和阻塞D触发器的电路和动态波形

4.最高时钟频率:为保证由门G1~G4组成的同步RS触发器能可靠地翻转,CP高电平的持续时间应大于 tPHL,时钟信号高电平的宽度tWH应大于tPHL。

而为了在下一个CP上升沿到达之前确保门G5和G6新的输出电平得以稳定地建立,CP低电平的持续时间不应小于门G4的传输延迟时间和tset之和,即时钟信号低电平的宽度tWL≥tset+tpd,因此得到:

在实际集成触发器中,每个门传输时间是不同的,并且作了不同形式的简化,因此上面讨论的结果只是一些定性的物理概念。

其真实参数由实验测定。

综上所述,对边沿D触发器归纳为以下几点:

1.边沿D触发器具有接收并记忆信号的功能,又称为锁存器;

2.边沿D触发器属于脉冲触发方式;

3.边沿D触发器不存在约束条件和一次变化现象,抗干扰性能好,工作速度快。