1.从好用来说,肯定是Xilinx的好用,不过Altera的便宜

- 格式:doc

- 大小:138.50 KB

- 文档页数:6

fpga芯片的种类FPGA芯片的种类FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它具有灵活可塑性和高性能,被广泛应用于数字电路设计和嵌入式系统开发领域。

随着技术的不断发展,FPGA芯片也呈现出多样化的种类和功能,本文将介绍几种常见的FPGA芯片。

1. Xilinx Virtex系列Xilinx Virtex系列是业界最强大的FPGA产品系列之一。

它以其卓越的性能和丰富的资源而受到广泛关注。

Virtex系列采用了最新的FPGA架构,具有高达数百万个可编程逻辑单元(LUT)和丰富的高速IO接口,可满足复杂系统设计的需求。

此外,Virtex系列还提供了丰富的硬核IP(Intellectual Property),如处理器核、高速串行收发器等,使其在高性能计算和通信领域具有重要应用。

2. Altera Cyclone系列Altera Cyclone系列是一种低成本、低功耗的FPGA芯片,广泛用于嵌入式系统和消费电子产品中。

Cyclone系列采用了先进的工艺技术,具有较高的逻辑密度和丰富的资源。

该系列芯片在功耗控制上表现出色,可满足对低功耗需求较高的应用场景。

Cyclone系列还支持多种外围接口和通信协议,如CAN、SPI、I2C等,方便与其他设备进行通信和互联。

3. Lattice iCE系列Lattice iCE系列是一种超低功耗的FPGA芯片,适用于移动设备和便携式电子产品。

iCE系列采用了极小的封装和低功耗设计,能够在极端环境下提供可靠的性能。

该系列芯片具有快速启动和低功耗特性,适合应用于电池供电的场景。

iCE系列还具有较高的集成度和资源利用率,可满足对系统复杂度和成本要求较高的应用。

4. Intel Stratix系列Intel Stratix系列是一种高性能、高密度的FPGA芯片,由英特尔(Intel)公司推出。

Stratix系列采用了英特尔的最新工艺技术,具有卓越的性能和可靠性。

高级篇:第2章altera器件高级特性与应用展开全文高级篇:第2章 altera器件高级特性与应用发布时间:2010-06-23 16:09:11主要内容:. 时钟管理;. 片内存储器;. 数字信号处理;. 片外高速存储器;. 高速差分接口和DPA;. 高速串行收发器。

2.1 时钟管理分析设计中经常遇到的时序问题,介绍如何利用altera的时钟资源和PLL来有效地管理时钟,解决设计中的时序问题。

时序问题:时钟偏斜(skew)和抖动(jitter)时钟偏斜skew是指在时钟分配系统中各个时钟末端(器件内部触发器的时钟输入端)的时钟相位不一致的现象,是同一时钟源分不到不同时钟目的端的延时差。

主要由两个原因造成:一是时钟源之间的偏差,例如同一个PLL所输出的不同的时钟信号之间的偏斜;另一个是时钟分配网络的偏斜。

时钟偏斜是永远存在的,但是其大到一定程度,就会严重影响设计的时序,因此需在设计中尽量减小其影响。

时钟抖动是指时钟边沿的输出位置和理想情况存在一定的误差, 理想的时钟周期与实际的时钟周期的差别。

抖动一般可以分为确定性抖动和随机抖动,确定性抖动一般比较大,而且可以追踪到特定的来源,如信号噪声、串扰、电源系统和其他类似的来源;随机抖动一般是由环境内的因素造成的,如热干扰和辐射等,往往难以追踪。

实际环境中任何时钟都存在一定的抖动,而当时钟的抖动大到影响设计时序时就不可接受,应予以减弱。

时序余量(Timing Margin):在一个同步设计中,可以说时序决定一切。

在设计内部的时序余量时,工程师通常会考虑的一些延时因素是:源触发器的时钟到输出延时MicroTco,触发器到触发器的走线延时Tlogic,目的触发器的建立时间MicroTsu和保持时间MicroTh。

假设设计规格需要跑的时钟周期为T,因此需要满足时钟建立的要求:MicroTco + Tlogic +MicroTsu <= T同时也需要满足目的端触发器的保持时间MicroTh要求。

fpga芯片价格FPGA(Field-Programmable Gate Array)是一种集成电路芯片,可以根据用户的需求进行灵活的重构。

它不同于传统的固定功能集成电路,可以通过编程来实现特定的功能,因此被广泛应用于数字电路设计和嵌入式系统开发中。

FPGA芯片的价格因品牌、规格和性能等因素而异。

一般而言,FPGA芯片的价格较高,但随着市场竞争的激烈以及技术的发展,价格也在逐渐下降。

下面将从几个主要厂商的角度介绍FPGA芯片的价格。

1. Xilinx(赛灵思)是全球最大的FPGA厂商之一,其FPGA芯片价格相对较高。

例如,赛灵思最新推出的Versal ACAP系列(Adaptive Compute Acceleration Platform)芯片,价格从数千美元到几万美元不等。

不同配置的芯片具有不同的性能和功能,价格也相应不同。

2. Altera(英特尔)是另一家重要的FPGA厂商。

其FPGA芯片价格也较高。

例如,英特尔的Arria 10系列FPGA芯片,根据配置和性能的不同,价格从数千美元到几万美元不等。

3. Microchip Technology Inc.是一家全球领先的半导体解决方案供应商,其FPGA芯片的价格相对较低。

例如,Microchip的SmartFusion2系列FPGA芯片,价格从几十美元到数百美元不等。

这些芯片具有较低的功耗和较高的可编程逻辑资源。

4. Lattice Semiconductor是一家专注于低功耗FPGA和CPLD(Complex Programmable Logic Device)的厂商,其FPGA芯片价格一般较低。

例如,Lattice的ECP5系列FPGA芯片,价格从几十美元到数百美元不等。

另外,FPGA芯片的价格还会受到市场需求、供应情况和技术进步等因素的影响。

随着市场对FPGA的需求增加,厂商为了提高竞争力常常会降低价格。

此外,新一代的FPGA技术也会不断推动价格下降。

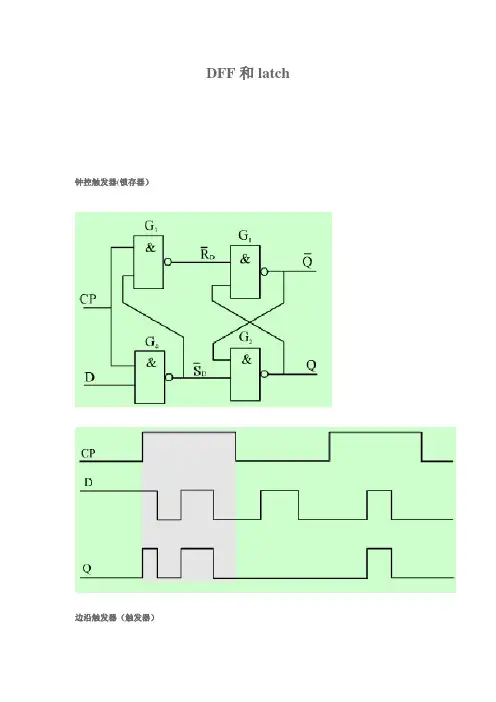

DFF和latch 钟控触发器(锁存器)边沿触发器(触发器)触发器:flipflop,锁存器:latch,寄存器:register锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

触发器是边沿敏感的存储单元,数据存储的动作有某一信号的上升或者下降沿进行同步的。

寄存器用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。

其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。

寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。

触发器是在时钟的沿进行数据的锁存的,而锁存器是用电平使能来锁存数据的。

所以触发器的Q输出端在每一个时钟沿都会被更新,而锁存器只能在使能电平有效器件才会被更新。

有一些教科书里的触发器实际是锁存器。

在FPGA设计中建议如果不是必须那么应该尽量使用触发器而不是锁存器。

钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器,钟控D触发器在使能情况下输出随输入变化,边沿触发器只有在边沿跳变的情况下输出才变化。

20、D 触发器和D 锁存器的区别。

两个锁存器可以构成一个触发器,归根到底还是dff是边沿触发的,而latch是电平触发的。

锁存器的输出对输入透明的,输入是什么,输出就是什么,这就是锁存器不稳定的原因,而触发器是由两个锁存器构成的一个主从触发器,输出对输入是不透明的,必须在时钟的上升/下降沿才会将输入体现到输出,所以能够消除输入的毛刺信号。

21、latch和filp-flop的异同都是时序逻辑,但latch受所有的输入信号控制,只要输入信号变化,latch就变化。

也正因为如此,latch很容易出毛刺。

flip-flop是触发器,只有在被时钟触发时才采样当前的输入,产生输出。

如果使用门电路来搭建latch和ff,则latch消耗的门资源比ff要少。

关于altera系列软件的破解心得由于本人要写一个用DSP builder做的论文。

所以就用到了QuartusII 9.0+ MATLAB 7.6(R2008a)+ DSP Builder 9.0,这几个是最核心的部件。

以前装过,都是看似破解了,但编译的时候总是报错,弄得很烦人。

不过进过几次试探,终于把这个头疼的问题解决了。

我破解步骤弄完了,用DSP builder里给的范例模型编译试过了。

报表基本上是绿色(正常),少数蓝字(一些warning,可以忽略的),没有红字(error)。

先说一下破解步骤:1.首先下载这些版本的原始安装程序,注意版本匹配的。

我都用的是跟9.0版本相配的。

破解器可以在CSDN上找,很多都能用的。

2.先安装MTALAB。

这个很简单,一般的安装ISO里都给了序列号。

养成习惯,装好软件之后,写一个hello world小程序,编译,运行,看能不能运行。

如果能顺利通过,那么90%情况下就说明安装成功了。

3.安装QuartusII 9.0,点安装包,最好装在一个简单的根目录下,例如D:\altera\90。

安装流程完成之后,如果你启动QII 90它会提示你加载licence.dat。

等下再说。

4.然后是重要部分,就是QII 90系列的crack了。

在网上有很多,zip里面不仅仅有QII 的破解程序,还带有DSP builder和ModelSim的破解补丁。

先把QII 90的破解程序exe解出来,放到D:\altera\90\quartus\bin 中,这个破解器是破解这个文件夹里面的sys_cpt.dll 和quartus.exe两个文件。

(友情提示,先备份这两个文件,复制,粘贴到另外一个空文件夹里。

如果它本身有自动备份,可以不管)然后点击启动,应用补丁。

然后会弹出一个对话框要设置licence.dat的路径,我就直接放在D:\altera下面。

用记事本打开这个licence.dat,可以看到里面有两段以FEATURE开头文字,以及里面HOSTID的字段,后面有XXXXXX的字样。

【转】Xilinx和Altera的FPGA的对⽐Xilinx和Altera的FPGA的对⽐[原创⽂章,转载请注明出处tengjingshu]⽼板布置了⼀个任务:搞⼀个符合要求的DDS(直接数字频率合成),其中要求DDS存储波形的ROM地址要48位,天啊,这可是2的48次这么多个byte,FPGA有这么多空间吗?于是我就⽐较了⼀下Xilinx和Altera的FPGA逻辑资源。

(其实DDS中存储波形数据的ROM地址为没必要搞到48位,正弦波形间隔两位的数据差不了多少可以省了很多步长,加上其实只要存储1/4正弦波波形的数据既可,所以地址位可以减少到12位)。

要⽐较Xilinx和Altera的FPGA,就要清楚两个⼤⼚FPGA的结构,由于各⾃利益,两家的FPGA结构各不相同,参数也各不相同,但可以统⼀到LUT(Look-Up-Table)查找表上。

关于两家FPGA的结构,可以参考:1.2.我师姐⽤的是Altera的Cyclone II系列的EP2C35,我⽤的是Xilinx的Spartan-3E系列的XC3S500E。

可以参考Datasheet。

Cyclone IISpartan-3E其中Altera的LEs和Xilnx的CLB(Slice)【其中1 Slices="1" CLB】对应于LUT的结构。

Altera从LEs的结构可以知道 1 LEs = 1 LUTXilinx下图是1 Slice的结构,从Slice的结构可以看到1 Slice = 2 LUT =4 CLB从⽽可以知道Xilinx和Altera FPGA逻辑资源的对应关系:(为了统⼀度量衡(感觉像QSH⼀样),业界⼀般会归结到BLM(Basic Logic Module)1 BLM=1 LUT4(四输⼊查找表)+DFF(D触发器)1 BLM=0.5 Slice(Xilinx)=1 LE(Altera)=2.25 Tile(Actel)于是就可以知道Altera的Cyclone II系列的EP2C35有33216个LUT,我⽤的是Xilinx的Spartan-3E系列的XC3S500E有9312个LUTL 呜呜……加上EP2C35还有4个PLL,我的XC3S500E就跟⽐不上了参考资料:1. Altera Cyclone II系列⼿册 2. Xilinx Spartan-3E系列⼿册 3. 【器件求助】XILINX FPGA 和 ALTERA FPGA在逻辑单元是怎么算的? 4. PLD/FPGA 结构与原理初步5. xilinx和Altera的fpga對⽐?6. 做个⼩调查,Xilinx的Spartan-3和Altera的MAX II,哪个⽤的更多? 7. Altera/Xilinx FPGA逻辑门计算 8. 【EDA技术】第⼆章 FPGA/CPLD的结构与应⽤(⼀)9. 【EDA技术】第⼆章 FPGA/CPLD的结构与应⽤(⼆)。

altera芯片命名规则Altera芯片命名规则Altera公司是一家专业从事可编程逻辑器件(FPGA)和复杂可编程逻辑器件(CPLD)的设计、制造和销售的公司。

其产品广泛应用于通信、计算机、工业控制、汽车电子等领域。

在Altera公司的产品中,芯片命名规则是非常重要的,本文将详细介绍Altera芯片命名规则。

1. 品牌名称Altera芯片品牌名称分为四个系列:Arria、Cyclone、Stratix和MAX。

其中Arria系列主要面向高性能应用,Cyclone系列主要面向低成本应用,Stratix系列主要面向高端应用,MAX系列主要面向高密度应用。

2. 芯片类型Altera芯片类型分为FPGA和CPLD两种。

FPGA是可编程逻辑器件,可以在设计完成后重新编程;CPLD是复杂可编程逻辑器件,相对于FPGA来说更加灵活和容易使用。

3. 芯片容量Altera芯片容量以LE(Logic Element)为单位进行计算。

LE是指一个可以实现任意逻辑功能的基本单元。

不同型号的芯片具有不同数量的LE。

4. 芯片速度等级Altera芯片速度等级以数字和字母组成的代码表示。

其中数字代表最大工作频率,字母代表芯片的性能等级。

例如,5SXTFPC2代表最大工作频率为500MHz,性能等级为SXT。

5. 芯片封装形式Altera芯片封装形式分为BGA、QFP、TQFP、LQFP等多种形式。

其中BGA是最常见的封装形式,也是最小的封装形式。

6. 其他标识Altera芯片还有一些其他的标识,例如温度范围、电压范围等。

这些标识通常以字母和数字组成的代码表示。

综上所述,Altera芯片命名规则包括品牌名称、芯片类型、芯片容量、芯片速度等级、芯片封装形式和其他标识等多个方面。

这些规则既有一定的规律性,又有一定的灵活性,在实际应用中可以根据具体需求进行选择和组合。

简谈Altera和Xilinx的FPGA区别大家好,又到了每日学习的时间了,最近有很多人再问我学习FPGA到底是选择Altera的还是xilinx的呢,于是我就苦口婆心的说了一大堆,中心思想大概就是,学习FPGA一定要学习FPGA的设计思想以及设计原理,不要纠结于单一的实验平台或者操作软件,因为你想在这个行业越走越高的话,广度和深度都是要有所了解的,初期学习的时候尤其注重动手,选择一款操作平台以及操作软件是为了让你更好的去动手做,而不是让你在这款软件或者实验平台去做文章,因为不懂原理的话,换个环境你同样是什么都不明白。

尤其是现在的科技公司产品更新升级换代还比较快,要学会去掌握最核心的知识点才是王道。

下面,就我自己接触,咱们就来简单聊聊Altera和Xilinx的FPGA 区别,欢迎大家一起交流,三人行,必有我师,共同学习,共同进步。

对于Altera和Xilinx 的FPGA,本人认为可以分为两个方面去比较一下,基本逻辑资源和内部基本架构。

从目前企业中做开发使用的广泛性来说,Xilinx占得比重确实是大一些,但是从其他方面来说,比如价格,相对而言Altera的便宜些。

对于两者的特点,Xilinx的短线资源非常丰富,这样在实现的时候,布线的成功率很高,尤其是逻辑做得比较满的时候。

而Altera的FPGA 的短线资源经常不够用,经常要占用LE来充当布线资源,这也是为什么Altera的FPGA 可以便宜的原因,资源少些当然便宜,但是如果你是高手,也能把他的性能发挥得很好。

另外就是关于块RAM,Xilinx的双口RAM是真的,Altera的没有双口RAM,如果你要实现真正的双口RAM,只能用两块RAM来背靠背地实现,这样你的RAM资源就少了一半,如果你的应用对片内双口RAM的需求很重要,用Altera的就划不来。

下面咱们就从我刚才说的基本逻辑资源和内部基本架构这两个方面来聊聊。

1.基本逻辑资源基本的逻辑资源我建议大家可以去看看两家的芯片做个比较,今天时间有限就不给各位详谈了,通过比较你会发现我上面说的还是有点道理的。

FPGA经典笔试题+答案1、FPGA结构一般分为三部分:可编程逻辑块(CLB)、可编程I/O模块和可编程内部连线。

2 CPLD的内部连线为连续式布线互连结构,任意一对输入、输出端之间的延时是固定;FPGA的内部连线为分段式布线互连结构,各功能单元间的延时不定(不可预测)。

3 大规模可编程器件主要有CPLD和FPGA两类,其中CPLD通过可编程乘积项逻辑实现其逻辑功能。

基于SRAM的FPGA器件,每次上电后必须进行一次配置。

FPGA内部阵列的配置一般采用在电路可重构技术,编程数据保存在静态存储器(SRAM) ,掉电易失。

4 目前世界上有十几家生产CPLD/FPGA的公司,最大的两家是:Altera,Xilinx。

5 硬件描述语言(HDL)是EDA技术的重要组成部分,是电子系统硬件行为描述、结构描述、数据流描述的语言,它的种类很多,如VHDL、Verilog HDL、 AHDL6 WHEN_ELSE条件信号赋值语句和 IF_ELSE顺序语句的异同WHEN_ELSE条件信号赋值语句中无标点,只有最后有分号;必须成对出现;是并行语句,必须放在结构体中。

IF_ELSE顺序语句中有分号;是顺序语句,必须放在进程中7 可编程逻辑器件设计输入有原理图输入、硬件描述语言输入和波形输入三种方式。

原理图输入方式是一种最直接的设计描述方式,硬件描述语言的突出优点是:* 语言与工艺的无关性;语言的公开可利用性,便于实现大规模系统的设计; * 具有很强的逻辑描述和仿真功能,而且输入效率高,在不同的设计输入库之间的转换非常方便,用不着对底层的电路和PLD结构的熟悉。

波形设计输入适用于时序逻辑和有重复性的逻辑函数。

8 用VHDL/Veilog HDL语言开发可编程逻辑电路的完整流程:文本编辑→功能仿真→逻辑综合→布局布线→时序仿真。

* 所谓综合,就是根据设计功能和实现该设计的约束条件(如面积、速度、功耗和成本等),将设计输入转换成满足要求的电路设计方案,该方案必须同时满足与其的功能和约束条件。

EDA复习资料《EDA技术基础》题库及参考答案(试用版)目录一、填空题 (I)二、单选题 (4)三、简答题 (10)四、应用题 (11)五、上机实验题 (15)一、填空题1.现代电子技术经历了CAD 、CAE 和EDA 三个主要的发展阶段。

2.EDA技术包括大规模可编程器件、硬件描述语言HDL 、EDA工具软件和实验开发系统四大要素。

3.EDA的设计输入主要包括文本输入方式、图形输入方式和波形输入方式三种形式。

4.目前已经成为IEEE标准、应用最为广泛的硬件描述语言有VHDL 和Verilog HDL 。

仿真是一种对所设计电路进行间接检测的方法,包括_ 功能仿真和_ 时序仿真。

5.层次化设计是将一个大的设计项目分解为若干个子项目或若干个层次来完成的。

先从底层的电路设计开始,然后在___高层次___的设计中逐级调用低层次的设计结果,直至实现系统电路的设计。

6.用HDL设计的电路,既可以被高层次的系统调用,成为系统的一部分,也可以作为一个电路的功能块独立存在和独立运行____。

7.可编程逻辑器件从结构上可分为乘积项结构器件和查找表结构器件。

8.PLD(FPGA、CLPD)种类繁多,特点各异。

共同之处包括的三大部分是逻辑块阵列、输入/输出块和互连资源。

9.FPGA两类配置下载方式是主动配置方式和被动配置方式。

10.Quartus II是EDA器件制造商Altera公司自己开发的___EDA工具___软件。

11.Quartus II工具软件安装成功后、第一次运行前,还必授权。

12.Q uartus II支持原理图、__文本和波形等不同的编辑方式。

13.在Quartus II集成环境下,设计文件不能直接保存在计算机磁盘根目录中,因此设计者在进入设计之前,应当在磁盘根目录中建立保存设计文件的工程目录(文件夹)。

14.在Quartus II集成环境下执行原理图输入设计法,应选择___模块/原理图文件(Block Diagram/Schematic File ).__方法,设计文件的扩展名是__ .bdf_______。

ASIC与FPGA比较谈专用集成电路(ASIC)采用硬接线的固定模式,而现场可编程门阵列(FPGA)则采用可配置芯片的方法,二者差别迥异。

可编程器件是目前的新生力量,混合技术也将在未来发挥作用。

与其他技术一样,有关ASIC技术过时的报道是不成熟的。

新的ASIC产品的数目可能有大幅度下降,但其销售额仍然相当高,尤其是在亚太区。

此外,采用混合式方法,如结构化ASIC,也为该技术注入了新的活力。

同时,FPGA(和其他可编程逻辑器件)也在发挥作用,赢得了重要的大众市场,并从低端应用不断向上发展。

每种技术都有它的支持者。

一般来说,ASIC用于大型项目,而对于需要快速投放市场且支持远程升级的小型项目,FPGA则更为适合。

ASIC和FPGA供应商对这两种技术孰优孰劣不能达成共识,对适合的应用领域也持不同看法。

上述技术及其衍生技术将可能在今后一段时间内长期存在。

Altera Corp的高密度FPGA高级总监David Greenfield指出,FPGA技术的主要优势仍是产品投放市场的时间较短。

他说:“在目前新增的设计方案中,对FPGA的选择倾向超过ASIC。

ASIC技术有其价值所在,它的性能、密度和单位容量都相当出色,不过随着FPGA的发展和ASIC的开发成本不断上升,将会导致ASIC的市场份额不断缩小。

”在上述趋势之后发挥作用的,正是FPGA在性能、密度和制造成本上的发展。

Greenfield指出,高性能曾经是ASIC超出FPGA的优势,当时FPGA在性能和功能上都较逊色。

随着芯片的制造工艺从180nm发展到130nm甚至90nm,上述情况发生了很大变化,现在FPGA的性能已经能够满足大多数应用的需要(要求最高的应用除外),而密度水平则达到逻辑设计的80%。

他解释说:“某些系统设计师也认识到,ASIC的市场领域在于极高性能/密度的产品,这种市场领域风险非常大。

NRE (非重复性工程设计)和开发成本对这种设备而言是最高的。

⽐较Altera与Xilinx带ARM处理器的FPGA哪个更好?如今FPGA开始带ARM处理器了。

赛灵思(Xilinx)的称作可扩展处理平台,取名Zynq;Altera的称作集成ARM处理器的SoC FPGA。

今年3⽉份,赛灵思推出Zynq;今年10⽉份,Altera推出集成ARM处理器的SoC FPGA。

两家公司的产品⾮常类似。

两者都是集成ARM Cortex-A9 MPCore 双核处理器的SoC,都采⽤28纳⽶⼯艺,都在台积电⽣产。

它们的⽬标应⽤领域也都是视频监视、汽车驾驶员辅助以及⼯⼚⾃动化(⼯业驱动)。

那么,它们之间有什么不同呢?Altera公司产品及企业市场副总裁Vince Hu先⽣总结出以下⼏点不同:1. FPGA与处理器之间的互联(AXI总线)带宽,Altera的SoC FPGA较Xilinx的Zynq有所提升,⼤约是Zynq的两倍带宽。

这样整个芯⽚的性能会更好。

2. Altera的产品更丰富,有两个系列:Cyclone V和Arria V SoC FPGA。

两个不同产品系列针对不同的应⽤,⽤户在功能与价格上⾯有更多的选择。

3. 两家虽然都是由台积电代⼯,但所采⽤的⼯艺有所不同。

Altera选⽤的是LP ⼯艺(lowpower,即低功耗),这样对产品的功耗跟价格⽅⾯会有所缓解。

4. Altera推出的虚拟⽬标软件可提升软件开发⼯程师的效率,把他们的开发时间降到最低。

5. Altera的SoC FPGA的存储器的控制提供 ECC,即纠错码功能,可以满⾜对数据完整性的⾼的需求。

不过赛灵思不以为然。

赛灵思亚太区市场及应⽤总监张宇清说,Altera在步Xilinx的后尘,并完全模仿赛灵思的Zynq。

Zynq-7000 系列预计将于今年下半年推出,⽽Altera的产品需要⼀年之后。

⼯艺⽅⾯,赛灵思与台积电合作开发了HP-L(⾼性能、低功耗)⼯艺,芯⽚性能⽐LP⼯艺会更好,成本也不会显著提⾼。

1.问:Cyclone II系列器件是什么?答:Cyclone II系列器件是Altera低成本Cyclone系列的第二代产品,Cyclone II FPGA 的成本比第一代Cyclone 器件低30%,逻辑容量大3倍多。

Cyclone II器件采用TSMC 经验证的90nm 低K 绝缘材料工艺技术,是业界成本最低的FPGA。

Cyclone II器件容量有4608~68416个逻辑单元,还具有新的增强特性,包括多达1.1Mbit的嵌入存储器、多达150个嵌入18×18乘法器、锁相环、支持外部存储器接口及差分和单端I/O标准。

2.问:Cyclone II器件系列采用什么样的工艺技术?答:Cyclone II器件系列是采用TSMC的1.2V、90nm、低K 绝缘材料工艺。

3.问:Cyclone II器件系列满足了哪些市场的需求?答:Cyclone II器件系列是多种不同市场上大批量应用最优的低成本方案,包括消费电子、电信和无线、计算机外设、工业和汽车。

Cyc lone II器件包含了许多新的增强特性,如嵌入存储器、嵌入乘法器、PLL和低成本的封装,这些都为诸如视频显示、数字电视、机顶盒、DVD 播放器、DSL调制解调器、家用网关和中低端路由器等批量应用进行了优化。

4.问:为什么Cyclone II 器件是ASIC 理想的替代方案?答:Cyclone II系列提供了一种灵活的无风险的,且没有前期一次性工程费用或最小定货量的开发方式。

Cyclone II器件除了具有其它任何FPGA 无可匹敌的成本结构之外,还具有先进的特性,如用于高性能数字信号处理应用的嵌入式18×18乘法器和支持如DDR2(高达334Mbps)和QDRII(高达688Mbps)的存储器接口。

5.问:Cyclone II器件有哪些产品,提供哪些封装?答:Cyclone II系列包括6种器件,容量从4608~68416个逻辑单元。

FPGA技术正处于高速发展时期,新型芯片的规模越来越大,成本也越来越低,低端的FPGA已逐步取代了传统的数字元件,高端的FPGA不断在争夺AS IC的市场份额。

本节从FPGA软、硬件来展望未来的FPGA设计技术,给读者留一个FPGA技术的宏观轮廓。

1 未来可编程器件的发展趋势先进的ASIC生产工艺已经被用于FPGA的生产,越来越丰富的处理器内核被嵌入到高端的FPGA芯片中,基于FPGA的开发成为一项系统级设计工程。

随着半导体制造工艺的不同提高,FPGA的集成度将不断提高,制造成本将不断降低,其作为替代ASIC来实现电子系统的前景将日趋光明。

workcodi (1)大容量、低电压、低功耗FPGA大容量FPGA是市场发展的焦点。

FPGA产业中的两大霸主:Altera和Xili nx在超大容量FPGA上展开了激烈的竞争。

2007年Altera推出了65nm工艺的S tratixIII系列芯片,其容量为67200个L E (Logic Element,逻辑单元),Xilinx 推出的65nm工艺的VitexVI系列芯片,其容量为33792个Slices (一个Slices约等于2个L E)。

采用深亚微米(DSM)的半导体工艺后,器件在性能提高的同时,价格也在逐步降低。

由于便携式应用产品的发展,对FPGA的低电压、低功耗的要日益迫切。

因此,无论那个厂家、哪种类型的产品,都在瞄准这个方向而努力。

(2)系统级高密度FPGA随着生产规模的提高,产品应用成本的下降,FPGA的应用已经不是过去的仅仅适用于系统接口部件的现场集成,而是将它灵活地应用于系统级(包括其核心功能芯片)设计之中。

在这样的背景下,国际主要FPGA厂家在系统级高密度F PGA的技术发展上,主要强调了两个方面:FPGA的IP( Intellec2tual Property,知识产权)硬核和IP软核。

当前具有IP内核的系统级FPGA的开发主要体现在两个方面:一方面是FPGA厂商将IP硬核(指完成版图设计的功能单元模块)嵌入到FPGA器件中,另一方面是大力扩充优化的IP软核(指利用HDL语言设计并经过综合验证的功能单元模块),用户可以直接利用这些预定义的、经过测试和验证的IP核资源,有效地完成复杂的片上系统设计。

1.从好用来说,肯定是Xilinx的好用,不过Altera的便宜Altera的FPGA的短线资源经常不够用,经常要占用LE来充当布线资源〔这也是什么原因Altera的FPGA能够廉价的缘故,资源少些所以廉价〕,然而假如你是高手,也能把他的性能发挥得很好。

另外确实是关于块RAM,Xilinx的双口RAM是真的,Altera的没有双口RAM,假如你要实现真正的双口RAM,只能用两块RAM来背靠背地实现,如此你的RAM资源就少了一半,假如你的应用对片内双口RAM的需求很重要,用Altera的就划不来。

2.Xilinx与Altera FPGA比较系列之一逻辑资源速度一开始没想到那个比较会得到大伙的关注,纯粹是出于自己的兴趣。

两个厂商都会宣称自己某一方面比对方好,到底是谁的更好呢?这确信是个仁者见仁,智者见智的问题。

最近这段时间比较忙,项目到了比较关键的阶段,加上其他一些杂七杂八的情况,很难有比较完整的时间坐下来完成报告,直到今天才差不多把一些文档整理完。

在整理的过程中,越来越觉得很难比较两者之间的速度,因为相关的因素实在太多了。

软件的好坏,器件本身的延迟,设计等等对最优的速度都有着相当大的妨碍。

做速度比较用的滤波器很难代表其他的设计,确实是抛砖引玉,盼望能够和大伙一起讨论FPGA的速度那个问题。

在整理过程中,发明了许多很有趣的情况,比如StratixIII和StratixII的速度区别等。

为此,作者做了一些简单的实验,盼望能够找到合理的解释,来分析出现这些现象的缘故。

编译之前的考虑依照作者自己的一些经验,作者把常用的一些开关打开了,以便更好的优化速度。

另外,有一些选项作者拿不准是否两个软件都有相似的开关,就没有打开。

为了使得比较更加合理,作者尽可能选择门数和IO速度都比较接近的FPGA。

Xilinx采纳ISE9.1ServicePack1版本,Altera采纳Quartus7.1ServicePa ck1版本,Xilinx:Altera编译结果作者采纳了两种形式的滤波器来比较两者的速度。

第一种实现形式是57阶F IR滤波器,8比特输入数据,8比特输出数据,13比特系数,滤波器采纳转置形式的结构。

下面是得到的测试结果。

表1转置形式滤波器第二种实现方式是相同的滤波器,采纳直截了当形式的结构,乘完之后的数据按照四输入加法的方式求和。

下面是得到的测试结果。

表2直截了当形式滤波器一些简单的结论1. 从表1能够看出,Altera的FPGA运行速度快许多。

StratixII比V4的速度高出尤其多。

2. 表1,2的结果说明StratixIII的速度比StratixII的没有显著的增加。

Xilinx的V5比V4速度提升了许多。

3. 关于直截了当形式的FIR滤波器,一个有趣的现象是StratixII比V4快,然而V5比StratixIII快。

为了能够更好的理解造成这些差异的缘故,下面对两个公司的FPGA做进一步的分析。

首先,作者对32bit的加法在两个FPGA进行编译,比较两者的速度。

表132-bit加法器速度从上面的表格来看,Xilinx的V5比V4速度提高了许多,尤其是逻辑资源的加法器速度。

Xilinx的V5一位进位逻辑延迟为83ps,寄存器输出延迟为326ps,最低位加法延迟为318ps。

Xilinx的V4一位进位逻辑延迟为66ps,寄存器输出延迟为258ps,最低位加法延迟为433ps。

Altera的StratixIII比StratixII只提高了一些,然而并不是太大。

临时没有找到Altera的进位逻辑的延迟参数,S tratixII寄存器输出延迟为94ps,StratixIII为下面我们来看看乘法器的情况。

那个地方我比较了两种乘法器:两个输入可变〔下面称为可变乘法器〕,一个输入可变〔下面称为固定系数乘法器〕。

分别针对16bit和8bit情况做了比较,依旧采纳纯逻辑资源来实现上述运算。

关于一个输入可变的情况,另外一个数我用的是有符号数的最大值,即8bit的0x7F 和16bit的0x7FFF。

下面的一些表格给出了一些测试结果。

表2两个输入可变16bit乘法器表3一个输入可变16bit乘法器表4两个输入可变8bit乘法器表5一个输入可变8bit乘法器从以上的表格能够看出Altera的可变输入乘法器比Xilinx略微快一些。

固定系数乘法器比Xilinx速度高出许多〔由于Quartus优化的缘故,下面会专门分析〕。

Xilinx的V5比V4速度有了较大的提高,而StratixIII的速度比Str atixII没有明显的提高。

Quartus软件能够对固定系数乘法器做优化,比如与0x7F相乘,等价于先与0x080相乘,然后减去被乘数。

我使用了另外一个系数0x7D,结果发明速度明显下降,StratixIIIC2的最高速度只有253MHz,而占用的资源却增加许多。

因为这一点,也导致了在实现转置形式的FIR滤波器〔速度要紧局限在固定系数乘法器〕上,Altera不仅能够少用一部分资源,速度比Xilinx快许多。

上次的分析还剩下一点点尾巴,确实是查找直截了当形式滤波器XilinxV5比AlteraS3快的缘故。

在对直截了当形式的滤波器做比较时,发明Xilinx的V5比Altera的S3要快一些,时序分析报告显示关键路径在乘完之后的求和运算。

我单独把求和运算做了分析,下面是得到的结果。

奇怪的是这种情况下Xilinx的V5比Altera的S3要慢一些。

可能是其他缘故造成了上述的差别,今后再接着研究那个问题。

FPGAPlatform FPGAType Speed(MHz)Speed(MHz)FPGAType FPGAPlatform StratixIII EP3SE80F780C2 304 255 xc5vlx85-ff1153-3 Virtex5 StratixII EP2S90F1020C3 264 208 xc4vlx100-ff1148-12 Virtex4下一个系列接着研究直截了当形式和转置形式滤波器采纳DSP块的一些实现情况。

大伙明白,高端的FPGA中都有为数许多的DSP块,里边要紧包括一些18X18的乘法器,以及加法器等单元,相邻的DSP往往能够通过专用的连线互连,从而实现滤波器的级联设计,提高滤波器的运行速度。

Xilinx和Altera的DSP块有所差别,Xilinx的DSP模块能够做18X18乘法,18X18乘累加运算,18X18乘加运算等,其中累加器能够到48位宽,厂家标称的最高速度位500MHz。

Altera的DSP块能够分解成为8X8,16X16,32X32块,能够完成乘法,乘累加,乘加等运算,厂家标称的最高速度为450MHz。

下面的表格给出了一些综合结果。

FPGAPlatform FPGAType Speed(MHz)Speed(MHz)FPGAType FPGAPlatformStratixII EP2S90F1020C3313165xc4vsx35-ff668-12Virtex4 EP2S90F1020C4282154xc4vsx35-ff668-11EP2S90F1020C5240124xc4vsx35-ff668-1FPGAPlatform FPGAType Speed(MHz)Speed(MHz)FPGAType FPGAPlatformStratixII EP2S90F1020C3195109xc4vsx35-ff668-12Virtex4 EP2S90F1020C4169101xc4vsx35-ff668-11EP2S90F1020C514188xc4vsx35-ff668-1一些简单的分析:1、Xilinx之因此速度比Altera慢一个缘故可能是ISE综合时可能需要加一些约束才能够达到最正确状态,就这件情况我曾经咨询过Xilinx的应用工程师,她给了我一个使用Synplify综合的结果,速度明显比我使用ISE的好许多。

2、有关Xilinx的DSPBlock,我还试了许多其他的模块,包括简单的乘法器等,然而都不能达到器标称的500MHz,另外,ISE不能支持随意的写法,对代码的风格有一定的要求,比如,需要写成同步reset,如此才能被综合到DSPBlock当中。

首先,Xilinx和Altera的FPGADSP功能差不多相同,两者差不多上能够实现相近的功能.比较小的差别是,Xilinx的DSP模块能够在模块内做乘累加运算,而Altera的必须借助逻辑资源实现.另外,两者的速度有所区别,XilinxV4标称最高速度为500MHz,而AlteraS2标称最高速率为450MHz. 在实际使用过程当中,厂商的参数当然重要,然而用户的使用对性能的妨碍也是特别大的.我在Altera 的S2C3上用综合工具自动识别*,以及调用IPcore,发明两者的结果一致,关于16X16的乘法器速度是367.65MHz,关于8X8乘法器的速度是375.94MHz.Altera 的IPcore对流水线的支持相对较少,只有2级.Xilinx综合工具大概并没有那么智能,只能把*识别出来,用IPcore的0级流水线替代,而不能将乘法后跟随的一级流水线自己吸收到IPcore中.只是Xilinx的乘法器提供了18级流水线选择,因而采纳IPcore例化实现的乘法器速度大大的提升.我做的一个结果(V4-12),采纳综合工具infer出乘法器的速度是189MHz,而采纳IPcore例化的方法实现的为260MHz和611MHz,分别对应一级流水线和两级流水线结构.从以上实验结果以及笔者的使用经验来看,大概Altera的软件的智能程度稍高一些,然而Xilinx的硬件功能更强.在本例子当中,通过例化IPcore,能够大大提高乘法器的速度.假如采纳Xilinx的FPGA,在项目前期时能够采纳综合工具infer,留两级流水线待今后例化IPcore使用,如此一方面能够达到原型平台的快速开发,用能够保证以后性能的改进和提高.而采纳altera的FPGA,大概软件差不多解决了以上问题,利用IPcore例化的效果并不明显.。