时序及面积约束

- 格式:pdf

- 大小:127.16 KB

- 文档页数:20

时序约束的概念

时序约束是指在设计和开发硬件或软件系统时,对于其中的各个元件或操作的时间关系的限制要求。

它用来确保系统在特定的时间范围内以期望的顺序和时间间隔进行操作。

时序约束在各个层面的设计中都有应用,包括电子电路设计、数字系统设计、通信协议设计等。

时序约束可以包括以下几个方面:

1.时钟频率和时钟沿:为了实现正确的操作顺序,时序约束会定义系统中的时钟频率和时钟沿的要求。

这可以保证各个元件在时钟信号的控制下按照预期的时序进行操作。

2. 时序延迟:时序约束可以规定不同元件或操作之间的最大或最小延迟要求。

这可以确保信号在指定的时间范围内到达目标元件,避免信号延迟导致的系统故障或性能下降。

3. 时序关系:时序约束可以定义不同元件或操作之间的时间关系,如顺序、并行和同步等。

这确保了系统在不同元件之间的通信和操作按照特定的时间顺序进行。

4. 时序约束检查:通过时序约束检查工具,可以对设计中的时序约束进行验证。

DC综合归纳总结Author:WJDate:Dec 11 2014 概述:●综合是将RTL源代码转换成门级网表的过程。

●电路的逻辑综合一般由三个步骤组成,即综合=转化+逻辑优化+映射(Synthesis=Translation+Logic Optimization+Mapping)●在综合过程中,优化进程尝试完成库单元的组合,使组合成的电路能最好地满足设计的功能、时序和面积的要求●综合是约束驱动(constraint driven)的,给定的约束是综合的目标。

约束一般是在对整个系统进行时序分析得到的,综合工具会对电路进行优化以满足约束的要求。

●综合以时序路径为基础进行优化。

(注意:电路中的cell,对于前一级是load,其电容越大负载能力越大;对于后一级是drive,其电阻越小驱动能力越大。

有:大器件大电容小电阻,小器件小电容大电阻)启动文件:1. search_path指定了综合工具的搜索路径。

2. target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。

3.synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

4. link_library是链接库,它是DC在解释综合后网表时用来参考的库。

一般情况下,它和目标库相同;当使用综合库时,需要将该综合库加入链接库列表中。

5. symbol_library为指定的符号库。

6. synlib_wait_for_design_license用来获得DesignWare-Foudation的许可(license)。

7. alias语句与UNIX相似,它定义了命令的简称。

8. 另外,在启动文件中用符号“/*” 和“*/” 进行注释。

时序约束的概念和基本策略时序约束的概念和基本策略引言在现代电子设计中,时序约束是一项至关重要的任务。

它是指在电路中确定各个信号之间的时间关系,以确保电路能够按照预期的方式运行。

时序约束涉及到许多方面,包括时钟分配、逻辑延迟、信号传输等等。

在本文中,我们将详细介绍时序约束的概念和基本策略。

一、时序约束的概念1.1 什么是时序?在电路设计中,时序指的是各个信号之间发生的时间顺序关系。

例如,在一个简单的计数器电路中,一个时钟脉冲会触发计数器加1操作。

如果这个操作完成后立即出现下一个脉冲,则会导致计数器计数错误。

因此,在这种情况下,需要对脉冲之间的时间进行限制。

1.2 什么是时序约束?时序约束是一种用于限制各个信号之间时间顺序关系的技术。

它可以确保电路按照预期方式运行,并且可以帮助设计人员避免一些常见问题,例如信号噪声、稳定性问题等。

1.3 为什么需要时序约束?在现代电子设计中,时序约束非常重要。

这是因为现代电路的速度非常快,信号传输时间非常短。

如果不对信号进行时序约束,则可能会导致一些问题,例如:- 信号噪声:由于信号传输时间非常短,因此可能会受到噪声的干扰。

通过时序约束可以确保信号在正确的时间到达目标设备。

- 稳定性问题:如果两个信号在错误的时间交错到达,则可能会导致电路不稳定。

通过时序约束可以确保各个信号之间的时间顺序关系正确。

1.4 时序约束的应用领域时序约束广泛应用于各种电子设计中,包括:- 高速数字电路设计- FPGA设计- ASIC设计- PCB布局和布线二、时序约束的基本策略2.1 了解器件特性在进行时序约束之前,必须了解所使用器件的特性。

这包括器件的逻辑延迟、输入输出延迟等参数。

这些参数对于确定各个信号之间的时间关系至关重要。

2.2 确定主频率和时钟分配主频率和时钟分配是确定各个信号之间时间关系的重要因素。

通过确定主频率和时钟分配,可以确保各个信号在正确的时间到达目标设备。

2.3 确定时序限制一旦了解了器件特性并确定了主频率和时钟分配,就可以开始制定时序限制。

Synopsys dc1.1 什么是DC?DC(Design Compiler)是Synopsys的logical synthesis优化工具,它根据design description和constraints自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和netlist等,并产生多种性能报告,在缩短设计时间的同时提高读者设计性能。

1.2 DC能接受多少种输入格式?支持.db, .v, .vhd , edif, .vgh等等,以及.lib等相关格式。

1.3 DC提供多少种输出格式?提供.db, .v, .vhd, edif, .vgh等,并可以输出sdc, .sdf等相关格式文件。

1.4 DC的主要功能或者主要作用是什么?DC是把HDL描述的电路综合为跟工艺相关的门级电路。

并且根据用户的设计要求,在timing和area,timing和power上取得最佳的效果。

在floorplanning和placement和插入时钟树后返回DC进行时序验证1.5 如何寻找帮助?帮助可以用3种求助方式:1. 使用SOLD,到文档中寻求答案2. 在命令行中用man+ DC命令3. 在命令行中用info+ DC命令1.6 如何找到SOLD文档?SOLD文档可以在teminal中输入sold&执行。

$> sold&或者用命令which dc_shell找到dc的安装目录。

找到online目录。

1.7 如何配置DC?综合设置提供必要的参数给DC,使工具能够知道进行综合时所需要的必要的信息,即重要参数:工艺库,目标库,标志库等等。

要在.synopsys_dc.setup上设置好这些参数。

而.synopsys_dc.setup要在三个目录下有说明,一个是synopsys的安装目录,一个是用户文件夹,最后一个是工程目录。

由后一个设置覆盖前一个文件。

参数包括:search_path, target_library, link_library, symbol_library1.8 target_library 是指什么?target_library是在synthesis的map时需要的实际的工艺库1.9 link_library如何指定?链接时需要的库,通常与library相同,设置时,需要加“*”,表示内存中的所有库。

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

什么是DC?DC(Design Compiler)是Synopsys公司的logical synthesis工具,它根据design description和design constraints自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如HDL、Schematics、Netlist等,并能生成多种性能report,在reducing design time的同时提高了设计的性能。

DC能接受多少种输入格式支持.db、.v、.vhd、.edif、.vgh、.lib等,.db一般是厂商的单元库;.v是veilog的后缀;.vhd是VHDL的后缀;.edif 和.vhd是两种形式的netlist。

DC提供多少种输出格式提供.db、.v、.vhd、edif、.vgh等,并可以输出sdc、sdf等相关格式文件。

DC的主要功能或者主要作用是什么DC是把HDL描述的电路综合为跟工艺相关的门级电路。

并且根据用户的设计要求,在timing、area、power上取得最佳的效果。

在floorplanning和placement和插入时钟树后返回DC进行时序验证。

如何寻找帮助帮助可以用3种求助方式:1. 使用SOLD,到文档中寻求答案2. 在命令行中用man+ DC命令(我最喜欢这种)3. 在命令行中用info+ DC命令如何找到SOLD文档SOLD文档可以在teminal中输入sold&执行。

$> sold&或者用命令which dc_shell找到dc的安装目录。

找到online目录。

如何配置DC综合设置提供必要的参数给DC,使工具能够知道进行综合时所需要的必要的信息,如:工艺库,目标库,标志库等等。

要在.上设置好这些参数。

而.要在三个目录下有说明,一个是synopsys的安装目录,一个是用户文件夹,最后一个是工程目录。

由后一个设置覆盖前一个文件。

具体参数包括:search_path, target_library, link_library, symbol_librarytarget_library 是指什么target_library是在synthesis的map阶段时需要的实际的工艺库。

芯片设计后端知识点芯片设计的后端阶段是一个非常重要的环节,它涉及到芯片的物理实现和验证。

在这个阶段,设计工程师需要熟悉一系列关键的知识点,以确保芯片的性能、功耗和可靠性等方面得到有效的优化。

本文将介绍几个与芯片设计后端相关的重要知识点。

一、物理实现物理实现是芯片设计的核心环节,它包括了门级综合、布局布线和时序分析等步骤。

1. 门级综合门级综合是将逻辑门级的RTL描述转化为门级网表的过程,其目的是为了将逻辑电路实现为具体的门级电路。

在门级综合过程中,需要考虑到电路延时、功耗和面积等因素,以达到设计的性能指标。

2. 布局布线布局布线是将门级网表转化为物理结构的过程,包括将逻辑电路布置在芯片上,并且进行电路的连线。

布局布线的目标是最小化电路面积,同时保证电路的正常工作。

3. 时序分析时序分析主要是为了确保电路在不同的时钟周期下能够正确工作。

在时序分析中,需要考虑到时钟信号的传输延迟、电路中的时序约束等因素。

通过时序分析,可以预测电路的性能和稳定性。

二、功耗优化功耗是芯片设计中一个非常重要的指标,尤其是在移动设备和低功耗应用中。

在芯片设计的后端阶段,需要采取一系列的措施来对功耗进行优化。

1. 时钟树设计时钟树是芯片中用于分发时钟信号的网络。

设计工程师需要通过合理的时钟树设计,减少时钟信号的传输延迟,从而降低功耗。

2. 电源网设计电源网是芯片中用于供电的网络。

设计工程师需要通过合理的电源网设计,减小供电噪声和功耗损耗,以提高芯片的可靠性和效率。

3. 功耗分析和优化在物理实现的过程中,需要进行功耗分析,以确定芯片的功耗情况,并采取相应的措施进行优化。

例如,通过减少电流泄漏、优化电路结构等方式来降低功耗。

三、时序约束时序约束是芯片设计中的重要指导,它规定了电路中各个信号的时序关系,确保电路能够按照指定的时钟周期进行工作。

1. 输入输出延迟时序约束中需要考虑到输入输出的延迟情况,即在输入信号发生变化后,相应输出信号需要在指定的时间内出现。

武汉大学电工电子实验教学示范中心集成电路设计实验实验报告电子信息学院电子信息工程专业2014 年 5 月 2 日实验名称逻辑综合(DC工具)实验指导教师姓名江燕婷年级2011级学号2011301200025 成绩一、预习部分1.实验目的(预期成果)2.实验基本原理(概要)3.主要仪器设备(实验条件,含必要的元器件、工具)一、实验目的1.掌握综合的基本流程和Design Compile软件的使用2.对设计进行分块设计以获得更好的综合效果;3. 对设计进行时间约束的综合。

二、实验原理1.综合DC是把RTL级的代码转化为门级网表。

综合包括翻译,优化,映射三个步骤。

优化是基于所施加的一定时序和面积的约束条件,综合器按照一定的算法对翻译结果做逻辑优化和重组。

在映射过程中,根据所施加的一定的时序和面积的约束条件,综合器从目标工艺库总搜索符合条件的单元来构成实际电路。

2.时序与面积约束通过描述其设计环境,目标任务和设计规则来系统的约束设计。

约束主要包含时序和面积信息,它们通常是从规格说明中提取出来的。

DC用这些约束去综合和优化设计以符合其目标任务。

3.环境变量,设计规则和设计优化(1)设计环境条件约束的环境变量set_operating_conditions描述了设计的工艺、电压和温度等条件;set_load定义了输出单元总的驱动能力;set_driving_cell模拟了驱动输入管脚的驱动单元的驱动电阻;set_drive指明了输入管脚的驱动强度,模拟了输入管脚的外部驱动电阻;set_wire_load用来提供估计的统计线载(wire load)信息,反过来也用线载信息模拟net 延时。

(2) 设计规则set_max_transition,set_max_ capacitance,set_max_fanout 设计规则在技术库中设置,为工艺参数所决定。

set_max_transition <value> <object list>set_max_capacitance <value> <object list>set_max_fanout <value> <object list>三. 实验设备与软件平台基于UNIX 系统的服务器、PC 机(windows)、DC 综合软件二、实验操作部分1.实验数据、表格及数据处理(综合结果概要、仿真波形图、时序分析结果、signalTAPII 结果等)2.实验操作过程(可用图表示)3.结论四. 实验内容1. 对设计进行分块设计;2. 会用DC_tcl完成设计命令;3. 时间约束设计;4.环境属性设置和规则设计。

时序分析(2):时序约束原理⼀、基本概念1.时序:时钟和数据的对应关系2.约束:告诉综合⼯具,我们希望时序达到什么样的标准3.违例:时序达不到需要的标准4.收敛:通过调整布局布线⽅案来达到这个标准5.静态时序分析:电路未跑起来时,延时等已知,以此分析时序6.动态时序分析:电路跑起来,如Modelsim软件(理想状态)⼆、时序分析基本模型模型分为以下四种:(注:PAD指管脚)寄存器与寄存器之间输⼊PAD与寄存器之间寄存器与输出PA D之间输⼊PAD 与输出PAD之间(太极端,不讨论)知识补充:1、全局时钟:FPGA时钟到各个寄存器的时间⾮常接近。

2、⾃分频时钟:⾛的是数据线,到各个寄存器的时间差异⾮常⼤。

三、理想状态的建⽴时间和保持时间1、建⽴时间 Time setup(1) 接收时钟上升沿前,发送数据要准备好的时间(2) Tsu = 数据锁存沿(Latch)- 数据发送沿(Lanch)= 时钟周期2、保持时间 Time hold(1) 接收时钟上升沿后,发送数据要保持住的时间(2) Th = 发送端数据变化时 - 接收端数据锁存 = 03、补充(1) D触发器本⾝也有建⽴/保持时间的概念,称之为寄存器建⽴时间门限和寄存器保持时间门限,这是⼀个固有属性,是确定的、不变的。

当理想状态时,我们讨论建⽴/保持时间就相当于讨论D触发器的这⼀固有属性。

(2) FPGA所有时序问题,根本原因都是“建⽴时间和保持时间”的问题。

(3) 解决建⽴时间不⾜的⽅法是“减少延时”,⽽解决保持时间不⾜的⽅法是“增加延时”。

4、符号说明四、建⽴时间余量和保持时间余量Lunch edge:发射沿,以 clk_pad 为基准,⼀般看成 0 时刻。

实际时间是上⼀个寄存器所⽤的时间,因此⽤ clk1,看数据到达下⼀个寄存器的 D 端⽤了多久时间,结束时间⼜是多久。

Latch edge:接收沿,以 clk_pad 为基准,⼀般看成 0+Tcyc 时刻,要求时间是下⼀个寄存器计算的时间,所以⽤ clk2,看它⾃⾝需要的到达时间和结束时间是什么时候。

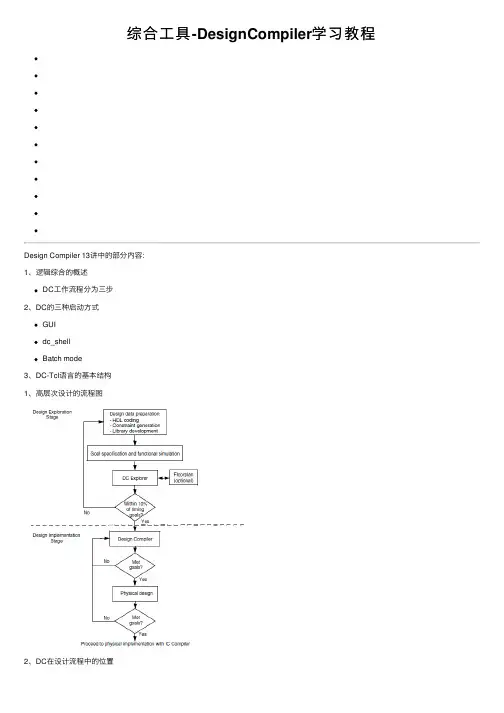

综合⼯具-DesignCompiler学习教程Design Compiler 13讲中的部分内容:1、逻辑综合的概述DC⼯作流程分为三步2、DC的三种启动⽅式GUIdc_shellBatch mode3、DC-Tcl语⾔的基本结构1、⾼层次设计的流程图2、DC在设计流程中的位置3、使⽤DC进⾏基本的逻辑综合的流程图与相应的命令①准备设计⽂件②指定库⽂件③读⼊设计④定义设计环境⑤设置设计约束⑥选择编译策略⑦编译⑧分析及解决设计中存在的问题⑨存储设计数据(1)启动环境配置简述(2).synopsys_dc.setup配置⽂件的书写(3).synopsys_dc.setup的讲解(1)标准单元库①概述⼀个ASIC综合库包括如下信息:·⼀系列单元(包括单元的引脚)。

·每个单元的⾯积(在深亚微⽶中,⼀般⽤平⽅微⽶表⽰,在亚微⽶⼯艺下,⼀般⽤门来称呼,⾄于具体的单位,可以咨询半导体制造商)。

·每个输出引脚的逻辑功能。

·每个输⼊到输出的传递延时,输出到输出的传递延时;inout到输出的传递延时。

②内容与结构Synopsys的⼯艺库是⼀个.lib⽂件,经过LC编译后,产⽣.db⽂件。

⼯艺库⽂件主要包括如下信息:·单元(cell)(的信息):(主要有)功能、时间(包括时序器件的约束,如建⽴和保持)、⾯积(⾯积的单位不在⾥⾯定义,可按照规律理解,⼀般询问半导体⼚商)、功耗、测试等。

·连线负载模型(wire load models):电阻、电容、⾯积。

·⼯作环境/条件(Operating conditions):制程(process)(电压和温度的⽐例因数k,表⽰不同的环境之间,各参数缩放的⽐例)·设计规则约束(Design ):最⼤最⼩电容、最⼤最⼩转换时间、最⼤最⼩扇出。

⼯艺库的结构如下所⽰:(2)DC的设计对象在了解了综合库之后,下⾯介绍⼀下DC的设计对象,虽然这个设计对象相对于综合库没有那么重要,但是还是要了解⼀下的。

`第五章综合的约束与优化综合的一个很重要的概念就是:单纯的映射是远远不够的,更重要的是设计的整体优化。

一方面设计工程师为综合规定必要的约束,例如对面积、速度、功耗的要求等,从而使优化有所依据;另一方面选择合适的综合器是优化程度的决定性因素。

同一个设计使用不同的综合器所得到的优化结果可以相差3~5倍。

第一节综合约束5-1-1 概述综合约束是对可测量的电路特性所定义的设计目标,比如面积、速度和电容等。

如果没有这些约束,Design Compiler工具将不能有效地对你的设计进行最优化。

在对设计进行优化时,Design Compiler支持两种类型的约束:●设计规则约束(Design rule constraints)●最优化约束(Optimization constraints)设计规则约束是固有的,在工艺库里定义;这些约束条件是为了保证设计的功能正确性,适用于使用工艺库的每一个设计;可以使这些约束比最优化约束更为严格。

最优化约束是外在的,由设计者自己定义;最优化约束描述设计指标,在整个dc_shell 工作期间应用于当前设计;它们必须接近于现实情况。

D esign Compiler试图同时满足设计规则约束和最优化约束,但设计规则约束必须首先被满足。

设计者可以以命令行形式交互式的指定约束或者在一个约束文件里指令约束。

图5.1显示了主要的设计规则约束和最优化约束,以及如何用dc_shell界面命令来设置这些约束。

图5.1 Major Design Compiler Constraints第二节设置设计规则约束这一节将讨论最常用的设计规则约束:•转换时间(Transition time)•扇出负载(Fanout load)•电容(Capacitance)Design Compiler给设计对象赋予属性来表示这些设计规则约束。

表5.1列出了每一个设计规则约束对应的属性名。

表5.1 设计规则属性Design Rule Constraint Attribute NameTransition time max_transitionFanout load max_fanoutCapacitance max_capacitancemin_capacitanceCell degradation cell_degradationConnection class connection_class 设计规则约束是工艺库里指定属性,你也可以明确地、随意地指定这些约束。

FPGA(Field-Programmable Gate Array)作为一种可编程的逻辑器件,被广泛应用于数字信号处理、通信系统、嵌入式系统等领域。

在设计FPGA电路时,面积和速度是两个核心指标,对于设计人员来说,如何优化FPGA面积和速度是一个非常重要的课题。

本文将从面积优化和速度优化两个方面,探讨FPGA设计中的优化方法。

一、FPGA面积优化方法1. 逻辑优化在FPGA设计中,逻辑优化是一种常见的面积优化方法。

逻辑优化主要包括逻辑综合、布线和布局三个阶段。

在逻辑综合阶段,可以通过逻辑合并、功能分解等技术,减少逻辑门的数量,从而减小FPGA的面积占用。

在布线和布局阶段,可以通过合理的布线规则和布局布线策略,减少开关电路的数量,进而减小FPGA的面积占用。

2. 流水线技术流水线技术是一种常见的面积优化方法,通过将一个大模块分解成多个小模块,并将其连接成流水线,可以减小每个模块的逻辑规模,从而减小FPGA的面积占用。

流水线技术可以有效降低FPGA电路的逻辑深度,提高电路的运行速度。

3. 复用技术在FPGA设计中,复用技术是一种有效的面积优化方法。

通过设计可重用的功能模块,并在不同的部分中多次使用这些功能模块,可以减小FPGA的面积占用。

复用技术可以降低电路的逻辑规模,提高电路的复杂度。

4. 资源共享技术资源共享技术是一种常见的面积优化方法。

通过将同一类型的资源共享给多个功能模块使用,可以减小FPGA的资源占用。

资源共享技术可以降低FPGA的资源消耗,提高电路的资源利用率。

二、FPGA速度优化方法1. 时序优化时序优化是一种常见的速度优化方法。

通过优化时序约束、时钟分配等技术,可以降低电路的时序延迟,提高电路的工作速度。

时序优化可以通过同步技术和异步技术来实现,可以提高电路的工作速度。

2. 缓冲器插入技术缓冲器插入技术是一种有效的速度优化方法。

通过在关键路径上插入缓冲器,可以减小信号传输的延迟,提高电路的工作速度。