第五章:组合逻辑电路(1)

- 格式:ppt

- 大小:6.08 MB

- 文档页数:32

第五章组合逻辑电路设计(Combination Logic CircuitDesign)1.知识要点组合逻辑电路的分析方法;组合逻辑电路的综合过程中真值表的设计构成;冒险(Hazard)产生的原因、检测及消除的方法;译码器(Decoder)、编码器(Encoder)、多路选择器(Multiplexer)、异或门(Exclusive-OR gate)、比较器(Comparator)、全加器(Full Adder)等常用中规模集成电路(MSI)逻辑器件的功能及其工作原理;利用基本的逻辑门和已有的中规模集成电路(MSI)逻辑器件如译码器、编码器、多路选择器、异或门、比较器、全加器、三态器件(Three-State Device)等作为设计的基本元素完成更复杂的组合逻辑电路设计的方法。

等效门符号(摩根定理)(Equivalent Gate Symbols under the Generalized Demorgan’s Theorem);信号名和有效电平(Signal Name and Active Levels);“圈到圈”的逻辑设计(Bubble-to-Bubble Logic Design);电路定时(Circuit Timing);奇偶校验电路(Parity Circuit)的原理、应用;了解:文档标准。

重点:1.组合逻辑电路的分析方法;2.组合逻辑电路的综合过程中真值表的设计构成;3.冒险产生的原因,冒险检测及消除的方法;4.译码器、编码器、多路选择器、异或门、比较器、全加器等常用中规模集成电路(MSI)逻辑器件的功能及其工作原理;熟悉这些器件的使用方法,包括功能扩展等;5.利用译码器、多路选择器等实现组合逻辑函数的方法;6.了解大规模电路的设计特点,利用基本的逻辑门和已有的中规模集成电路(MSI)逻辑器件作为设计的基本元素,完成更复杂的组合逻辑电路设计。

难点:1.由实际问题分析建立真值表;2.冒险的检测与消除方法;3.多输入逻辑的不同设计方法选择;4.基于中小规模集成电路的组合逻辑电路的设计。

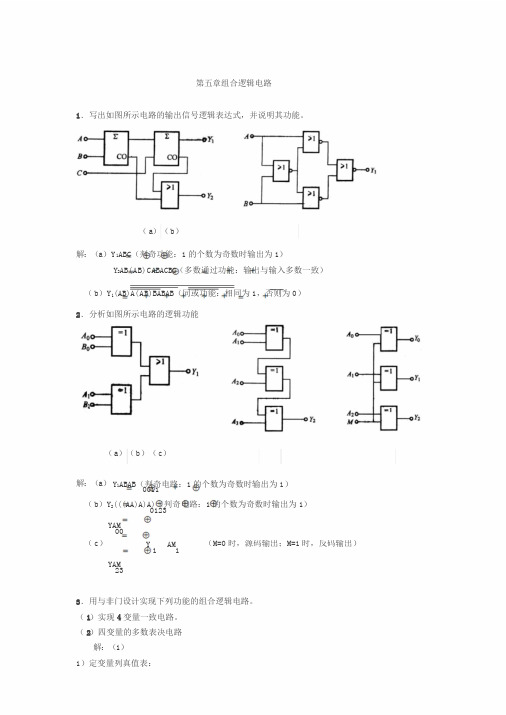

第五章组合逻辑电路1.写出如图所示电路的输出信号逻辑表达式,并说明其功能。

(a)(b)解:(a)Y1ABC(判奇功能:1的个数为奇数时输出为1)Y2AB(AB)CABACBC(多数通过功能:输出与输入多数一致)(b)Y1(AB)A(AB)BABAB(同或功能:相同为1,否则为0)2.分析如图所示电路的逻辑功能(a)(b)(c)解:(a)Y1ABAB(判奇电路:1的个数为奇数时输出为1)0011(b)Y2(((AA)A)A)(判奇电路:1的个数为奇数时输出为1)0123YAM00(c)Y1 A M1(M=0时,源码输出;M=1时,反码输出)YAM233.用与非门设计实现下列功能的组合逻辑电路。

(1)实现4变量一致电路。

(2)四变量的多数表决电路解:(1)1)定变量列真值表:ABCDYABCDY0000110000000101001000100101000011010110010*******010*******011001110001110111112)列函数表达式:YABCDABC D ABCDABCD3)用与非门组电路(2)输入变量A、B、C、D,有3个或3个以上为1时输出为1,输人为其他状态时输出为0。

1)列真值表2)些表达式3)用与非门组电路4.有一水箱由大、小两台水泵ML和Ms供水,如图所示。

水箱中设置了3个水位检测元件A、B、C,如图(a)所示。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C点时水泵停止工作;水位低于C点而高于B点时Ms单独工作;水位低于B点而高于A点时ML单独工作;水位低于A点时ML和Ms同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

解:(1)根据要求列真值表(b)(b)(a)(2)真值表中×对应的输入项为约束项,利用卡诺图化简(c)(d)(c)(d)(e)得:MABCsMBL(ML、M S的1状态表示工作,0状态表示停止)(3)画逻辑图(e)5.某医院有—、二、三、四号病室4间,每室设有呼叫按钮,同时在护士值班室内对应地装有一号、二号、三号、四号4个指示灯。

组合逻辑电路•组合逻辑电路的概述•组合逻辑电路的分析•组合逻辑电路的设计•常用的组合逻辑电路在数字电路中,数字电路可分为组合逻辑电路和时序逻辑电路两大类。

组合逻辑电路:输出仅由输入决定,与电路当前状态无关,电路结构中无反馈环路(无记忆)。

组合逻辑电路的概述1.特点(1)输入、输出之间没有反馈延迟通路;(2)电路中不含记忆元件;(3)电路任何时刻的输出仅取决于该时刻的输入,而与电路原来的状态无关。

2.描述组合电路逻辑功能的方法逻辑表达式、真值表、卡诺图、逻辑图、波形图。

组合逻辑电路的分析[例] 试分析下列组合逻辑电路的功能。

[例] 试分析下列组合逻辑电路的功能。

解:(1)根据给定的逻辑电路,写出所有输出逻辑函数表达式并对其进行变换:(2)根据化简后的逻辑函数表达式列出真值表,如表。

(3)逻辑功能评述该电路是一位二进制数比较器:当A>B时,L1=1;当A<B时,L3=1。

注意在确定该电路的逻辑功能时,输出函数L1、L2、L3不能分开考虑。

组合逻辑电路的设计1.组合逻辑电路设计的目的设计组合电路的目的是根据功能要求设计最佳电路。

即根据给出的实际问题,求出能够实现这一逻辑要求的最简的逻辑电路,这就是组合电路的设计,它是分析的逆过程。

2.设计组合电路的步骤:(1)分析设计要求;(2)根据功能要求列出真值表;(3)根据真值表利用卡诺图进行化简,得到最简逻辑表达式;(4)根据最简表达式画逻辑图。

[例]用与非门设计一个三变量“多数表决电路”。

解:(1)进行逻辑抽象,建立真值表:用A、B、C表示参加表决的输入变量,“1”代表赞成,“0”代表反对,用F表示表决结果,“1”代表多数赞成,“0”代表多数反对。

根据题意,列真值表如表。

(2)根据真值表写出逻辑函数的“最小项之和”表达式:(3)将上述表达式化简,并转换成与非形式:(4)根据逻辑函数表达式画出逻辑电路图,如图。

上述逻辑电路可以用74LS00芯片实现,74LS00为4个2输入与非门芯片,74LS00的逻辑符号和引脚图如图所示。

第五章 组合逻辑电路典型例题分析第一部分:例题剖析例1.求以下电路的输出表达式:解:例2.由3线-8线译码器T4138构成的电路如图所示,请写出输出函数式.解:Y = AC BC ABC= AC +BC + ABC = C(AB) +CAB = C (AB) T4138的功能表&&Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7“1”T4138A B CA 2A 1A 0YaYbS 1 S 2 S 30 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1S 1S 2S 31 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0A 2A 1A 0Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 70 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 0例3.分析如图电路,写出输出函数Z的表达式。

CC4512为八选一数据选择器。

解:例4.某组合逻辑电路的真值表如下,试用最少数目的反相器和与非门实现电路。

(表中未出现的输入变量状态组合可作为约束项)CC4512的功能表A ⨯DIS INH 2A 1A 0Y1 ⨯0 10 00 00 00 00 00 00 00 0⨯⨯⨯⨯⨯0 0 00 0 10 1 00 1 11 0 0 1 0 11 1 01 1 1高阻态 0D 0D 1D 2D 3D 4D 5D 6D 7ZCC4512A 0A 1A 2D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7DIS INHD1DA B C D Y 0 0 0 0 10 0 0 1 00 0 1 0 10 0 1 1 00 1 0 0 0CD AB 00 01 11 1000 1 0 0 101 0 1 0 1 11 ××××10 0 1 ××AB第一步画卡诺图第三步画逻辑电路图例5.写出下面组合电路的输出表达式,分析逻辑功能。

数字电子技术教案设计范例一、教学内容本节课选自《数字电子技术基础》第五章“组合逻辑电路”,具体内容包括5.1节“组合逻辑电路概述”,5.2节“逻辑门电路”,5.3节“逻辑函数及其化简”,以及5.4节“组合逻辑电路的设计与应用”。

二、教学目标1. 理解组合逻辑电路的概念,掌握组合逻辑电路的特点;2. 学会使用逻辑门电路进行逻辑函数的表示与计算;3. 能够运用逻辑函数化简方法,简化给定的逻辑函数。

三、教学难点与重点重点:组合逻辑电路的概念、逻辑门电路的运用、逻辑函数化简方法。

难点:组合逻辑电路的设计与应用、逻辑函数的化简过程。

四、教具与学具准备1. 教具:多媒体教学设备、PPT课件、逻辑门电路实物模型;2. 学具:笔记本电脑、逻辑门电路实验箱、逻辑函数计算器。

五、教学过程1. 实践情景引入(5分钟)通过展示一个简单的组合逻辑电路实物模型,引导学生思考:什么是组合逻辑电路?它有什么作用?2. 知识讲解(15分钟)(1)讲解组合逻辑电路的概念、特点;(2)介绍逻辑门电路的种类及功能;(3)阐述逻辑函数及其化简方法。

3. 例题讲解(15分钟)选取一道具有代表性的例题,讲解如何运用逻辑门电路表示逻辑函数,以及如何化简逻辑函数。

4. 随堂练习(10分钟)布置一道与例题相似的练习题,让学生当堂完成,巩固所学知识。

5. 课堂讨论与解答(15分钟)对学生的练习进行点评,解答学生在练习过程中遇到的问题。

六、板书设计1. 组合逻辑电路2. 内容:(1)组合逻辑电路概念、特点;(2)逻辑门电路种类、功能;(3)逻辑函数化简方法;(4)例题及解答过程。

七、作业设计1. 作业题目:2. 答案:(1)用与门、或门表示;(2)化简结果:F(A,B,C)=A'B+C。

八、课后反思及拓展延伸1. 反思:本节课学生对组合逻辑电路的理解程度,以及对逻辑函数化简方法的掌握情况;2. 拓展延伸:引导学生了解数字电路在实际应用中的重要性,激发学生学习数字电子技术的兴趣。

第五章组合逻辑电路的VerilogHDL实现第5章组合逻辑电路的Verilog HDL实现5.10.1 逻辑电路的Verilog HDL描述方式Verilog HDL描述逻辑电路时常用3种描述方式,分别为:行为型描述、数据流型描述和结构型描述。

行为型描述只描述行为特征,不涉及逻辑电路的实现,是一种高级语言描述方式,使用例如always语句或initial 语句块中的过程赋值语句;数据流型描述指通过assign连续赋值实现组合逻辑功能的描述方式;结构型描述指描述实体连接的结构方式,所谓实体一般指Verilog 语言已定义的基元,包括门原语、用户自定义原语(UDP)和其他模块(module)。

行为型描述语句更简练,不能被综合;结构型描述语句通常容易被综合,但语句显得复杂。

在实际开发中往往多种描述方法混合使用。

5.10.2 2选1数据选择器的Verilog HDL实现2选1数据选择器可以有多种描述方式,通过4个实例和3种描述方式对例子中出现的语法现象进行解释。

5.10.12选1数据选择器的数据流型描述方式;5.10.22选1数据选择器的数据流型描述方式;5.10.32选1数据选择器的行为型描述方式;5.10.42选1数据选择器的结构型描述方式;5.10.2.1 2选1数据选择器实例1//例5.10.1module Mux21(a,b,s,y);//----------------1input a,b;input s;output y;assign y=(s==0)?a:b;//----------------2endmodule//----------------310.2.1 2选1数据选择器实例11. Verilog语言描述//例5.10.1module Mux21(a,b,s,y);//----------------1input a,b;input s;output y;assign y=(s==0)?a:b;//----------------2endmodule//----------------32. 程序说明(1)注释行(2)模块定义语句module和endmodule所有的程序都置于模块(module)框架结构内。