MCS-51单片机的指令时序

- 格式:doc

- 大小:43.50 KB

- 文档页数:4

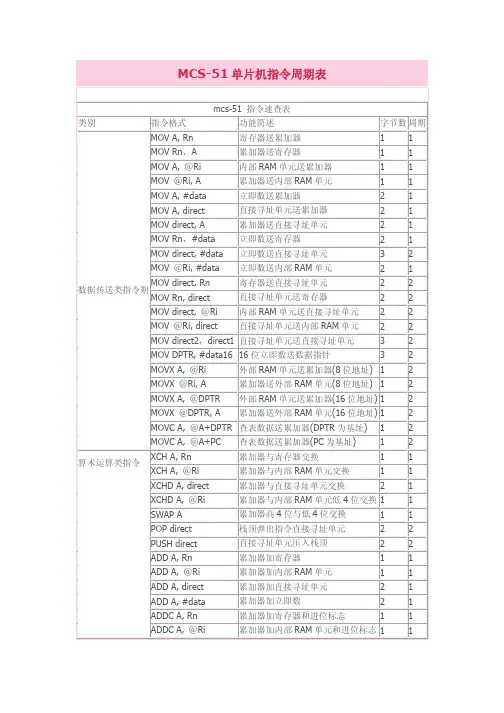

MCS-51单片机指令周期表mcs-51指令速查表类别指令格式功能简述字节数周期MOV A,Rn寄存器送累加器11MOV Rn,A累加器送寄存器11MOV A,@Ri内部RAM单元送累加器11MOV@Ri,A累加器送内部RAM单元11MOV A,#data立即数送累加器21MOV A,direct直接寻址单元送累加器21MOV direct,A累加器送直接寻址单元21MOV Rn,#data立即数送寄存器21MOV direct,#data立即数送直接寻址单元32MOV@Ri,#data立即数送内部RAM单元21MOV direct,Rn寄存器送直接寻址单元22数据传送类指令期MOV Rn,direct直接寻址单元送寄存器22MOV direct,@Ri内部RAM单元送直接寻址单元22MOV@Ri,direct直接寻址单元送内部RAM单元22MOV direct2,direct1直接寻址单元送直接寻址单元32MOV DPTR,#data1616位立即数送数据指针32MOVX A,@Ri外部RAM单元送累加器(8位地址)12MOVX@Ri,A累加器送外部RAM单元(8位地址)12MOVX A,@DPTR外部RAM单元送累加器(16位地址)12MOVX@DPTR,A累加器送外部RAM单元(16位地址)12MOVC A,@A+DPTR查表数据送累加器(DPTR为基址)12MOVC A,@A+PC查表数据送累加器(PC为基址)12XCH A,Rn累加器与寄存器交换11算术运算类指令XCH A,@Ri累加器与内部RAM单元交换11XCHD A,direct累加器与直接寻址单元交换21XCHD A,@Ri累加器与内部RAM单元低4位交换11SWAP A累加器高4位与低4位交换11POP direct栈顶弹出指令直接寻址单元22PUSH direct直接寻址单元压入栈顶22ADD A,Rn累加器加寄存器11ADD A,@Ri累加器加内部RAM单元11ADD A,direct累加器加直接寻址单元21ADD A,#data累加器加立即数21ADDC A,Rn累加器加寄存器和进位标志11ADDC A,@Ri累加器加内部RAM单元和进位标志11ADDC A,#data累加器加立即数和进位标志21ADDC A,direct累加器加直接寻址单元和进位标志21INC A累加器加111INC Rn寄存器加111INC direct直接寻址单元加121INC@Ri内部RAM单元加111INC DPTR数据指针加112DA A十进制调整11SUBB A,Rn累加器减寄存器和进位标志11SUBB A,@Ri累加器减内部RAM单元和进位标志11SUBB A,#data累加器减立即数和进位标志21SUBB A,direct累加器减直接寻址单元和进位标志21DEC A累加器减111DEC Rn寄存器减111DEC@Ri内部RAM单元减111DEC direct直接寻址单元减121MUL AB累加器乘寄存器B14DIV AB累加器除以寄存器B14ANL A,Rn累加器与寄存器11逻辑运算类指令ANL A,@Ri累加器与内部RAM单元11ANL A,#data累加器与立即数21ANL A,direct累加器与直接寻址单元21ANL direct,A直接寻址单元与累加器21ANL direct,#data直接寻址单元与立即数31ORL A,Rn累加器或寄存器11ORL A,@Ri累加器或内部RAM单元11ORL A,#data累加器或立即数21ORL A,direct累加器或直接寻址单元21ORL direct,A直接寻址单元或累加器21ORL direct,#data直接寻址单元或立即数31XRL A,Rn累加器异或寄存器11XRL A,@Ri累加器异或内部RAM单元11XRL A,#data累加器异或立即数21XRL A,direct累加器异或直接寻址单元21XRL direct,A直接寻址单元异或累加器21XRL direct,#data直接寻址单元异或立即数32RL A累加器左循环移位11RLC A累加器连进位标志左循环移位11RR A累加器右循环移位11RRC A累加器连进位标志右循环移位11CPL A累加器取反11CLR A累加器清零11ACCALL addr112KB范围内绝对调用22AJMP addr112KB范围内绝对转移22LCALL addr162KB范围内长调用32LJMP addr162KB范围内长转移32SJMP rel相对短转移22JMP@A+DPTR相对长转移12RET子程序返回12RET1中断返回12控制转移类指令JZ rel累加器为零转移22JNZ rel累加器非零转移22CJNE A,#data,rel累加器与立即数不等转移32CJNE A,direct,rel累加器与直接寻址单元不等转移32CJNE Rn,#data,rel寄存器与立即数不等转移32CJNE@Ri,#data,rel RAM单元与立即数不等转移32DJNZ Rn,rel寄存器减1不为零转移22DJNZ direct,rel直接寻址单元减1不为零转移32NOP空操作11MOV C,bit直接寻址位送C21MOV bit,C C送直接寻址位21CLR C C清零11CLR bit直接寻址位清零21CPL C C取反11CPL bit直接寻址位取反21SETB C C置位11SETB bit直接寻址位置位21布尔操作类指令ANL C,bit C逻辑与直接寻址位22ANL C,/bit C逻辑与直接寻址位的反22ORL C,bit C逻辑或直接寻址位22ORL C,/bit C逻辑或直接寻址位的反22JC rel C为1转移22JNC rel C为零转移22JB bit,rel直接寻址位为1转移32JNB bit,rel直接寻址为0转移32JBC bit,rel直接寻址位为1转移并清该位32。

计算机工作时,是在统一的时钟脉冲控制下一拍一拍地进行的。

这个脉冲是由单片机控制器中的时序电路发出的。

单片机的时序就是CPU在执行指令时所需控制信号的时间顺序,为了保证各部件间的同步工作,单片机内部电路应在唯一的时钟信号下严格地控时序进行工作,在学习51单片机的时序之前,我们先来了解下时序相关的一些概念。

既然计算机是在统一的时钟脉冲控制下工作的,那么,它的时钟脉冲是怎么来的呢?要给我们的计算机CPU提供时序,就需要相关的硬件电路,即振荡器和时钟电路。

我们学习的8051单片机内部有一个高增益反相放大器,这个反相放大器的作用就是用于构成振荡器用的,但要形成时钟,外部还需要加一些附加电路。

8051单片机的时钟产生有以下两种方法:1. 内部时钟方式:利用单片机内部的振荡器,然后在引脚XTAL1(18脚)和XTAL2(19脚)两端接晶振,就构成了稳定的自激振荡器,其发出的脉冲直接送入内部时钟电路,外接晶振时,晶振两端的电容一般选择为30PF左右;这两个电容对频率有微调的作用,晶振的频率范围可在1.2MHz-12MHz之间选择。

为了减少寄生电容,更好地保证振荡器稳定、可靠地工作,振荡器和电容应尽可能安装得与单片机芯片靠近。

2. 外部时钟方式:此方式是利用外部振荡脉冲接入XTAL1或XTAL2。

HMOS和CHMOS单片机外时钟信号接入方式不同,HMOS型单片机(例如8051)外时钟信号由XTAL2端脚注入后直接送至内部时钟电路,输入端XTAL1应接地。

由于XTAL2端的逻辑电平不是TTL的,故建议外接一个上接电阻。

对于CHMOS型的单片机(例如80C51),因内部时钟发生器的信号取自反相器的输入端,故采用外部时钟源时,接线方式为外时钟信号接到XTAL1而XTAL2悬空。

如下图外接时钟信号通过一个二分频的触发器而成为内部时钟信号,要求高、低电平的持续时间都大于20ns,一般为频率低于12MHz的方波。

片内时钟发生器就是上述的二分频触发器,它向芯片提供了一个2节拍的时钟信号。

MCS-51单片机的指令时序时序是用定时单位来描述的,MCS-51的时序单位有四个,它们分别是节拍、状态、机器周期和指令周期,接下来我们分别加以说明。

·节拍与状态:我们把振荡脉冲的周期定义为节拍(为方便描述,用P表示),振荡脉冲经过二分频后即得到整个单片机工作系统的时钟信号,把时钟信号的周期定义为状态(用S表示),这样一个状态就有两个节拍,前半周期相应的节拍我们定义为1(P1),后半周期对应的节拍定义为2(P2)。

·机器周期:MCS-51有固定的机器周期,规定一个机器周期有6个状态,分别表示为S1-S6,而一个状态包含两个节拍,那么一个机器周期就有12个节拍,我们可以记着S1P1、S1P2……S6P1、S6P2,一个机器周期共包含12个振荡脉冲,即机器周期就是振荡脉冲的12分频,显然,如果使用6MHz的时钟频率,一个机器周期就是2us,而如使用12MHz的时钟频率,一个机器周期就是1us。

·指令周期:执行一条指令所需要的时间称为指令周期,MCS-51的指令有单字节、双字节和三字节的,所以它们的指令周期不尽相同,也就是说它们所需的机器周期不相同,可能包括一到四个不等的机器周期(这些内容,我们将在下面的章节中加以说明)。

·MCS-51的指令时序:MCS-51指令系统中,按它们的长度可分为单字节指令、双字节指令和三字节指令。

执行这些指令需要的时间是不同的,也就是它们所需的机器周期是不同的,有下面几种形式:·单字节指令单机器周期·单字节指令双机器周期·双字节指令单机器周期·双字节指令双机器周期·三字节指令双机器周期·单字节指令四机器周期(如单字节的乘除法指令)下图是MCS-51系列单片机的指令时序图:上图是单周期和双周期取指及执行时序,图中的ALE脉冲是为了锁存地址的选通信号,显然,每出现一次该信号单片机即进行一次读指令操作。

MCS-51单片机指令周期表mcs-51指令速查表类别指令格式功能简述字节数周期MOV A,Rn寄存器送累加器11MOV Rn,A累加器送寄存器11MOV A,@Ri内部RAM单元送累加器11MOV@Ri,A累加器送内部RAM单元11MOV A,#data立即数送累加器21MOV A,direct直接寻址单元送累加器21MOV direct,A累加器送直接寻址单元21MOV Rn,#data立即数送寄存器21MOV direct,#data立即数送直接寻址单元32MOV@Ri,#data立即数送内部RAM单元21MOV direct,Rn寄存器送直接寻址单元22数据传送类指令期MOV Rn,direct直接寻址单元送寄存器22MOV direct,@Ri内部RAM单元送直接寻址单元22MOV@Ri,direct直接寻址单元送内部RAM单元22MOV direct2,direct1直接寻址单元送直接寻址单元32MOV DPTR,#data1616位立即数送数据指针32MOVX A,@Ri外部RAM单元送累加器(8位地址)12MOVX@Ri,A累加器送外部RAM单元(8位地址)12MOVX A,@DPTR外部RAM单元送累加器(16位地址)12MOVX@DPTR,A累加器送外部RAM单元(16位地址)12MOVC A,@A+DPTR查表数据送累加器(DPTR为基址)12MOVC A,@A+PC查表数据送累加器(PC为基址)12XCH A,Rn累加器与寄存器交换11算术运算类指令XCH A,@Ri累加器与内部RAM单元交换11XCHD A,direct累加器与直接寻址单元交换21XCHD A,@Ri累加器与内部RAM单元低4位交换11SWAP A累加器高4位与低4位交换11POP direct栈顶弹出指令直接寻址单元22PUSH direct直接寻址单元压入栈顶22ADD A,Rn累加器加寄存器11ADD A,@Ri累加器加内部RAM单元11ADD A,direct累加器加直接寻址单元21ADD A,#data累加器加立即数21ADDC A,Rn累加器加寄存器和进位标志11ADDC A,@Ri累加器加内部RAM单元和进位标志11ADDC A,#data累加器加立即数和进位标志21ADDC A,direct累加器加直接寻址单元和进位标志21INC A累加器加111INC Rn寄存器加111INC direct直接寻址单元加121INC@Ri内部RAM单元加111INC DPTR数据指针加112DA A十进制调整11SUBB A,Rn累加器减寄存器和进位标志11SUBB A,@Ri累加器减内部RAM单元和进位标志11SUBB A,#data累加器减立即数和进位标志21SUBB A,direct累加器减直接寻址单元和进位标志21DEC A累加器减111DEC Rn寄存器减111DEC@Ri内部RAM单元减111DEC direct直接寻址单元减121MUL AB累加器乘寄存器B14DIV AB累加器除以寄存器B14ANL A,Rn累加器与寄存器11逻辑运算类指令ANL A,@Ri累加器与内部RAM单元11ANL A,#data累加器与立即数21ANL A,direct累加器与直接寻址单元21ANL direct,A直接寻址单元与累加器21ANL direct,#data直接寻址单元与立即数31ORL A,Rn累加器或寄存器11ORL A,@Ri累加器或内部RAM单元11ORL A,#data累加器或立即数21ORL A,direct累加器或直接寻址单元21ORL direct,A直接寻址单元或累加器21ORL direct,#data直接寻址单元或立即数31XRL A,Rn累加器异或寄存器11XRL A,@Ri累加器异或内部RAM单元11XRL A,#data累加器异或立即数21XRL A,direct累加器异或直接寻址单元21XRL direct,A直接寻址单元异或累加器21XRL direct,#data直接寻址单元异或立即数32RL A累加器左循环移位11RLC A累加器连进位标志左循环移位11RR A累加器右循环移位11RRC A累加器连进位标志右循环移位11CPL A累加器取反11CLR A累加器清零11ACCALL addr112KB范围内绝对调用22AJMP addr112KB范围内绝对转移22LCALL addr162KB范围内长调用32LJMP addr162KB范围内长转移32SJMP rel相对短转移22JMP@A+DPTR相对长转移12RET子程序返回12RET1中断返回12控制转移类指令JZ rel累加器为零转移22JNZ rel累加器非零转移22CJNE A,#data,rel累加器与立即数不等转移32CJNE A,direct,rel累加器与直接寻址单元不等转移32CJNE Rn,#data,rel寄存器与立即数不等转移32CJNE@Ri,#data,rel RAM单元与立即数不等转移32DJNZ Rn,rel寄存器减1不为零转移22DJNZ direct,rel直接寻址单元减1不为零转移32NOP空操作11MOV C,bit直接寻址位送C21MOV bit,C C送直接寻址位21CLR C C清零11CLR bit直接寻址位清零21CPL C C取反11CPL bit直接寻址位取反21SETB C C置位11SETB bit直接寻址位置位21布尔操作类指令ANL C,bit C逻辑与直接寻址位22ANL C,/bit C逻辑与直接寻址位的反22ORL C,bit C逻辑或直接寻址位22ORL C,/bit C逻辑或直接寻址位的反22JC rel C为1转移22JNC rel C为零转移22JB bit,rel直接寻址位为1转移32JNB bit,rel直接寻址为0转移32JBC bit,rel直接寻址位为1转移并清该位32。

单片机时序图MCS51单片机的指令时序接下来我们分别对几个典型的指令时序加以说明。

·单字节单周期指令:单字节单周期指令只进行一次读指令操作,当第二个ALE信号有效时,PC并不加1,那么读出的还是原指令,属于一次无效的读操作。

·双字节单周期指令:这类指令两次的ALE信号都是有效的,只是第一个ALE信号有效时读的是操作码,第二个ALE信号有效时读的是操作数。

·单字节双周期指令:两个机器周期需进行四读指令操作,但只有一次读操作是有效的,后三次的读操作均为无效操作。

单字节双周期指令有一种特殊的情况,象MOVX这类指令,执行这类指令时,先在ROM 中读取指令,然后对外部数据存储器进行读或写操作,头一个机器周期的第一次读指令的操作码为有效,而第二次读指令操作则为无效的。

在第二个指令周期时,则访问外部数据存储器,这时,ALE信号对其操作无影响,即不会再有读指令操作动作。

上页的时序图中,我们只描述了指令的读取状态,而没有画出指令执行时序,因为每条指令都包含了具体的操作数,而操作数类型种类繁多,这里不便列出,有兴趣的读者可参阅有关书籍时序是用定时单位来描述的,MCS-51的时序单位有四个,它们分别是节拍、状态、机器周期和指令周期,接下来我们分别加以说明。

·节拍与状态:我们把振荡脉冲的周期定义为节拍(为方便描述,用P表示),振荡脉冲经过二分频后即得到整个单片机工作系统的时钟信号,把时钟信号的周期定义为状态(用S表示),这样一个状态就有两个节拍,前半周期相应的节拍我们定义为1(P1),后半周期对应的节拍定义为2(P2)。

·机器周期:MCS-51有固定的机器周期,规定一个机器周期有6个状态,分别表示为S1-S6,而一个状态包含两个节拍,那么一个机器周期就有12个节拍,我们可以记着S1P1、S1P2……S6P1、S6P2,一个机器周期共包含12个振荡脉冲,即机器周期就是振荡脉冲的12分频,显然,如果使用6MHz的时钟频率,一个机器周期就是2us,而如使用12MHz的时钟频率,一个机器周期就是1us。

MCS-51单片机的指令时序

时序是用定时单位来描述的,MCS-51 的时序单位有四个,它们分别是节拍、状态、机器周期和指令周期,接下来我们分别加以说明。

节拍与状态:我们把振荡脉冲的周期定义为节拍(为方便描述,用P 表示),振荡脉冲经过二分频后即得到整个单片机工作系统的时钟信号,把时钟信号

的周期定义为状态(用S 表示),这样一个状态就有两个节拍,前半周期相应

的节拍我们定义为1(P1),后半周期对应的节拍定义为2(P2)。

机器周期:MCS-51 有固定的机器周期,规定一个机器周期有6 个状态,分别表示为S1-

S6,而一个状态包含两个节拍,那么一个机器周期就有12 个节拍,我们可以

记着S1P1、S1P2……S6P1、S6P2,一个机器周期共包含12 个振荡脉冲,即机器周期就是振荡脉冲的12 分频,显然,如果使用6MHz 的时钟频率,一个机

器周期就是2us,而如使用12MHz 的时钟频率,一个机器周期就是1us。

指令周期:执行一条指令所需要的时间称为指令周期,MCS-51 的指令有单字节、双字节和三字节的,所以它们的指令周期不尽相同,也就是说它们所需的机器

周期不相同,可能包括一到四个不等的机器周期(这些内容,我们将在下面的

章节中加以说明)。

MCS-51 的指令时序:MCS-51 指令系统中,按它们的长度可分为单字节指令、双字节指令和三字节指令。

执行这些指令需要的时间是

不同的,也就是它们所需的机器周期是不同的,有下面几种形式:单字节指令单机器周期单字节指令双机器周期双字节指令单机器周期

双字节指令双机器周期三字节指令双机器周期单字节指令四机器周期(如单

字节的乘除法指令) 下图是MCS-51 系列单片机的指令时序图:。

MCS-51单片机的指令时序

时序是用定时单位来描述的,MCS-51的时序单位有四个,它们分别是节拍、状态、机器周期和指令周期,接下来我们分别加以说明。

·节拍与状态:

我们把振荡脉冲的周期定义为节拍(为方便描述,用P表示),振荡脉冲经过二分频后即得到整个单片机工作系统的时钟信号,把时钟信号的周期定义为状态(用S表示),这样一个状态就有两个节拍,前半周期相应的节拍我们定义为1(P1),后半周期对应的节拍定义为2(P2)。

·机器周期:

MCS-51有固定的机器周期,规定一个机器周期有6个状态,分别表示为S1-S6,而一个状态包含两个节拍,那么一个机器周期就有12个节拍,我们可以记着S1P1、S1P2……S6P1、S6P2,一个机器周期共包含12个振荡脉冲,即机器周期就是振荡脉冲的12分频,显然,如果使用6MHz的时钟频率,一个机器周期就是2us,而如使用12MHz的时钟频率,一个机器周期就是1us。

·指令周期:

执行一条指令所需要的时间称为指令周期,MCS-51的指令有单字节、双字节和三字节的,所以它们的指令周期不尽相同,也就是说它们所需的机器周期不相同,可能包括一到四个不等的机器周期(这些内容,我们将在下面的章节中加以说明)。

·MCS-51的指令时序:

MCS-51指令系统中,按它们的长度可分为单字节指令、双字节指令和三字节指令。

执行这些指令需要的时间是不同的,也就是它们所需的机器周期是不同的,有下面几种形式:

·单字节指令单机器周期

·单字节指令双机器周期

·双字节指令单机器周期

·三字节指令双机器周期

·单字节指令四机器周期(如单字节的乘除法指令)

下图是MCS-51系列单片机的指令时序图:

上图是单周期和双周期取指及执行时序,图中的ALE脉冲是为了锁存地址的选通信号,显然,

每出现一次该信号单片机即进行一次读指令操作。

从时序图中可看出,该信号是时钟频率6分

频后得到,在一个机器周期中,ALE信号两次有效,第一次在S1P2和S2P1期间,第二次在

S4P2和S5P1期间。

接下来我们分别对几个典型的指令时序加以说明。

·单字节单周期指令:

单字节单周期指令只进行一次读指令操作,当第二个ALE信号有效时,PC并不加1,那么读出的还是原指令,属于一次无效的读操作。

·双字节单周期指令:

这类指令两次的ALE信号都是有效的,只是第一个ALE信号有效时读的是操作码,第二个ALE信号有效时读的是操作数。

两个机器周期需进行四读指令操作,但只有一次读操作是有效的,后三次的读操作均为无效操作。

单字节双周期指令有一种特殊的情况,象MOVX这类指令,执行这类指令时,先在ROM中读取指令,然后对外部数据存储器进行读或写操作,头一个机器周期的第一次读指令的操作码为有效,而第二次读指令操作则为无效的。

在第二个指令周期时,则访问外部数据存储器,这时,ALE信号对其操作无影响,即不会再有读指令操作动作。

上页的时序图中,我们只描述了指令的读取状态,而没有画出指令执行时序,因为每条指令都包含了具体的操作数,而操作数类型种类繁多,这里不便列出,有兴趣的读者可参阅有关书籍。

·外部程序存储器(ROM)读时序

右图8051外部程序存储器读时序图,从

图中可看出,P0口提供低8位地址,P2口

提供高8位地址,S2结束前,P0口上的低

8位地址是有效的,之后出现在P0口上的就

不再是低8位的地址信号,而是指令数据信

号,当然地址信号与指令数据信号之间有一

段缓冲的过度时间,这就要求,在S2其间必

须把低8位的地址信号锁存起来,这时是用

ALE选通脉冲去控制锁存器把低8位地址予

以锁存,而P2口只输出地址信号,而没有指

令数据信号,整个机器周期地址信号都是有

效的,因而无需锁存这一地址信号。

从外部程序存储器读取指令,必须有两个信号进行控制,除了上述的ALE信号,还有一个PSEN(外部ROM读选通脉冲),上图显然可看出,PSEN从S3P1开始有效,直到将地址信

号送出和外部程序存储器的数据读入CPU后方才失效。

而又从S4P2开始执行第二个读指令操

作。

·外部数据存储器(RAM)读时序

右图8051外部数据存储器读写

时序图,从ROM中读取的需执行的

指令,而CPU对外部数据存储的访

问是对RAM进行数据的读或写操

作,属于指令的执行周期,值得一

提的是,读或写是两个不同的机器

周期,但他们的时序却是相似的,

我们只对RAM的读时序进行分析。

上一个机器周期是取指阶段,是

从ROM中读取指令数据,接着的下

个周期才开始读取外部数据存储器

RAM中的内容。

在S4结束后,先把需读取RAM中的地址放到总线上,包括P0口上的低8位地址A0-A7和P2口上的高8位地址A8-A15。

当RD选通脉冲有效时,将RAM的数据通过P0数据总线读进CPU。

第二个机器周期的ALE信号仍然出现,进行一次外部ROM的读操作,但是这一次的读操作属于无效操作。

对外部RAM进行写操作时,CPU输出的则是WR(写选通信号),将数据通过P0数据总线写入外部存储中。