cadence原理图转换成protel

- 格式:doc

- 大小:1.05 MB

- 文档页数:7

ORCAD PCB转换为Protel 99se/ Protel DXP

一:转换到Protel 99se

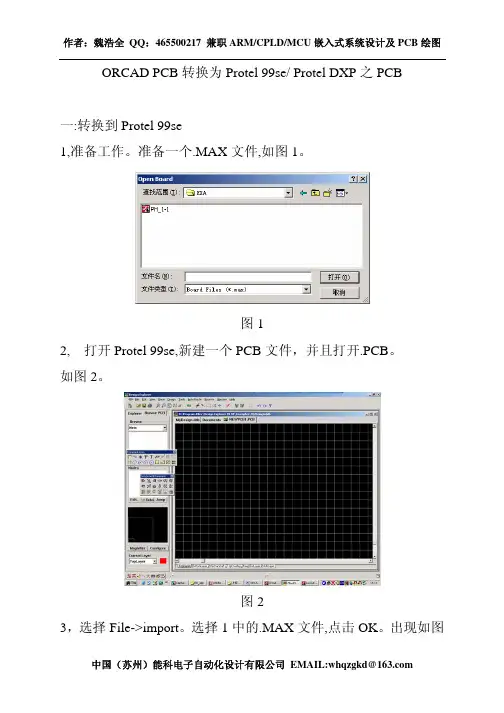

1,准备工作。

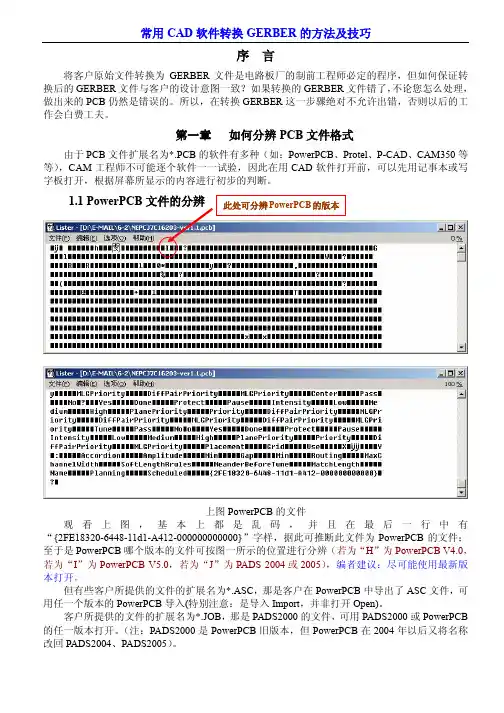

准备一个.MAX文件,如图1。

图1

2, 打开Protel 99se,新建一个PCB文件,并且打开.PCB。

如图2。

图2

3,选择File->import。

选择1中的.MAX文件,点击OK。

出现如图3,弹出对话框。

图3

在出现的对话框Option中选择FABDWG和NOTES为任意一层。

点击OK按键,即可生成PCB文件。

如图4。

图4

注意:

1,在第3步中可以选择ORCAD的层颜色(USE orCAD Color Setting)或选择Protel 99se默认的层颜色。

2,如果不选择FABDWG和NOTES为任意一层,则不能生成PCB文件,同时也会提示出错.

4,转换成功!!!!!!可以在PROTEL 99SE 里修改电路图。

二:转换到Protel DXP/2004

1 准备工作.准备一个.MAX文件,如上步骤1

2 打开Protel DXP或Protel 2004,选择打开,选择1中的.MAX文件,并打开。

3 同上第三步,第四步。

4 保存格式为.PCB格式。

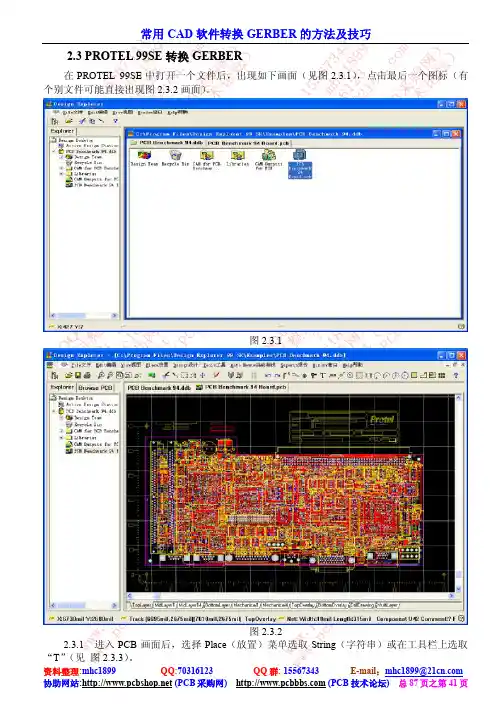

Orcad原理图转为protel DXP原理图方法及步骤

O RCAD原理图转为PROTEL原理图,其主要方法及步骤如下:

1、如果ORCAD的软件版本为16.3,需要将其另存为16.2版本,通过Save as命令即可实现;

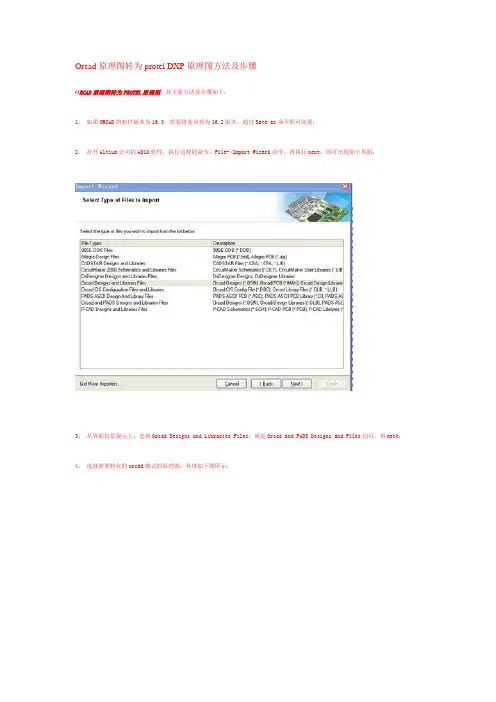

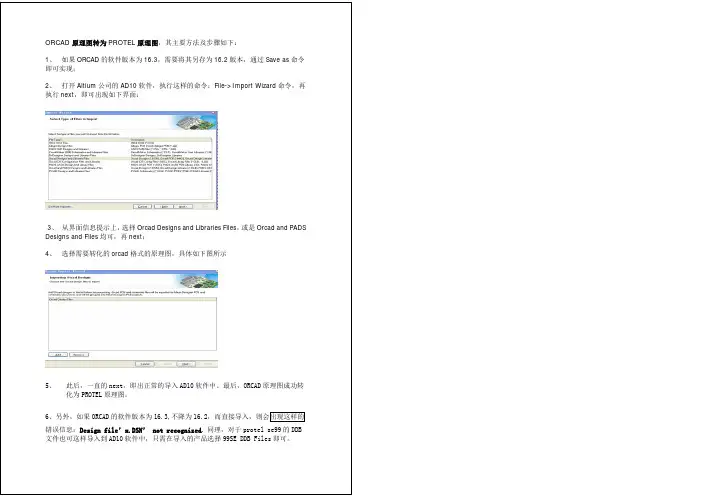

2、打开Altium公司的AD10软件,执行这样的命令:File->Import Wizard命令,再执行next,即可出现如下界面:

3、从界面信息提示上,选择Orcad Designs and Libraries Files,或是Orcad and PADS Designs and Files均可,再next;

4、选择需要转化的orcad格式的原理图,具体如下图所示:

5、此后,一直的next,即出正常的导入AD10软件中。

最后,ORCAD原理图成功转化为PROTEL原理图。

另外,如果ORCAD的软件版本为16.3,不降为16.2,而直接导入,则会出现这样的错误信息:Design file’x.DSN’ not recognized. 同理,对于protel se99的DDB文件也可这样导入到AD10软件中,只需在导入的产品选择99SE DDB Files即可。

如何将a l t i u m d e s i g n e r的原理图和P C B转入c e n c e里This model paper was revised by the Standardization Office on December 10, 2020说明:1)本教程适用于将altiumdesigner的原理图和PCB转入cadence(分别对应captureCIS和allegro)里。

对于protel99se,可以将其先导入较新版本的AD 里,再转入cadence中。

2)整个过程中使用的软件包括altiumdesignerSummer08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。

其中,后面两个软件较小,便于下载。

3)原理图的转化路线是,从altiumdesigner导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。

因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。

如果你不是这些版本的软件,也可以参考本人的方法进行尝试。

4)pcb转化的顺序是,altiumdesigner导出的文件,导入PADS9.3打开,然后导出.asc文件。

随后利用allegro对pads的接口,将pads文件导入。

1.原理图的导入1.1选中原理图的项目文件,即.PRJPCB文件,右键-》saveprojecas,选择.dsn文件,输入要保存的文件名,保存。

注意输入新的文件名的时候要把文件名的后缀手动改掉。

1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。

具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。

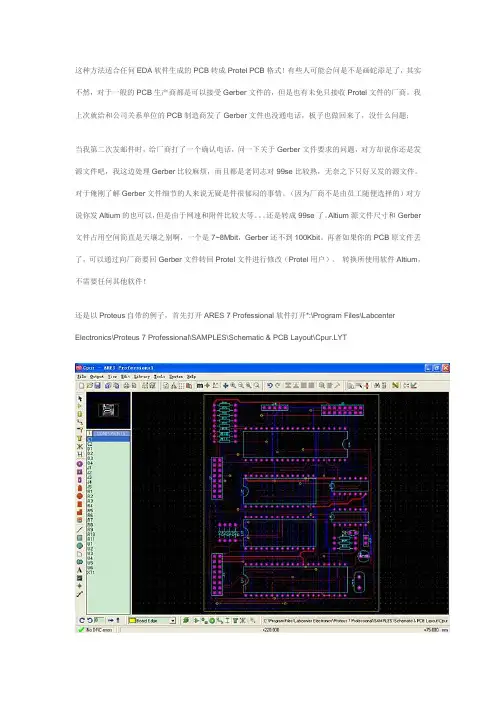

这种方法适合任何EDA软件生成的PCB转成Protel PCB格式!有些人可能会问是不是画蛇添足了,其实不然,对于一般的PCB生产商都是可以接受Gerber文件的,但是也有未免只接收Protel文件的厂商。

我上次就给和公司关系单位的PCB制造商发了Gerber文件也没通电话,板子也做回来了,没什么问题;当我第二次发邮件时,给厂商打了一个确认电话,问一下关于Gerber文件要求的问题,对方却说你还是发源文件吧,我这边处理Gerber比较麻烦,而且都是老同志对99se比较熟,无奈之下只好又发的源文件。

对于俺刚了解Gerber文件细节的人来说无疑是件很郁闷的事情。

(因为厂商不是由员工随便选择的)对方说你发Altium的也可以,但是由于网速和附件比较大等。

还是转成99se了。

Altium源文件尺寸和Gerber 文件占用空间简直是天壤之别啊,一个是7~8Mbit,Gerber还不到100Kbit。

再者如果你的PCB原文件丢了,可以通过向厂商要回Gerber文件转回Protel文件进行修改(Protel用户)。

转换所使用软件Altium,不需要任何其他软件!还是以Proteus自带的例子,首先打开ARES 7 Professional软件打开*:\Program Files\Labcenter Electronics\Proteus 7 Professional\SAMPLES\Schematic & PCB Layout\Cpur.LYT先用输出生成制造用的gerber文件,点Output-> Gerber/Excellon Output...弹出CADCAM (Gerber and Excellon)Output设置对话框按默认设置点击OK。

最后将生产的文件整理为如下文件夹,将相应文件拷贝其中,为以下工作提供方便!打开Altium软件首先需要新建一个CAM Document之后点击File -> Import -> Gerber 导入ARES 7 Professional生成的Gerber文件在弹出对话框按自述文件设置导入的Gerber文件相关内容之后弹出日志及导入的效果,0个错误,0个警告!接下来我们要导入钻孔文件,选择File -> Import -> Drill弹出File Import - NC Drill弹出Import Drill Data设置对话框,按照自述文件进行相关设置弹出日志对话框,同样是0个错误,0个警告!放大以后我们可以看到孔已经添加上了。

ORCAD PCB转换为Protel 99se/ Protel DXP之PCB

一:转换到Protel 99se

1,准备工作。

准备一个.MAX文件,如图1。

图1

2, 打开Protel 99se,新建一个PCB文件,并且打开.PCB。

如图2。

图2

3,选择File->import。

选择1中的.MAX文件,点击OK。

出现如图

3,弹出对话框。

图3

在出现的对话框Option中选择FABDWG和NOTES为任意一层。

点击OK按键,即可生成PCB文件。

如图4。

图4

注意:1,在第3步中可以选择ORCAD的层颜色(USE orCAD Color Setting)或选择Protel 99se默认的层颜色。

2,如果不选择FABDWG和NOTES为任意一层,则不能生成PCB文件,同时也会提示出错.

4,转换成功!!!!!!可以在PROTEL 99SE 里修改电路图。

二:转换到Protel DXP/2004

1,准备工作.准备一个.MAX文件,如上步骤1

2,打开Protel DXP或Protel 2004,选择打开,选择1中的.MAX文件,并打开。

3, 同上第三步,第四步。

4,保存格式为.PCB格式。

EMAIL:whqzgkd@。

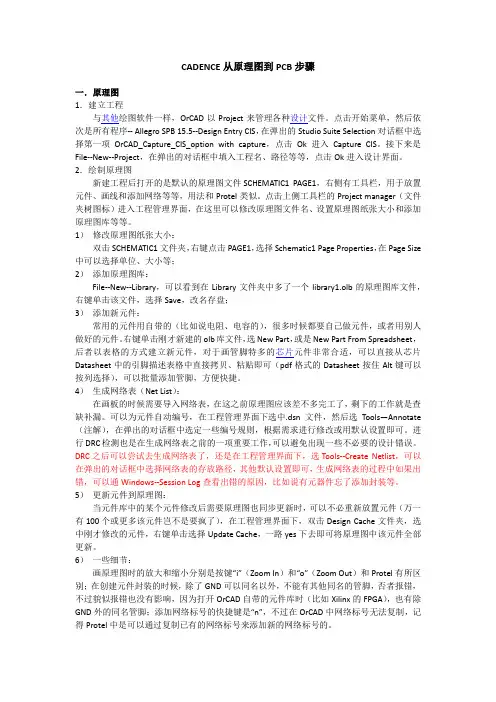

CADENCE从原理图到PCB步骤一.原理图1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第一项OrCAD_Capture_CIS_option with capture,点击Ok进入Capture CIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Project manager(文件夹树图标)进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size 中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

4)生成网络表(Net List):在画板的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。

钻孔图的导出步骤:首先要给每一种VIA定义一个字母。

Manufacture\NC\Drill Customization。

在Symbol Characters里给每一个VIA定义一个字母,注意不能重复,其他数值禁止修改。

(如果在做PAD的时候定义过字母,那就只需检查一下是否有重复的。

)然后,选Manufacture\NC\Drill Legend。

一定要在Output unit里选尺寸单位。

其他选项默认。

点OK后放在PCB板的旁边。

(检查这个表的字母和外框形状是否有重复的。

)金属化孔和非金属化孔文件的导出步骤:选Manufacture\NC\NC Drill。

首先在NCParameters里设置:Format里前面的选3后面的选5。

(即整数位3,小数位5。

和Artwork里的设置要一样。

)Coordinates里选 Absoiute。

Output units 里选英寸或毫米。

然后勾选1和3项。

(即省首零,和Artwork里的设置要一样。

)然后Close。

回到NC Drill画面。

勾选1、2、3项。

点Drill即可。

会在PCB文件的路径下产生3个文件,后缀名为drl的2个和1个叫nc_tools_auto.txt的文件。

要交给板厂的。

Gerber导出步骤1、首先在Artwork里把所有要出底片的层定义好。

建立每个层的文件夹。

比如:TOP、BOTTOM、L2、L3、SM-TOP、SM-BOT、SS-TOP、PT-TOP、Outline、Drawing 等等。

然后,打开每个文件夹所需要的那些层。

比如:Drawing文件夹里,要打开:Board Geometry里的Outline层。

Manufacturing里的Nclegend-*-*层、Ncdrill_Legend层、Ncdrill_Figure层。

其余的层全部关闭。

然后对着Drawing 文件夹点击鼠标右键,选Match Display。

这些层就被定义到文件夹里了。

Cadence从原理图到PCB的流程图:一.原理图1.建立工程2.绘制原理图3. 生成网络表(Net List):在画板的时候需要导入网络表,在这之前可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate;再进行DRC检测。

DRC之后可以尝试去生成网络表了,在工程管理界面下,选Tools--Create Netlist,二.PCB1. 打开PCB Editor,在弹出的对话框中选择Allegro PCB Design GXL(legacy),然后点击Ok进入PCB编辑器。

接下来就是利用向导建立电路板了,包括确定板子的大小、层数、形状等等参数。

File-new 在弹出的对话框中的Drawing Type选择Board(wizard),然后确定文件名,Browse存盘路径等,最后点Ok进入向导。

注意:板子的路径应该和前面生成网表的路径保持一致。

2.导入网络表接上一个步骤,将网络表导入到刚建好的PCB中。

在此之前还有一个很重要的工作要做,就是指定PCB封装的路径。

点击Setup--User Preferences,在弹出对话框中的Categories中选中Design_paths,分别为padpath和psmpath指定路径,即将PCB元件封装路径添加到padpath和psmpath中,以告知Allegro从指定的路径寻找封装。

元件的PCB封装需要自己做或是直接用别人做好的,封装准备好后往PCB 中导入网络表,点击File--Import--Logic,在Import directory中指定在原理图部分生成的网络表文件路径,其他设置使用默认值即可,点击Import Cadence即可导入网络表。

3.叠层设计,规则设定,布局布线暂时简单描述下元件的放置,布局,布线,具体的叠层设计,设计规则等后面再详细补充3.1 元件放置成功导入网络表之后,放置元件。

点击菜单Place--Quickplace,在弹出的对话框中使用默认设置,点击Place按钮即可完成元件的放置。

CADENCE从原理图到PCB步骤一(原理图1(建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第一项OrCAD_Capture_CIS_option withcapture,点击Ok进入Capture CIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2(绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Project manager(文件夹树图标)进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1) 修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size中可以选择单位、大小等;2) 添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;3) 添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

4) 生成网络表(Net List):在画板的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。

Cadence从原理图到PCB的流程图:一.原理图1.建立工程2.绘制原理图3. 生成网络表(Net List):在画板的时候需要导入网络表,在这之前可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate;再进行DRC检测。

DRC之后可以尝试去生成网络表了,在工程管理界面下,选Tools--Create Netlist,二.PCB1. 打开PCB Editor,在弹出的对话框中选择Allegro PCB Design GXL(legacy),然后点击Ok进入PCB编辑器。

接下来就是利用向导建立电路板了,包括确定板子的大小、层数、形状等等参数。

File-new 在弹出的对话框中的Drawing Type选择Board(wizard),然后确定文件名,Browse存盘路径等,最后点Ok进入向导。

注意:板子的路径应该和前面生成网表的路径保持一致。

2.导入网络表接上一个步骤,将网络表导入到刚建好的PCB中。

在此之前还有一个很重要的工作要做,就是指定PCB封装的路径。

点击Setup--User Preferences,在弹出对话框中的Categories中选中Design_paths,分别为padpath和psmpath指定路径,即将PCB元件封装路径添加到padpath和psmpath中,以告知Allegro从指定的路径寻找封装。

元件的PCB封装需要自己做或是直接用别人做好的,封装准备好后往PCB 中导入网络表,点击File--Import--Logic,在Import directory中指定在原理图部分生成的网络表文件路径,其他设置使用默认值即可,点击Import Cadence即可导入网络表。

3.叠层设计,规则设定,布局布线暂时简单描述下元件的放置,布局,布线,具体的叠层设计,设计规则等后面再详细补充3.1 元件放置成功导入网络表之后,放置元件。

点击菜单Place--Quickplace,在弹出的对话框中使用默认设置,点击Place按钮即可完成元件的放置。

Orcad16.5原理图转PADS logic原理图方法在将Cadence公司的Orcad16.5原理图文件转成PADS logic原理图时,需要经过以下三个步骤:(1)将Orcad16.5原理图文件另存为低版本Orcad16.2原理图文件,文件后缀名为.dsn;(2)在PADS logic软件中打开Orcad16.2原理图文件,并将其另存为PADS logic原理图文件,文件后缀名为.sch;转换后得到的PADS logic原理图文件除了在文件属性方面是Logic原理图文件后,其仍然具备Orcad16.2原理图文件的特点。

例如,在Orcad16.2原理图文件中存在原理图分层结构,而Logic 不存在该结构。

但是由于两种软件的原理图兼容,因此,在Orcad16.2原理图中出现的符号仍然可以在PADS logic中打开,但是PADS Logic本身可能没有该符号或者该符号异于Orcad16.2原理图符号(例如,两种软件的接地符号、电源符号、换页连接符等就不一样)。

因此,转换后得到的Logic原理图文件并不能直接使用,需要进一步修改为标准PADS logic原理图文件。

(3)在PADS logic中新建一个原理图文件,然后将转换后得到的Logic原理图文件复制到该原理图中,这时发生一个很有意思的现象:将原有Logic 原理图文件粘贴到该原理图中时,原Orcad16.2原理图符号竟然变成了Logic 本身的原理图符号(例如,接地符号、电源符号、换页连接符变成Logic原理图符号)。

在此基础上,用Logic中的元件替换转换后原理图文件中的符号即可。

将该文件进行修改并保存,即可得到最终的标准Logic原理图文件。

对于由Protel99se原理图文件转换后得到的PADS logic原理图文件,也存在上述步骤(2)提到的问题,因此也可以用上述步骤(3)来解决。

温馨提示:在将Orcad16.2原理图文件转换后得到的PADS logic原理图文件在局部一些地方跟原有Orcad16.2原理图文件有差异,这时需要对转换后得到的原理文件进行小范围修改,以保证原始设计文件在Logic中真实展现。

很多人只会用protel但是有的时候别人的图是cadence画的,比较头疼。

今天闲着没事打开protel看看他能不能打开cadence的原理图。

终于发现窍门了。

我用的是cadence16.3 直接用altium densigner导入不了得先转换成15.5的格式。

打开ad6.9使用导入向导

下面的一路next

原文地址:cadence16.5中差分规则的设置作者:秋天的雨

在高速的PCB不嫌重,往往有很多的差分走线,差分对之间必须要保证线宽、线距、线长等满足一定的要求,这就需要对差分走线进行规则的约束设置。

我们以一个实例进行差分对之间约束规则的设置:

打开PCB,在菜单栏,以此打开setup->constraints->constraint manager,打开约束管理器,然后再点击electrical constraints->NET->routing->wiring,然后选中要设置差分规则的差分对(如:CS_AOUT_LN,CS_AOUT_LP),然后右键,选择create->differential pair,弹出如下图所示对话框:

默认,然后点击create,将创建一个命名为CS_AOUT_L的差分属性。

然后我们在electrical constraints->NET->routing->differential pair中可以看到设置的差分属性,然后需要根据自己电路板的实际情况对它进行设置:

这样,命名为CS_AOUT_L的差分对就设置好了。

设置差分对还有其他的方法,这里只记录最常用的一种设置方法,而且这样设置的差分对优先级是最高的。

在PCB中,我们可以产看设置的差分对设置情况:

以同样的方法,可以进行其他差分对的设置。

/s/blog_535614070101t5dm.html。