低噪声频率合成技术研究

- 格式:docx

- 大小:69.27 KB

- 文档页数:7

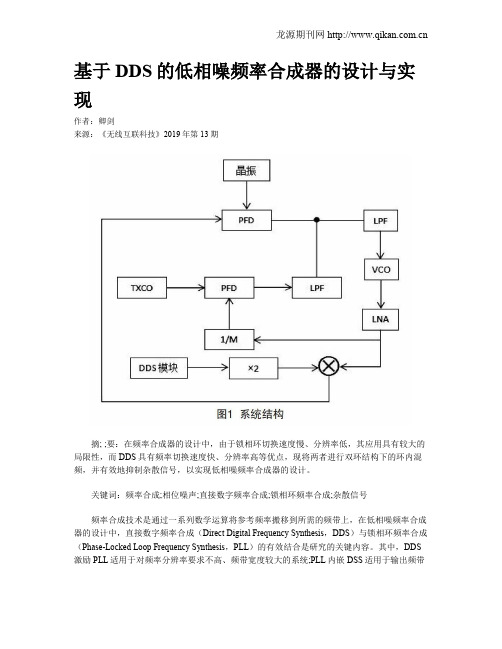

基于DDS的低相噪频率合成器的设计与实现作者:卿剑来源:《无线互联科技》2019年第13期摘; ;要:在频率合成器的设计中,由于锁相环切换速度慢、分辨率低,其应用具有较大的局限性,而DDS具有频率切换速度快、分辨率高等优点,现将两者进行双环结构下的环内混频,并有效地抑制杂散信号,以实现低相噪频率合成器的设计。

关键词:频率合成;相位噪声;直接数字频率合成;锁相环频率合成;杂散信号频率合成技术是通过一系列数学运算将参考频率搬移到所需的频带上,在低相噪频率合成器的设计中,直接数字频率合成(Direct Digital Frequency Synthesis,DDS)与锁相环频率合成(Phase-Locked Loop Frequency Synthesis,PLL)的有效结合是研究的关键内容。

其中,DDS 激励PLL适用于对频率分辨率要求不高、频带宽度较大的系统;PLL内嵌DSS适用于输出频带窄、频点少的系统[1]。

而本研究应用的是DDS与PLL环内混频,并通过增加环路优化以达到更好的设计要求。

现对详细的研究内容报告如下。

1; ; 研究目的与意义在频率合成技术不断发展的今天,按照工作原理可以将其分为直接频率合成(Direct Frequency Synthesis,DS)、PLL以及DDS 3种,DS主要利用混频、倍频以及分频等方法进行频率的处理以获得所需的频率信号,具有结构简单、运算速度较快的优点,但由于其结构较为简单,在获得所需输出的过程中往往需要使用滤波器进行信号质量改善,但难以处理滤波器中的噪声。

PLL属于自动控制系统负反馈控制电路中的一种,其同样具有转换速度慢、分辨率低等缺点,在实际应用中具有较大的局限性。

而DDS则是目前使用最多的一种频率合成技术,其基于相位累积进行频率合成,转换速度快、分辨率高;同时,DDS由数字方法进行频率合成,因此,具有小型化、集成化的特点,市场应用前景较好[2-3]。

第8卷 第1期 信 息 与 电 子 工 程 Vo1.8,No.12010年2月 INFORMATION AND ELECTRONIC ENGINEERING Feb.,2010 文章编号:1672-2892(2010)01-0033-03低相噪毫米波频率合成器设计廖梁兵1,2,邓贤进2,张红雨1(1.电子科技大学 电子工程学院,四川 成都610054;2.中国工程物理研究院 电子工程研究所,四川 绵阳621900)摘 要:简要介绍毫米波频率合成器的重要性,分析两种毫米波频率合成器实现方案的优劣,综合其优点,并采用直接数字频率合成(DDS)技术,提出毫米波频率合成器的设计方案。

进行方案系统实验,结果表明,相位噪声为-85 dBc/Hz@10 kHz ,提升了整个毫米波通信系统的性能。

关键词:毫米波;频率合成;相位噪声;频率分辨力中图分类号:TN741 文献标识码:ADesign of low phase noise millimeter wave frequency synthesizersLIAO Liang-bing 1,2,DENG Xian-jin 2,ZHANG Hong-yu 1(1.School of Electronic Engineering,UESTC, Chengdu Sichuan 610054,China;2.Institute of Electronic Engineering,China Academy of Engineering Physics,Mianyang Sichuan 621900,China)Abstract:The importance of millimeter wave frequency synthesizers was introduced briefly, theadvantages and disadvantages of two schemes of millimeter wave frequency synthesizers were analyzed,and a final design scheme of millimeter wave frequency synthesizer was put forward by the combination ofthese advantages and the Direct Digital Synthesis(DDS) technology. A systematic experiment of thescheme was performed, and the results showed that the phase noise was -85 dBc/Hz@10 kHz, whichindicated that the performance of the whole millimeter communication system had been improved.Key words:millimeter wave;frequency synthesizers;phase noise;frequency resolution近年来,由于频谱资源日益紧张,毫米波频段的频谱资源得到极大开发。

X波段低相位噪声宽带宽频率合成器的研究的开题报告前言:随着现代无线通信技术的广泛应用,对频率合成器的要求也越来越高。

特别是在X波段,对于低相位噪声、宽带宽和高频率合成精度的要求更加严格。

因此,本文将研究X波段低相位噪声宽带宽频率合成器。

研究内容:本文主要研究X波段低相位噪声宽带宽频率合成器的设计和实现。

具体内容包括以下几个方面:1.理论研究:对于X波段频率合成器的特点、要求和原理进行深入研究,分析当前常用的频率合成器的优缺点,为设计提供理论依据。

2.设计和仿真:基于理论研究的结论,设计X波段低相位噪声宽带宽频率合成器的电路,并采用仿真软件进行仿真验证。

3.实验验证:通过搭建实验平台,对设计的X波段低相位噪声宽带宽频率合成器进行实际测试,并与仿真结果进行比较分析,验证设计方案的可行性和有效性。

预期目标:本文预期达到的目标是设计一种X波段低相位噪声宽带宽频率合成器,并实现相应的硬件电路。

该频率合成器具有以下特点:1.低相位噪声:在X波段频率范围内,相位噪声小于-120 dBc/Hz。

2.宽带宽:频率合成器的带宽能够满足X波段的需求,具体带宽将在仿真和实验中确定。

3.高频率合成精度:频率合成器的输出频率精度小于1%。

4.较高的输出功率:频率合成器的输出功率大于10 dBm。

5.较小的尺寸和功耗:为了满足实际应用的需要,频率合成器将采用较小的芯片尺寸和尽量少的功耗。

结论:本文是对X波段低相位噪声宽带宽频率合成器的研究。

通过理论研究和实验验证,设计一种具有低相位噪声、宽带宽、高频率合成精度、较高输出功率、较小的尺寸和功耗的频率合成器,其可用于X波段的无线通信系统中,对于提高通信质量、保证通信安全、减少通信干扰等方面都具有重要的意义。

低噪声频率合成技术研究

【摘要】:本文介绍了低噪声频率合成单元的基本原理和主要电路单元对噪声的影响,也介绍了一些相位噪声优化的方法。

【关键词】相位噪声频率合成信号发生器

一、低噪声频率合成单元

从传统意义上来说,信号发生器类频率合成单元基本包括参考环、小数环、微波本振环、YO环四个部分组成。

参考环主要用于给小数环和微波本振环提供超低相位噪声参考信号,在参考信号发生电路的设计上相位噪声是首要考虑的因素。

小数环由VCO,小数分频电路、鉴相电路、积分电路组成。

小数分频采用FPGA实现,频率范围3GHz~6GHz,经分频后作为基波混频环的参考信号。

本振环主要作用是产生大步进低噪声本振信号。

参考信号与微波本振信号进行混频,产生中频信号与参考信号进行鉴相通过环路滤波器驱动VCO,产生3~6GHz的合成信号。

微波本振环采用梳谱混频,需要对VCO进行准确的预置,本振环中的测频单元通过对预置频率的测量,反馈给预置DAC,保证预置的准确性。

YO环由鉴相电路、积分电路、YIG振荡器和混频下变频电路构成。

来自微波本振环的本振信号与YTO反馈信号进行混频,中频信号与小数环输出的分频信号进行鉴相,经积分电路驱动YTO实现环路锁定。

二、锁相环路中各部分电路对噪声的影响

在锁相环设计中,最主要的噪声来源有两方面,一方面是参考信号或反馈信号通过鉴相器引入的噪声,另一个是VCO自身振荡产生的噪声。

1、锁相环电路中振荡器的噪声

在锁相环路中,选择什么样的VCO电路主要取决于环路要求达到何种程度的

性能。

目标是达到尽可能低的相位噪声,也就是说VCO是产生这些干扰的主要来源,是影响频率合成器输出信号频谱纯度的主要部件之一。

影响VCO输出信号相位噪声的主要因素有两个:参考信号的相位噪声和VCO

本身的相位噪声。

这种情况下,假设锁相环环路是线性的、VCO是一不产生噪声的理想部件,外加的等效于VCO产生的相位噪声。

图1考虑VCO相位噪声的锁相环

如果输入相位噪声和VCO的相位是不相关的,那么输出相位噪声的单边带谱

密度可表示为:

由于锁相环环路传输函数的低通特性,可以得出如下两个近似式:

于是,对于小的偏离载波频率,或者说在环路带宽之内,有

,

对于大的偏离载波频率,或者说在环路带宽之外,有

,

由式看出,锁相环环路对VCO的相位噪声而言是一个“高通”滤波器。

VCO

的这种特性是锁相环环路对器相当于一个负反馈回路。

环路滤波器阻止高频通过,所以反馈作用就小,而对于低频则允许通过,所以负反馈作用就大。

这就是说,

VCO的相位噪声在环路带宽内的低频范围可以通过锁相环作用降低,而在这以外

则不变。

上述结果对VCO的应用是很重要的,环路输入参考信号的相位噪声要低,VCO本身的相位噪声也要低,并在环路带宽内尽量保持;选择适当的环

路带宽,以便抑制VCO本身的相位噪声,而且对抑制来至VCO调谐电压控制线上

的干扰也是有利的。

2、锁相环路中分频器对噪声的影响

锁相环路中加入可变除N分频器可以解决两个很关键的问题。

首先是不改变

输入参考频率就可以改变VCO的输出频率,为实际应用提供了方便;其次是提高

了输出频率的分辨率,降低了鉴相的参考频率。

为了分析可变除N分频器对环路

噪声的影响,在这里仍然把分频器看作是一个理想部件,而本身的相位噪声用外

加于输出端的来表示。

同时由于分频的原因,在其输出端还有。

如图所示。

图2有可变除N分频器的环路噪声

有可变除N分频器锁相环相位噪声谱密度函数为:

环路中加入可变除N分频器之后,对VCO来说,它实际就变成了倍频器。

在

低频率偏移时,,相对是小的,所以噪声增加了 .这个结果告诉我们必须选择合适的N。

如果N太大,可以考虑采用双环、三环,甚至多环把N的影响降低。

3、锁相环路中混频器对相位噪声的影响

在使用N分频器的锁相环中,相对参考信号,输出信号相位噪声理论上会恶

化20logN。

但是在很多情况下,分频器对相位有采样效果,使相位噪声在频域上

拓展,当输入噪声带宽较大时,就会发生混叠,从而使噪声抬高。

通过锁相环的

传递将影响到输出信号。

常见多模分频器的单边带相位噪声一般在-150~-

140dBc/Hz,这样除了噪声要恶化20LogN外再加上附加相位噪声的影响,采用具

有可变除N分频器的锁相环难以达到设计要求。

而采用混频器的锁相环中则可以

避免这个问题。

图3表示混频器对输入信号的作用,和

是混频器的两个输入信号;则混频器的输出信号是。

混频器在对频率v

01和v

02

进行加减的同时,两个信号的相位和也进行

了加减。

因此,混频器可以看作是相位的加法(或减法)器。

图3混频器输入信号的作用

根据以上分析,若输出的本振信号足够好,经过混频器后锁相环反馈信号理

论上最多恶化3dB,只要参考信号及本振信号相位噪声足够低,则锁相环输出信

号的相位噪声就可以做得很低。

因此,采用混频锁相方式可实现低相噪的频率合成。

4、锁相环路中鉴相器对相位噪声的影响

鉴相器也是锁相环环路的关键部件之一。

作为鉴相器有两个主要问题要考虑:第一个问题是输入信号泄露,或者叫做干扰;第二个问题是鉴相器对输入信号加

噪声的响应。

我们假定锁相环环路是线性的,鉴相器是理想的。

鉴相器引入的噪

声干扰用一外加输出端的等效噪声干扰电压代替,如图4所示。

图4考虑鉴相器干扰时的锁相环

锁相环输出相位的单边带谱密度可表示为:

(1)

环路带宽之内,,,所以有

(2)

锁相环对鉴相器的泄露呈“低通”特性。

也就是说,干扰电压的频率越低,越容易输出,抑制性也越差。

反之,对于较高的干扰电压频率,抑制性也较好。

为了减少鉴相器的泄露影响,可采取一下措施:增大,降低,以提高边带抑制能力;选择合适的窄带环路,及减小和;提高鉴相频率,降低鉴相输入信号幅度;在低通滤波器之后加干扰频率的陷波器。

三、相位噪声优化方案

1、基于基波变频的YO环设计

采用基波变频方案,YO反馈信号与频率接近的本振信号混频,得到

100MHz~200MHz的中频信号。

基波变频避免了旧方案取样变频发生的噪声恶化问题。

2、低噪声微波本振环设计

频率范围要提高到微波波段,达到3~10GHz,为YO环基波变频提供变频本振,而且单边带相位噪声要非常低,要优于YO环最终输出的相位噪声的目标才能在变频过程中不对带内噪声产生恶化。

该环路中也采用基波变频的方案,作为

变频本振的微波多点参考信号为800MHz步进,为了实现VCO锁相输出为200MHz 步进,采用100MHz、300MHz带个中频,经过开关分频统一用100MHz频率鉴相。

3、低噪声微波多点参考合成电路设计

本振环需要低噪声微波参考信号作为变频本振,其特点是相位噪声要求高而且点太多,频率又高,达到4.8~10GHz。

实现方案以参考环输出的1GHz为参考信号,采用倍频、混频的避免相位噪声恶化的变频方式,实现了微波多点参考合成。

4、小数环设计

YO环要求来自小数环的高分辨率鉴相参考信号频率100~200MHz,单边带相位噪声@10kHz频偏优于-125dBc/Hz。

旧方案VCO输出500~1000MHz相位噪声为-95dBc/Hz,分频到100~200MHz为-109dBc/Hz,无法满足要求。

新方案中主要采取了两项新技术,一是使用更高频率的VCO,二是提高鉴相频率,使相位噪声指标得到有效提升。

1.

达到的效果

根据以上理论分析,通过对影响相位噪声的近端、远端指标的电路进行优化设计,改进后达到了比较理想的效果。

相位噪声指标对比(单位dBc/Hz)

参考文献

【1】王家礼,孙路.频率合成技术[M].西安:西安电子科技大学出版社,2009.

【2】田佳可,颜锦奎,等.宽频带频率合成器的编程与分析[J].电子测量技术,2014,37(5):47-51.

【3】张厥盛,郑继禹等.锁相技术[M].西安:西安电子科技大学出版社,1992.。