基于FPGA的串行接口芯片的设计与应用

- 格式:pdf

- 大小:294.44 KB

- 文档页数:4

基于FPGA的USB接口IP核设计USB(通用串行总线)作为一种外设连接技术,是计算机外设连接技术的重大变革,USB具有速度快、通用性好、扩展性强、功耗低、稳定、易开发等众多优点,在实践中获得了广泛的应用,逐步成为PC机的一种标准接口。

USB接口控制芯片是实现USB设备与主机建立通信所必须的芯片,目前国内的USB开发者所采用的芯片都是由国外的芯片商所提供,如Cypress、NEC、Motorola等大的IC设计公司,价格较贵。

由于USB的广泛应用,国内外众多科研机构和集成电路设计公司都把目光投向USB这项具有广阔市场前景的技术。

USB内核(USB Core)是USB接口控制芯片的关键模块,设计一个稳定、高速的USB内核更是芯片成功推向市场的前提。

1 USB通信原理USB通信逻辑上分成了3层:信号层、协议层和数据层。

信号层用来实现在USB 设备和主机的物理连接之间传输位信息流的信息。

逻辑层用来实现在USB设备和USB主机端的协议软件之间传输包字节流的信息,它们在信号层被编码成NRZI位信息后传送出去。

数据传输层用来实现在USB主机端的客户端驱动程序和设备端的功能接口之间传输有一定意义的信息,这些信息在协议层被打包成包格式。

1.1 传输的基本单元包(Packet)是USB系统中信息传输的基本单元。

结构,如图1所示,根据USB 规范,包的类型有:令牌包、数据包、握手包和专用包。

USB总线操作(通讯过程)都可以归结为3种包的传输:令牌包、数据包和应答包。

任何操作都是从主机开始的,主机以预先排好的时序,发出一个描述操作类型、方向、外设地址以及端点号,称之为令牌包Foken Packet。

然后由在令牌中指定的数据发送者发出一个数据包Data Packet或者报告它没有数据可以传输。

而数据的目的地一般要以一个应答包Handshake Packet做出响应表明传输是否成功。

1.2 事务处理事务处理(Transaction)是指USB总线上数据信息的一次接收或发送的处理过程。

基于Verilog的FPGA与USB 2.0高速接口设计2009-04-28 14:41:36 来源:与非网关键字:Verilog FPGA USB2.0高速接口设计0 引言USB(通用串行总线)是英特尔、微软、IBM、康柏等公司1994年联合制定的一种通用串行总线规范,它具有数据传输速度快,成本低,可靠性高,支持即插即用和热插拔等优点,迅速得到广泛应用。

在高速的数据采集或传输中,目前使用较多的都是采用USB 2.0接口控制器和FPGA或DSP实现的,本设计在USB 2.0接口芯片CY7C68013的Slave FIFO模式下,利用FPGA作为外部主控制器实现对FX2 USB内部的FIFO进行控制,以实现数据的高速传输。

该模块可普遍适用于基于USB 2.0接口的高速数据传输或采集中。

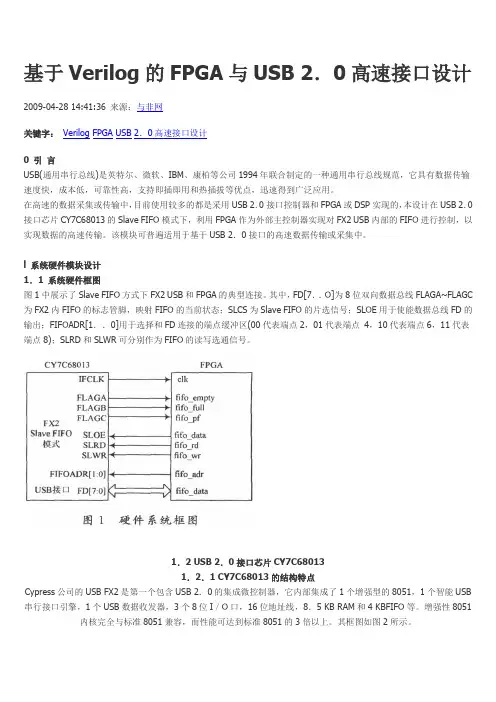

l 系统硬件模块设计1.1 系统硬件框图图1中展示了Slave FIFO方式下FX2 USB和FPGA的典型连接。

其中,FD[7..O]为8位双向数据总线FLAGA~FLAGC 为FX2内FIFO的标志管脚,映射FIFO的当前状态;SLCS为Slave FIFO的片选信号;SLOE用于使能数据总线FD的输出;FIFOADR[1..0]用于选择和FD连接的端点缓冲区(00代表端点2,01代表端点4,10代表端点6,11代表端点8);SLRD和SLWR可分别作为FIFO的读写选通信号。

1.2 USB 2.0接口芯片CY7C680131.2.1 CY7C68013的结构特点Cypress公司的USB FX2是第一个包含USB 2.0的集成微控制器,它内部集成了1个增强型的8051,1个智能USB 串行接口引擎,1个USB数据收发器,3个8位I/O口,16位地址线,8.5 KB RAM和4 KBFIFO等。

增强性8051内核完全与标准8051兼容,而性能可达到标准8051的3倍以上。

其框图如图2所示。

1.2.2 CY7C68013的工作模式CY7C68013有Ports模式、Slave FIFO和GPIF三种接口方式。

基于FPGA的串行64B/66B编解码IP核设计与研究作者:庞志锋刘毅夫安国臣王晓君来源:《科技风》2018年第25期摘要:串行传输技术具有速度快,成本低的特点,被广泛应用于高速通信领域。

在高速串行系统中,FPGA器件结合了可编程性和高速I /O的优点,实现了高速,稳定的数字通信。

本文基于FPGA开发环境,在vivado开发平台上使用VHDL语言编程设计了64B/66B编解码的IP核,完成了关键模块的功能仿真验证,為高速串行传输系统提供了一种有效的设计方法,具有一定工程意义。

关键词:高速串行传输;VHDL;64B/66B编解码;IP核随着对电子系统吞吐量要求的日益提高,并行数据传输模式已不能满足高带宽应用的传输需求。

高速串行传输技术[1]具有带宽高,延时低,信号完整性好,可扩展性强等优点,已成为数据传输的主流技术,广泛应用于通信网络、数据存储、个人计算机、服务器和嵌入式控制等诸多领域。

广泛应用于通信网络、数据存储、个人计算机、服务器和嵌入式控制等诸多领域。

现场可编程门阵列(Field Programmable Gate Array,FPGA)比数字信号处理器处理速度快,FPGA能够处理复杂的高速逻辑,与专用芯片相比,开发周期更短,灵活性更高。

基于FPGA的系统设计验证具有稳定性高、成本低、处理速度快等优点,FPGA器件已经成为实现串行接口应用[2]的理想连接平台。

IP核(Intellectual property core),就是知识产权核,是一段可以实现特定电路功能的可重用模块,设计人员能够调用IP核来进行现场可编程逻辑门阵列的逻辑设计,能够减少开发周期。

本文主要是基于FPGA的开发环境中使用VHDL语言来设计实现64B/66B编解码[3]功能的IP核,通过加扰、解扰模块以及并串/串并转换[4]模块来设计高速串行传输系统。

1 64B/66B编解码64 B/66B编码是一种高性能的串行数据编码标准,它并不是真正的编码,而是一种基于扰码机制的编解码方式,是 IEEE推荐的10G通信标准编码方式。

基于FPGA的1553B总线接口技术研究与实现1553B总线是一种常用的数字串行接口协议,用于航空与军事应用中。

它是一种双向总线,可以实现数据传输、控制信息传递和命令控制等功能。

本文将介绍基于FPGA的1553B总线接口技术研究与实现。

FPGA(Field Programmable Gate Array)是一种数字逻辑芯片,可编程电路板,可以实现数字电路的设计和实现。

它具有灵活性高、可重构性强等特点,非常适合用于1553B 总线的接口设计和实现。

1553B总线接口是一种双绞线协议,其中包含了控制寄存器、数据缓冲区、状态寄存器等。

FPGA技术可以实现这些模块的设计和实现。

它可以通过GPIO接口实现数据总线、地址总线和控制总线的连接,从而实现数据的传输和控制。

二、1553B总线接口的设计1. 系统基本结构基于FPGA的1553B总线接口系统一般由CPU、1553B控制器、数据缓冲区等模块组成。

其中CPU可以选择ARM、MIPS等微处理器。

数据缓冲区可以采用FIFO缓存、双向缓冲存储器等。

1553B控制器可以采用硬件实现,也可以使用软件实现。

2. 数据传输流程基于FPGA的1553B总线接口系统的数据传输流程一般分为以下几个步骤:(1)主设备发送命令:主设备通过向控制寄存器中写入命令字,向从设备发出命令。

(2)从设备接收命令:从设备接收到主设备发出的命令后,开始执行相应的操作。

(3)从设备发送响应:从设备向主设备发送响应信息。

3. 系统的实现系统的实现需要编写相应的程序和硬件描述语言(VHDL)代码。

程序实现部分包括驱动程序和应用程序。

驱动程序主要用于CPU和控制器的通信。

应用程序主要用于控制1553B总线的数据传输和控制。

VHDL代码包括控制寄存器、数据缓冲区和状态寄存器等模块。

控制寄存器用于存储控制信息,包括命令字、地址信息等。

数据缓冲区用于存储数据信息。

状态寄存器用于存储状态信息,包括传输状态、接收状态等。

基于FPGA的SPI串行接口实时以太网实现【摘要】工业以太网,从控制网络的角度来看,属于一种新型的现场控制总线,正处于不断完善和发展中。

基于ENC28J60芯片的独立以太网控制器接口通信系统,不仅能实现嵌入式控制系统与以太网的互联,而且能够实时可靠地传输数据,其中包括新型实时以太网通信的原理、串行接口SPI的软硬件设计、TCP/IP 协议的选择及参数设置、TCP/IP通信测试。

【关键词】以太网;ENC28J60;SPI;FPGA1.引言为解决以太网的通信确定性问题,从而消除以太网直接应用于工业现场设备间通信的主要障碍和为以太网直接应用于工业现场设备间通信提供技术可能,需要高速的通信速率、全双工交换方式。

为了满足这些要求,采用了只有28引脚的业界标准串行外设接口(SPI)的以太网控制器ENC28J60,符合IEEE 802.3协议,可以提供相应的功能,不仅大大的简化了相关设计,而且减小占用空间。

控制器ENC28J60与主控制通过两个中断和自带的SPI实现通信,其数据传输速率高达10Mb/s。

其中ENC28J60内置集成MAC和10BASE_T PHY,可按业界标准的以太网协议可靠地接受信息报数据,而且内部具有可编程8KB双端口SRAM缓冲器,可减轻主控单元的内存负荷,提供灵活可靠的数据管理机制,大大地提高系统传输性能。

以太网是一种可实现LAN内的嵌入式器件与互联网的连接的联网技术。

拥有以太网功能的嵌入式系统,主控制单元便可通过网络分发数据,并遥控控制。

因以太网架构、性能、互操作性、可扩展性及开发简便等特点,已成为嵌入式网络应用的标准通讯技术。

但是实时以太网控制往往要求对某些变量的数据准确定时刷新。

在工业以太网的应用中,PC机上数据的双向传输,可采用现场可编程门阵列FPGA作为控制的硬件。

而且从系统集成角度上,对于带有SPI接口的ENC28J60芯片选用FPGA技术实现SPI的设计也是最优的选择。

满足编程灵活、集成度高、可移植性好、开发工具先进、设计成本低的优点。

基于FPGA的UARTl6550的设计1 引言UART(Universal Asynchronous Receiver/Transmitter,通用异步收发器)是用于控制CPU 与串行设备通信的芯片,将由CPU 传送过来的并行数据转换为输出的串行数据流。

将系统外部来的串行数据转换为字节,供系统内部使用并行数据的器件使用。

他可以在输出的串行数据流中加人奇偶校验位和启停标记,并对从外部接收的数据流进行奇偶校验以及删除启停标记。

常见UART 主要有INS8250,PC16450 和PCI6550,其中16550 发送和接收都带有16 B 的FIFO,为协调发送、接收端的速率匹配提供了更大的缓冲余地,同时也可以提高CPU 的使用效率,从而提高系统的整体性能。

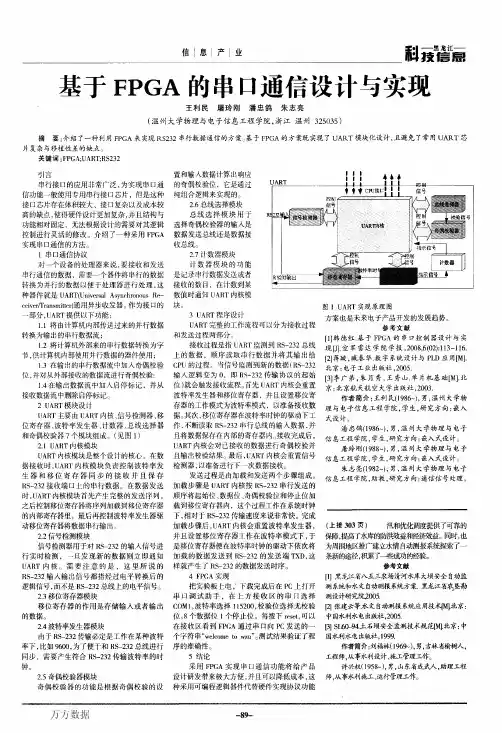

2 UART16550 的基本结构如图1 所示,UART16550 的基本结构由CPU 接口模块、波特率发生器、FIFO 控制器、发送/接收FIFO 和发送/接收模块共7 个部分组成。

CPU 通过UART 的CPU 接口模块配置整个UART,波特率发生器在CPU 写入初始值后产生需要的波特率,控制发送和接收模块在设定的波特率下工作。

CPU 通过接口模块向发送FIFO 内写入需要发送的8 位数据,同时发送模块开始读取FIFO 中的数据,并加入起始位、奇偶校验位和停止位后以串行发送的方式传输给串行接收设备。

接收模块时刻监视串行输入端口,发现有数据发送来的时候马上启动接收模块开始接收数据并有效的判断出奇偶校验位来检测数据的正确性,最后把剩下的8 位数据放入接收FIFO,并通知CPU 有数据进来进行接收。

异步串行通信协议的数据传输格式如图2 所示。

UART16550 的发送数据位可以选择为5~8 位,同时可以选择奇校验、偶校验或者不设置校验位,停止位可以约定为1,1.5 或2 位。

基于FPGA的智能串行通信板卡的设计与实现王剑博;胡晓吉【摘要】串行通信模块是每台计算机所必须的对外通信模块的一部分,但由于串行通信协议较多,串行接口也较多,所以,往往这部分模块需要占用较多的体积和资源。

将RS 232,RS 422和RS 485三种串行协议和同异步两种串行传输方式通过FPGA兼容于一块智能通信板卡上,通过上位机控制界面的控制,完成对8路串行通道的配置,并介绍了板卡的总体结构及硬件设计,展示了上位机控制界面的通信效果。

结果表明,该智能串行通信卡能够很好地完成多协议多方式的串行通信之间的切换,达到了预期的效果。

%Serial communication module is a part of external communication module which is necessary for every computer. However,because of too many serial communication protocols and interfaces,more resources and volumes are always occupied by the serial communication module. In this paper,three serial communication protocols(RS⁃232,RS 422 and RS 485)are com⁃patible with two serial communication modes (UART and HDLC) into an intelligent communication board through FPGA. The configuration of eight serial communication channels is completed under the control of the control interface of upper computer. The overall structure and the hardware design of the communication board are introduced in this article. At last,the communica⁃tion result of the upper computer control interface is displayed. The conclusion proves that this intelligent serial communication board can execute the switching between multi⁃protocol andmulti⁃mode,and meet the requirements of different kinds of serial communication as expected.【期刊名称】《现代电子技术》【年(卷),期】2015(000)007【总页数】4页(P39-42)【关键词】串行通信;串行协议;串行方式;FPGA;智能串行通信卡【作者】王剑博;胡晓吉【作者单位】华北计算技术研究所加固计算机产品事业部,北京 100083;华北计算技术研究所加固计算机产品事业部,北京 100083【正文语种】中文【中图分类】TN911-34串行通信作为计算机与其他设备之间广泛使用的一种通信方式,具有开发简单,抗干扰性强,传输距离远的特点。

基于FPGA的1553B总线接口设计 MIL-STD-1553 总线是美国20 世纪80 年代制定的第一个军用数据总线标准,它是一种串行的数据总线。

该总线标准自制定后广泛应用于军用飞机、车辆、船舶中,并鉴于其高可靠性和灵活性,逐渐应用在许多其他机动平台上。

1553B 是一种时分制指令/响应式多路传输数据总线,总线上的所有消息传输都由总线控制器发起,远程终端对发出的指令应给予回答(响应)并执行相关操作。

这种方式非常适合集中控制的分布式处理系统。

1553B总线通信系统是由总线控制器、远程终端、总线监控器三部分组成。

一个通信总线上最多可以挂32 个远程终端,传输介质采用屏蔽双绞线,对噪声等干扰有很好的抑制能力。

1553B 总线的数据传输率为1 Mb/s ,在一次消息传输中最多可以传送32 个字,所有单次传输的时间较短,具有很好的实时性。

在MIL-STD-1553 总线通信系统中,总线接口板是系统的关键部分,其中核心部分的接口电路是总线应用中的主要制约因素。

在1553B 总线得到广泛应用的今天,国内应用1553B 总线协议的通信模块的解决方案多采取基于进口1553B 总线协议芯片来开展相关设计,如UT 公司的UTl553B 协议芯片、DDC 公司的高级协议处理芯片BU-61580 等,虽然这些芯片能够完成协议功能,但价格昂贵、灵活性差,这些弱点在一定程度上限制了设计能力,因此提出一种新的基于嵌入式方法实现的1553B 数据总线接口逻辑。

1 系统总体设计方案 本文采用Xilinx 公司的FPGA 芯片作为协议处理核心器件,选用TI 公司的TMS320C5510 作为主处理器负责接收FPGA 处理过的数据和调度FPGA 的具体操作。

总体方案的系统结构如图1 所示。

1.1 模拟收发部分电路设计 由于1553B 总线上传输的是双极性的差分信号,主处理器不能直接接收来自总线上的数据,所以需要信号调制解调及电平转换电路。

基于FPGA的ASIC设计—RS232接口功能一、设计说明为了配合课程设计,完成RS232通信功能,以Verilog为硬件描述语言在FPGA开发板上实现串行通信的接受和发送模块,通过本项目掌握基于FPGA的ASIC设计的流程方法。

1. RS232介绍RS232是一种异步串行通信接口,RS232只是一个物理层的标准,只规定了信号物理特性,链路层的协议是UART,RS232接口的逻辑设计就是这部分内容。

其设置包括三部分:波特率、奇偶校验、停止位。

所谓波特率,指单位时间内传送二进制数据的位数,以位/ 秒为单位,是衡量串行数据传输快慢的重要指标。

如果某串口的波特率为115 200,指的是该串口以115 200bits/s 的速率在传输数据。

奇偶校验:是用来验证数据的正确性。

奇偶校验是通过修改每一发送字节(也可以限制发送的字节)来工作的。

在偶校验中,因为奇偶校验位会被相应的置1或0(一般是最高位或最低位),所以数据会被改变以使得所有传送的数位(含字符的各数位和校验位)中“1”的个数为偶数;在奇校验中,所有传送的数位(含字符的各数位和校验位)中“1”的个数为奇数。

奇偶校验可以用于接受方检查传输是否发送生错误——如果某一字节中“1”的个数发生了错误,那么这个字节在传输中一定有错误发生。

如果奇偶校验是正确的,那么要么没有发生错误要么发生了偶数个的错误。

停止位:是在每个字节传输之后发送的,它用来帮助接受信号方硬件重同步。

2. RS232的特性使用9针的"DB-9"插头(它一共有9个引脚,最重要的3个引脚是:引脚2 RxD (接收数据). 引脚3: TxD (发送数据). 引脚5: GND (地)). 允许全双工的双向通讯,最大可支持的传输速率为10KBytes/sRS232通信线上的电平RS-323标准对逻辑电平的定义。

对于数据(信息码):逻辑“1”(传号)的电平低于-3V,逻辑“0”(空号)的电平高于+3V;对于控制信号;接通状态(ON)即信号有效的电平高于+3V,断开状态(OFF)即信号无效的电平低于-3V,也就是当传输电平的绝对值大于3V时,电路可以有效地检查出来,介于-3~+3V之间的电压无意义,低于-15V或高于+15V的电压也认为无意义,因此,实际工作时,应保证电平在±(3~15)V之间。

基于FPGA芯片的SERDES接口电路设计串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。

随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。

起初,SERDES 是独立的ASSP 或ASIC 器件。

在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES 收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

1 硬件接口:硬件的接口如上图所示,主要包括发送与接收模块。

发送模块包括8b/10b编码器,并串转换器,锁相环(PLL)频率合成器和发送器,接收模块包括8b/10b解码器,Comma 检测器,串并转换器,时钟数据恢复器(CDR)和接收器。

8b/10b编码器用于将从上层协议芯片发送过来的字节信号映射成直流平衡的10 位8b/10b 编码,并串转换用于将10 位编码结果串行化,并串转换所需的高速、低抖动时钟由锁相环提供,发送器用于将CMOS电平的高速串行码流转换成抗噪声能力较强的差分信号,经背板连接或光纤信道发送到接收机。

在接收端,接收器将接收到的低摆幅差分信号还原为CMOS 电平的串行信号,CDR 从串行信号中抽取时钟信息,完成对串行数据的最佳采样,串并转换利用CDR 恢复的时钟,将串行信号转换成10 位的并行数据,Comma 检测器检测特殊的Comma 字符,调整字边界,字边界正确的并行数据经过8b/10b 解码,还原为字节信号,传送到上层协议芯片,完成整个信息传输过程。

实际的设计中,CDR部分是由纯逻辑电路完成的,为设计的核心的部分,下面将介绍数字CDR在HR03的实现方案。

基于国产FPGA的高速SRIO接口设计与实现摘要:随着技术发展水平的提升,接口芯片国产化要求越来越高,研究人员在国产PFGA基础上设计SRIO接口,能够有效提高国产芯片的使用效果。

因此研究人员应该继续加大对SRIO接口的研究力度,基于FRGA开展内部功能模块设计工作,还需对SRIO接口展开设计,从而提高接口验证的准确性。

本文首先分析SRIO接口的基本情况,其次探讨SRIO接口逻辑设计实现情况,以期对相关研究产生一定的参考价值。

关键词:国产FPGA;高速SRIO接口设计;实现引言:在国产FRGA技术发展水平不断提高的背景下,一些研究人员在FPGA基础上研发设计了高速SRIO接口,推动了我国国产芯片的高速发展。

以往在应用芯片时,主要依赖于进口,但是进口芯片价格高昂,在推动国产发展的背景下,基于国产FPGA的SRIO接口应运而生,使得我国很多企业不再需要使用进口芯片,可以使用价格更为低廉的国产化芯片,能够在促进国产芯片发展的同时,避免企业在芯片接口处花费过多的资金。

1国产FPGA平台本文研究的国产FPGA平台出自紫光同创电子有限公司,性能比较好,属于具备完全自主产权体系、自主开发的套件,这种芯片构成部分主要包括逻辑单元CLM、18KB存储单元DRM、算数处理单元APM、高速串行接口模块HSST、IO模块以及丰富的时钟资源。

这种国产FPGA芯片一般需要直接内置在高速串行模块HSST中,数据传输速率能够达到每秒钟6.375 Gb/s,可以灵活使用各类串行协议标准,FPGA内置的HSST接口可以被视为SRIO接口的硬件基础。

2SRIO接口的基本情况SRIO接口属于开放式比较强的互联网体系结构,这种接口类型属于能够进行交换的新一代高速互联技术,可靠性比较高、延时性比较低,管脚数比较少,接口频率比较高,端口宽度能够进行升级管理,运用这种接口可以顺利解决嵌入式系统串行数据出现的平面连接问题、高速串行数据传输安全稳定性问题、时效性问题。

基于FPGA的高速以太网接口设计和实现共3篇基于FPGA的高速以太网接口设计和实现1以太网是广泛使用的局域网(LAN)标准,其速度和带宽都非常高,不断发展和改进以满足用户需求。

在现代数据中心和云计算环境中,以太网已变得更加重要,因为它可以提供高速、低延迟和灵活性,使得多个系统之间的通信更加容易和高效。

为了满足这些需求,FPGA成为了一种重要的硬件平台,通过实现高速以太网接口,提供灵活的网络连接。

FPGA是一种可编程的硬件平台,集成了大量的可编程逻辑单元和DSP 资源,可以快速实现各种电路和系统。

基于FPGA的高速以太网接口设计具有以下优点:1. 速度高:基于FPGA的以太网接口可以支持高达40Gbps的数据传输速度,远远快于传统的以太网接口。

2. 低延迟:FPGA内部的可编程逻辑单元可以实现更快的数据处理,并且可以在硬件层面提供更快的响应时间,从而降低网络延迟。

3. 灵活性:FPGA具有可编程性和可重构性,可以根据需要进行实时调整和修改。

此外,FPGA可以通过工具链进行设计和优化,可适应各种硬件需求。

基于FPGA的高速以太网接口设计和实现需要经过以下步骤:1. 设计FPGA电路:使用Verilog或VHDL等硬件描述语言实现电路设计和仿真。

2. 选取以太网MAC:选择适合特定应用场景的以太网MAC,例如10G、25G、40G等。

3. 实现FPGA电路:在FPGA开发板中实现电路设计,FPGA的GPIO口可以与物理层器件、MAC等进行连接,形成完整的以太网接口。

4. 调试和测试:通过网络测试,验证以太网接口的工作状态和性能指标是否达标。

FPGA的以太网接口可以应用于许多领域,例如数据中心、高性能计算、视频监控等,提供高速、可靠的连接。

随着云计算和物联网的迅猛发展,基于FPGA的高速以太网接口设计将变得越来越重要,这将在未来的发展中起到至关重要的作用。

基于FPGA的高速以太网接口设计和实现2以太网是一种最常见的局域网(LAN)技术,它通过使用协议和设备实现计算机和其他设备之间的数据通信。