倍频电路与分频电路的设计

- 格式:docx

- 大小:47.11 KB

- 文档页数:6

倍频电路课程设计报告一、教学目标本课程旨在让学生了解和掌握倍频电路的基本原理和应用,通过学习,学生应能:1.理解倍频电路的定义、功能和工作原理。

2.掌握倍频电路的主要组成部分,以及各部分的作用和相互关系。

3.学会分析倍频电路的性能指标,如频率、幅度等。

4.能够运用倍频电路解决实际问题,提高学生的实践能力。

二、教学内容本课程的教学内容主要包括:1.倍频电路的基本概念:介绍倍频电路的定义、功能和工作原理。

2.倍频电路的组成:详细讲解倍频电路的各个组成部分,包括晶体管、电容、电阻等。

3.倍频电路的分析:教授如何分析倍频电路的性能指标,如频率、幅度等。

4.倍频电路的应用:介绍倍频电路在实际中的应用案例,让学生学会运用。

三、教学方法为了提高教学效果,本课程将采用多种教学方法,包括:1.讲授法:讲解倍频电路的基本概念、原理和应用。

2.讨论法:学生进行小组讨论,分享对倍频电路的理解和看法。

3.案例分析法:分析实际中的倍频电路应用案例,让学生更好地理解倍频电路。

4.实验法:安排实验室实践,让学生亲手操作,加深对倍频电路的理解。

四、教学资源为了支持教学,我们将准备以下教学资源:1.教材:选择合适的教材,为学生提供系统的学习资料。

2.参考书:提供相关的参考书籍,丰富学生的知识储备。

3.多媒体资料:制作课件、视频等多媒体资料,提高教学的趣味性和生动性。

4.实验设备:准备充足的实验设备,确保每个学生都有机会动手实践。

五、教学评估本课程的评估方式包括以下几个方面:1.平时表现:通过课堂参与、提问、小组讨论等,评估学生的学习态度和积极性。

2.作业:布置适量的作业,评估学生对倍频电路知识的理解和应用能力。

3.考试:安排期末考试,全面测试学生对倍频电路的掌握程度。

评估方式应客观、公正,能够全面反映学生的学习成果。

我们将根据学生的表现,给予及时的反馈,帮助学生提高。

六、教学安排本课程的教学安排如下:1.教学进度:按照教材的章节安排,有序地进行教学。

FPGA分频与倍频的简单总结(涉及⾃⼰设计,调⽤时钟IP核,调⽤MMCM原语模块)原理介绍1、分频FPGA设计中时钟分频是重要的基础知识,对于分频通常是利⽤计数器来实现想要的时钟频率,由此可知分频后的频率周期更⼤。

⼀般⽽⾔实现偶数系数的分频在程序设计上较为容易,⽽奇数分频则相对复杂⼀些,⼩数分频则更难⼀些。

1)偶分频系数=时钟输⼊频率/时钟输出频率=50MHz/5MHz=10,则计数器在输⼊时钟的上升沿或者下降沿从0~(10-1)计数,⽽输出时钟在计数到4和9时翻转。

2)奇分频系数=50MHz/10MHz=5,则两个计数器分别在输⼊时钟的上升沿和下降沿从0~ (5-1)计数,⽽相应的上升沿和下降沿触发的输出时钟在计数到1和4时翻转,最后将两个输出时钟进⾏或运算从⽽得到占空⽐为50%的5分频输出时钟。

下图所⽰为50MHz输⼊时钟进⾏10分频和5分频的仿真波形2、倍频两种思路:PLL(锁相环)或者利⽤门延时来搭建注意:此仿真是利⽤FPGA内部电路延迟来实现的倍频需要在后仿真下才能看到波形,在⾏为仿真下⽆法得到输出波形。

⼀、时钟IP的分频倍频相关参数说明输⼊时钟:clk_in1(125MHz)输出时钟:clk_out1(50MHz),clk_out2(74.25MHz)则VCO Freq=1262.5MHz=clk_in1*CLKFBOUT_MULT_F/DIVCLK_DIVIDE=125*50.5/5clk_out1(50MHz)=VCO_Freq/Divide=1265.5/25.250clk_out2(74.25MHz)=VCO_Freq/Divide=1265.5/17⼆、MMCME4_ADVMMCME4是⼀种混合信号块,⽤于⽀持频率合成、时钟⽹络设计和减少抖动。

基于相同的VCO频率,时钟输出可以有单独的分频、相移和占空⽐。

此外,MMCME4还⽀持动态移相和分数除法(1)Verilog 初始化模板MMCME4_ADV #(.BANDWIDTH("OPTIMIZED"), // Jitter programming.CLKFBOUT_MULT_F(5.0), // Multiply value for all CLKOUT.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB.CLKFBOUT_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKIN1_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN2_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKOUT0_DIVIDE_F(1.0), // Divide amount for CLKOUT0.CLKOUT0_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT0.CLKOUT0_PHASE(0.0), // Phase offset for CLKOUT0.CLKOUT0_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT1_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT1_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT1_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT1_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT2_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT2_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT2_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT2_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT3_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT3_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT3_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT3_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT4_CASCADE("FALSE"), // Divide amount for CLKOUT (1-128).CLKOUT4_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT4_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT4_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT4_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT5_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT5_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT5_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT5_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT6_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT6_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT6_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT6_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).COMPENSATION("AUTO"), // Clock input compensation.DIVCLK_DIVIDE(1), // Master division value.IS_CLKFBIN_INVERTED(1'b0), // Optional inversion for CLKFBIN.IS_CLKIN1_INVERTED(1'b0), // Optional inversion for CLKIN1.IS_CLKIN2_INVERTED(1'b0), // Optional inversion for CLKIN2.IS_CLKINSEL_INVERTED(1'b0), // Optional inversion for CLKINSEL.IS_PSEN_INVERTED(1'b0), // Optional inversion for PSEN.IS_PSINCDEC_INVERTED(1'b0), // Optional inversion for PSINCDEC.IS_PWRDWN_INVERTED(1'b0), // Optional inversion for PWRDWN.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REF_JITTER1(0.0), // Reference input jitter in UI (0.000-0.999)..REF_JITTER2(0.0), // Reference input jitter in UI (0.000-0.999)..SS_EN("FALSE"), // Enables spread spectrum.SS_MODE("CENTER_HIGH"), // Spread spectrum frequency deviation and the spread type .SS_MOD_PERIOD(10000), // Spread spectrum modulation period (ns).STARTUP_WAIT("FALSE") // Delays DONE until MMCM is locked)MMCME4_ADV_inst (.CDDCDONE(CDDCDONE), // 1-bit output: Clock dynamic divide done.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock.CLKFBOUTB(CLKFBOUTB), // 1-bit output: Inverted CLKFBOUT.CLKFBSTOPPED(CLKFBSTOPPED), // 1-bit output: Feedback clock stopped.CLKINSTOPPED(CLKINSTOPPED), // 1-bit output: Input clock stopped.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0.CLKOUT0B(CLKOUT0B), // 1-bit output: Inverted CLKOUT0.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1.CLKOUT1B(CLKOUT1B), // 1-bit output: Inverted CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2.CLKOUT2B(CLKOUT2B), // 1-bit output: Inverted CLKOUT2.CLKOUT3(CLKOUT3), // 1-bit output: CLKOUT3.CLKOUT3B(CLKOUT3B), // 1-bit output: Inverted CLKOUT3.CLKOUT4(CLKOUT4), // 1-bit output: CLKOUT4.CLKOUT5(CLKOUT5), // 1-bit output: CLKOUT5.CLKOUT6(CLKOUT6), // 1-bit output: CLKOUT6.DO(DO), // 16-bit output: DRP data output.DRDY(DRDY), // 1-bit output: DRP ready.LOCKED(LOCKED), // 1-bit output: LOCK.PSDONE(PSDONE), // 1-bit output: Phase shift done.CDDCREQ(CDDCREQ), // 1-bit input: Request to dynamic divide clock.CLKFBIN(CLKFBIN), // 1-bit input: Feedback clock.CLKIN1(CLKIN1), // 1-bit input: Primary clock.CLKIN2(CLKIN2), // 1-bit input: Secondary clock.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.DADDR(DADDR), // 7-bit input: DRP address.DCLK(DCLK), // 1-bit input: DRP clock.DEN(DEN), // 1-bit input: DRP enable.DI(DI), // 16-bit input: DRP data input.DWE(DWE), // 1-bit input: DRP write enable.PSCLK(PSCLK), // 1-bit input: Phase shift clock.PSEN(PSEN), // 1-bit input: Phase shift enable.PSINCDEC(PSINCDEC), // 1-bit input: Phase shift increment/decrement.PWRDWN(PWRDWN), // 1-bit input: Power-down.RST(RST) // 1-bit input: Reset);(2)本实验仿真所⽤参数配置说明及部分端⼝调⽤1、参数配置说明本实验通过输⼊时钟CLKIN1(150MHz),实现输出反馈时钟CLKFBOUT(150MHz)、输出时钟CLKOUT0(74.25MHz)、输出时钟CLKOUT1(74.25MHz)、输出时钟CLKOUT2(59.4MHz)、输出时钟CLKOUT3(49.5MHz)。

倍频电路设计范文倍频电路是一种通过倍频器将信号频率倍增的电路。

在许多应用中,需要将信号频率倍增,比如在通信领域中将低频信号转换为高频信号,以增加传输距离和可靠性。

倍频电路设计需要根据具体的应用需求和信号特性,选择合适的倍频器电路和参数。

常用的倍频器电路有倍频整波电路、倍频整数倍电路和倍频锁相环电路。

倍频整波电路通过整流和滤波将信号频率倍增,适用于低功率小幅度信号的倍频。

倍频整数倍电路则是通过电路中的倍频元件(如倍频器二极管、倍频晶体管)将信号频率乘以整数倍。

倍频锁相环电路则是通过锁定一个参考频率,并通过控制多级倍频器的相位和频率来实现信号频率倍增。

在设计倍频电路时,首先要确定输入信号的频率范围、幅度和功率。

然后选择合适的倍频器电路和倍频器元件。

对于倍频整波电路,可以选择使用整流电路和滤波电路,如谐振电路和低通滤波器。

对于倍频整数倍电路,可以选择使用适合的倍频器元件,如倍频晶体管、倍频二极管等。

对于倍频锁相环电路,需要选择合适的相位比较器、VCO(压控振荡器)和分频器等。

在设计倍频电路时,还需要考虑电路的带宽、失真、稳定性和功耗等方面的问题。

带宽要求决定了电路的频率响应范围,失真要求决定了电路的非线性和波形失真程度,稳定性要求决定了电路的抗干扰能力和稳定性,功耗要求决定了电路的能效。

总之,倍频电路设计需要根据具体应用需求和信号特性,选择合适的倍频器电路和元件,考虑电路的带宽、失真、稳定性和功耗等方面的问题,并可以使用仿真软件进行模拟和分析。

这样可以设计出满足要求的倍频电路,提高信号处理和传输的效果。

「一种简单而实用电子分频音频放大电路设计」电子分频是一种常见的音频处理技术,用于将输入信号分成不同的频段,并对每个频段进行放大。

设计一种简单而实用的电子分频音频放大电路可以有效地实现音频信号的处理和增强。

下面将详细介绍这个电路的设计。

首先,我们需要明确电子分频的基本原理。

电子分频通过使用不同的滤波器将输入信号分成不同的频段,然后将每个频段的信号分别放大。

常用的滤波器有低通滤波器、高通滤波器和带通滤波器。

为了实现简单和实用,我们选择使用一种普遍的设计方法-派生式架构。

在派生式架构中,输入信号首先经过一个低通滤波器,将高频信号滤除,只保留低频信号。

然后,低频信号分别通过一个放大器进行放大。

接下来,我们通过选择合适的电容和电感来设计低通滤波器和放大器的参数。

一般来说,电容和电感的选择取决于所需的频率范围和放大倍数。

为了更好地说明这个设计,我们以一个实例进行讲解。

假设我们想设计一个电子分频音频放大电路,将输入信号分成两个频段-低频和高频,并分别放大。

我们希望低频段能够通过放大器增强10倍,高频段能够通过放大器增强5倍。

首先,我们需要选择一个适当的低通滤波器。

根据所需的低频范围和其它设计参数,我们可以选择一个电容值为0.1μF的电容和一个电感值为10mH的电感构成的RC低通滤波器。

这个低通滤波器将输入信号中高于50Hz的频率滤除。

接下来,我们需要选择一个适当的放大器来放大低频信号。

我们可以选择一个放大倍数为10的运算放大器。

将低频信号的输出连接到运算放大器的非反向输入端,并将反馈电阻连接到运算放大器的输出端和反向输入端,以实现放大。

同样地,我们需要选择一个适当的高通滤波器来滤除低频信号,只保留高频信号。

我们可以选择一个电容值为0.01μF的电容和一个电感值为1mH的电感构成的RC高通滤波器。

这个高通滤波器将输入信号中低于500Hz的频率滤除。

最后,我们需要选择一个适当的放大器来放大高频信号。

我们可以选择一个放大倍数为5的运算放大器。

倍频实现原理

倍频实现原理是指在电子设备中通过对时钟信号进行倍频操作,实现对处理器等器件工作频率的提高的技术。

其实现原理主要包括以下几个方面:

1. 时钟信号的生成:时钟信号是在主板上由晶振等元器件产生的,其频率一般为几十兆赫至几百兆赫。

时钟信号是整个电子设备各个器件同步工作的基础。

2. 倍频电路的设计:倍频电路一般由锁相环、分频器、乘法器等元器件组成。

其功能是将输入的时钟信号进行倍频操作,从而实现对器件工作频率的提高。

3. 倍频倍数的设置:倍频操作的倍数决定了器件的工作频率,一般可以通过BIOS设置或者调节主板上的倍频开关来实现。

不同型号的器件支持的最大倍频数不同,需要根据具体情况进行设置。

4. 倍频时的稳定性:由于倍频操作会带来较高的工作频率,容易引起电子设备的稳定性问题。

针对这个问题,需要在倍频电路的设计和器件的选择上进行优化,同时还需要合理设置风扇和散热器等冷却系统,以保证电子设备的稳定运行。

通过以上几个方面的设计和优化,倍频实现原理可以使电子设备在不增加成本的情况下实现对器件工作频率的提高,从而提高设备的性能和响应速度。

- 1 -。

"分频"是说通过分频电路,将输入信号的频率进行降低后再输出.经过处理后,输出的信号频率如果是输入信号频率的1/2,叫2分频率;1/3,叫3分频;1/n,叫n分频;分频电路一般可以用数字电路来完成.2-4分频电路,可以用D或者JK触发器来实现.比如2分频原理就是让输入信号有两个脉冲时,输出端才出现一个脉冲,那么假如说输入信号为1000Hz,也就是输入信号每秒种有1000个脉冲,按照上面的原理,每2个输入脉冲才产生一个输出脉冲,那么输出信号就是500Hz,输出信号频率就变成了输入信号的1/2.如果要实现任意进制的分频,简单而且实用的电路是采用计数器电路.集成计数器芯片有74系列的74ls190、74ls191、74ls192等,以及40系列的CD4029等.实现n进制分频的原理是这样的:假如一个二进制计数器,如果计数到了5,那么4个输出端从高位到低位的状态是0101,按照8421码,这个输出就是5,我们可以将这4个输出端从高位到低位的第2、4个输出端的信号接到一个与门的输入端,按照与门的工作特性,只有当两个输入都为1时,输出才为1,而计数器计数到5时,也就是说计数的输入端信号有5个脉冲时,计数的输出端从高位到低位的第2、4个输出端的信号正好都为1,与门才输出1,除此之外的任何情况,与门的两个输入端都不可能同时为1,这就实现了5分频.与"分频"概念对应的还有"倍频".倍频就是使输出端信号频率为输入端信号频率的倍数,实现输出频率为输入频率2、3、4、n倍的电路,分别叫2倍频、3倍频、4倍频、n倍频电路.至于现实中电脑术语里提到的"分频"和"倍频",那是说的是CPU与总线、外设之间工作频率的关系.为什么会有分频、倍频这个说法,按照标准微机原理教科书的说法是,CPU的工作频率可以很高,但是有些外部设备如硬盘、软盘,按照现在技术手段,把他们的工作频率设计成到达CPU的工作频率是不可能的.也就是说,一般情况下,CPU的工作频率永远是高于外部设备的,为了协调CPU与外部设备的工作时序,就只有进行"分频"、"倍频"处理.__原先并没有倍频概念,CPU的主频和系统总线的速度是一样的,但CPU的速度越来越快,倍频技术也就应允而生。

倍频器电路设计

倍频器电路设计需要考虑以下几个方面:

1.输入频率和倍频系数:倍频器电路的输入频率和倍频系数是设计的基础,需要根据实际需求来确定。

2.电路结构:倍频器电路可以采用不同的结构,如RC 振荡器、LC振荡器、石英晶体振荡器等。

不同的结构具有不同的特点,需要根据实际需求来选择。

3.滤波器设计:倍频器电路中的滤波器用于滤除不需要的谐波和噪声,保证输出信号的纯净度。

需要根据实际需求来设计滤波器的类型和参数。

4.放大器设计:倍频器电路中的放大器用于放大输出信号,提高信号的幅度和功率。

需要根据实际需求来设计放大器的类型和参数。

5.相位检测和调整:倍频器电路中的相位检测和调整用于保证输出信号的相位与输入信号保持一致。

需要根据实际需求来设计相位检测和调整电路。

在具体设计过程中,可以采用以下步骤:

1.确定输入频率和倍频系数,选择合适的电路结构。

2.设计滤波器,滤除不需要的谐波和噪声。

3.设计放大器,放大输出信号的幅度和功率。

4.设计相位检测和调整电路,保证输出信号的相位与输入信号保持一致。

5.整体调试,检查各部分的工作状态,确保电路的稳定性和可靠性。

要注意的是,倍频器电路设计涉及到多个领域的知识,需要综合考虑各种因素,包括电路原理、电子元件、电路板设计等。

因此,在进行倍频器电路设计时,需要具备扎实的电子技术基础和丰富的实践经验。

倍频器电路设计-回复什么是倍频器电路设计?倍频器电路设计是一种用于将输入信号频率倍增的电路。

它可以通过改变输入信号频率的周期来实现输出信号的频率加倍。

在现代电子设备中,倍频器电路被广泛应用于通信、雷达、医疗设备和其他高频应用领域。

实现倍频器电路的一种常见方法是使用锁相环(PLL)技术。

锁相环是一种反馈系统,通过比较输入信号与输出信号的频率相位差,并利用反馈调整输出信号频率,从而实现倍频效果。

锁相环电路由相位检测器、低通滤波器、电压控制振荡器和分频器等组成。

下面我们将一步一步介绍如何设计一个简单的倍频器电路。

第一步,选择合适的锁相环芯片。

在倍频器电路设计中,选择合适的锁相环芯片非常关键。

通常,我们需要考虑的因素包括工作频率范围、相位检测灵敏度、锁定时间和功耗等。

根据具体需求,选择适合的芯片型号。

第二步,确定输入和输出频率。

根据应用要求,确定输入信号和输出信号的频率范围。

例如,如果输入信号频率为100MHz,我们希望输出信号频率为倍增后的200MHz,那么我们需要设计一个2倍频的电路。

第三步,设计相位检测器。

相位检测器用于检测输入信号和输出信号的相位差,并将其转换为电压信号。

在设计相位检测器时,我们可以选择常见的相位频率检测器(PFD),根据芯片手册提供的电路设计指南,确定合适的元器件参数和连接方式。

第四步,设计低通滤波器。

低通滤波器用于滤除相位检测器输出中的高频杂波和噪声,得到稳定的控制电压。

在设计低通滤波器时,我们需要根据频率要求选择合适的电阻和电容值,以及滤波器的截止频率。

第五步,设计电压控制振荡器。

电压控制振荡器(VCO)根据输入的控制电压调整输出信号的频率。

在设计电压控制振荡器时,我们需要选择适当的电感、电容和电阻等元件,并根据芯片手册提供的设计指南确定合适的参数。

第六步,设计分频器。

分频器用于将VCO输出的高频信号进行分频,从而得到期望的倍频输出。

在设计分频器时,我们需要根据倍频系数确定适当的分频比,并选择合适的计数器电路或专用分频器芯片。

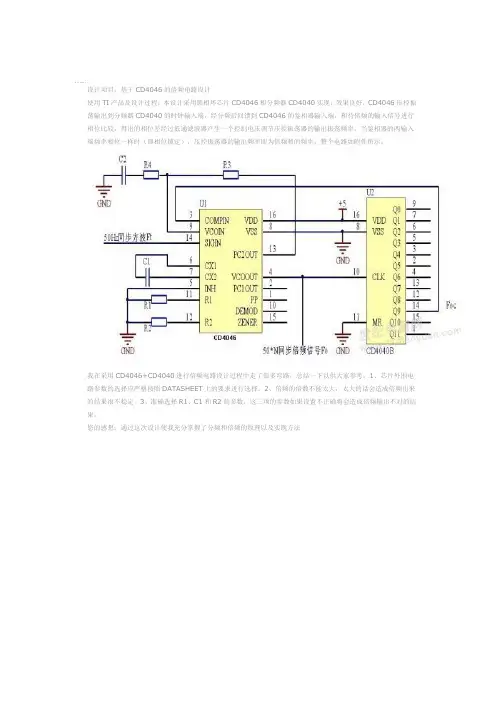

设计项目:基于CD4046的倍频电路设计

使用TI产品及设计过程:本设计采用锁相环芯片CD4046和分频器CD4040实现,效果良好,CD4046压控振荡输出到分频器CD4040的时钟输入端,经分频后回馈到CD4046的鉴相器输入端,和待倍频的输入信号进行相位比较,得出的相位差经过低通滤波器产生一个控制电压调节压控振荡器的输出振荡频率,当鉴相器的两输入端频率相位一样时(即相位锁定),压控振荡器的输出频率即为倍频和的频率。

整个电路如附件所示。

我在采用CD4046+CD4040进行倍频电路设计过程中走了很多弯路,总结一下以供大家参考:1、芯片外围电路参数的选择应严格按照DATASHEET上的要求进行选择。

2、倍频的倍数不能太大,太大的话会造成倍频出来的结果很不稳定。

3、准确选择R1、C1和R2的参数,这三项的参数如果设置不正确将会造成倍频输出不对的结果。

您的感想:通过这次设计使我充分掌握了分频和倍频的原理以及实现方法。

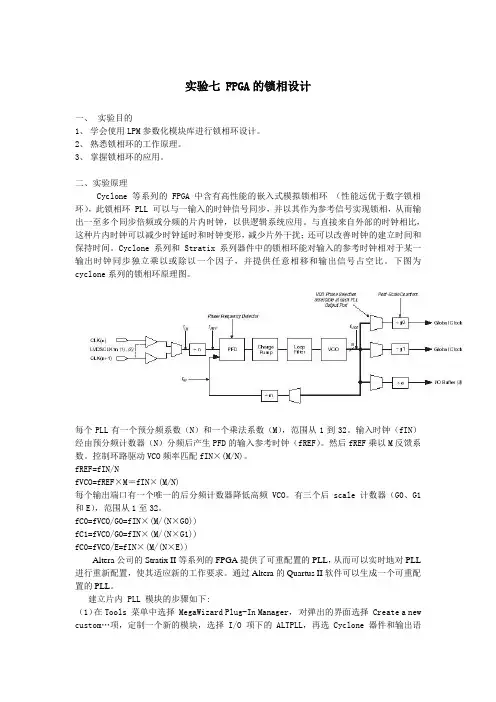

实验七 FPGA的锁相设计一、实验目的1、学会使用LPM参数化模块库进行锁相环设计。

2、熟悉锁相环的工作原理。

3、掌握锁相环的应用。

二、实验原理Cyclone 等系列的 FPGA中含有高性能的嵌入式模拟锁相环(性能远优于数字锁相环),此锁相环 PLL 可以与一输入的时钟信号同步,并以其作为参考信号实现锁相,从而输出一至多个同步倍频或分频的片内时钟,以供逻辑系统应用。

与直接来自外部的时钟相比,这种片内时钟可以减少时钟延时和时钟变形,减少片外干扰;还可以改善时钟的建立时间和保持时间。

Cyclone 系列和 Stratix 系列器件中的锁相环能对输入的参考时钟相对于某一输出时钟同步独立乘以或除以一个因子,并提供任意相移和输出信号占空比。

下图为cyclone系列的锁相环原理图。

每个PLL有一个预分频系数(N)和一个乘法系数(M),范围从1到32。

输入时钟(fIN)经由预分频计数器(N)分频后产生PFD的输入参考时钟(fREF)。

然后fREF乘以M反馈系数。

控制环路驱动VCO频率匹配fIN×(M/N)。

fREF=fIN/NfVCO=fREF×M=fIN×(M/N)每个输出端口有一个唯一的后分频计数器降低高频VCO。

有三个后scale计数器(G0、G1和E),范围从1至32。

fC0=fVCO/G0=fIN×(M/(N×G0))fC1=fVCO/G0=fIN×(M/(N×G1))fC0=fVCO/E=fIN×(M/(N×E))Altera公司的Stratix II等系列的FPGA提供了可重配置的PLL,从而可以实时地对PLL 进行重新配置,使其适应新的工作要求。

通过Altera的Quartus II软件可以生成一个可重配置的PLL。

建立片内 PLL 模块的步骤如下:(1)在Tools 菜单中选择 MegaWizard Plug-In Manager,对弹出的界面选择 Create a new custom…项,定制一个新的模块,选择 I/O 项下的 ALTPLL,再选 Cyclone 器件和输出语言方式,最后输入设计文件存放的路径和文件名,如d:\sin_gnt\PLL3.vhd。

电路中的频率倍增与分频方法电路中的频率倍增与分频方法是电子技术领域中常用的两种方法,用于改变信号的频率。

本文将介绍频率倍增与分频的原理和常见的应用场景。

一、频率倍增的原理与方法频率倍增是指将输入信号的频率增加到倍数的方法。

在电子领域中,常用的频率倍增方法有谐振倍频法、倍频器以及锁相环等。

1. 谐振倍频法谐振倍频法利用谐振现象实现频率倍增。

当输入信号的频率和谐振电路的固有频率相同时,电路会发生共振现象,使得输出信号的频率是输入信号的倍数。

谐振倍频法的优点是简单可靠,适用于低频和中频信号的倍频。

2. 倍频器倍频器是一种电子器件,用于将输入信号的频率倍增。

常见的倍频器有整流倍频器和非线性倍频器。

整流倍频器利用非线性元件的特性,将输入信号的谐波倍增;非线性倍频器则通过非线性元件和滤波电路的组合,将输入信号的频率倍增。

3. 锁相环锁相环是一种反馈系统,可以将输入信号的频率倍增或者分频。

锁相环由相位检测器、低通滤波器、电压控制振荡器和除频器组成。

相位检测器用于比较输入信号和振荡器产生的信号之间的相位差,通过调整振荡器的频率,实现输入信号频率的倍增或分频。

二、频率分频的原理与方法频率分频是指将输入信号的频率降低到分数的方法。

常用的频率分频方法有计数器分频、分频器以及相位锁定环等。

1. 计数器分频计数器分频是一种简单直接的分频方法。

计数器通过计数输入的脉冲数量,当计数器计数到特定值时,输出一个脉冲信号,从而实现对输入信号的分频。

计数器分频器常用于数字时钟、频率计等应用中。

2. 分频器分频器是一种电子器件,通过设置分频系数,将输入信号的频率分频。

常见的分频器有二分频器、四分频器等。

分频器可以通过级联连接实现更高的分频比。

分频器广泛应用于通信系统、频率合成器等领域。

3. 相位锁定环相位锁定环是一种基于反馈的频率分频方法。

它通过不断调整振荡器的相位,使得输入信号与振荡器的相位保持恒定的差值,从而实现对输入信号频率的分频。

课程设计说明书课程名称:模拟电子技术课程设计题目:倍频电路与分频电路的设计学生姓名:专业:班级:学号:指导教师:日期:年月日一、设计任务与要求1. 设计一倍频电路,能完成2倍频、4倍频甚至更多功能;且这些倍频能可用通过拨动开关转换;振荡电路自行设计、制作,振荡频率应不低于11MHZ晶振来完成;2. 设计一分频电路,能完成1/2分频、1/4分频甚至更低功能;且这些分频能通过拨动开关转换;振荡电路自行设计、制作,振荡频率应不低于11MHZ可用晶振来完成;二、方案设计与论证随着通信技术的日益发展,倍频技术应用的领域也日益增长;例如CPU的倍频,最初CPU的速度与系统总线的速度是一样的,但随着CPU的速度要求越高,相应的倍频技术也就得到了迅速的发展;其工作原理是使系统总线工作在低频状态,而CPU的运行速度可以通过倍频技术来提升;改变频率的方法有很多种,本文只讨论几种:傅里叶法,锁相环法及乘法器与滤波器法;方案一、傅里叶法:这是一种最简单的变频方式,它采用了傅里叶级数;任何一个周期信号都能表示为其基波和其谐波的和,如果将变换振荡电路输出的正弦波为方波,那它可以用一下的公式表示:接着就需要选择正确的谐波,接着可以通过一个带通滤波器来选择所需的谐波;缺陷:自适用于低频;方案二、锁相环法:在这个方法中,其输出频率不是直接是基准频率的输出,而是通过一个电压控制的振荡电路输出,它是通过一个相位比较器和基准电路频率同步;要被比较的频率是要除以倍频因子;由于频率的分割,压控振荡电路必须产生一个乘以n的频率;此过程便实现了频率的改变;局限:在大的频率范围内容易实现,起抖动差;方案三、乘法器和滤波器法:此方法是,首先建立一个振荡电路,使其产生正弦波,而后通过一个乘法器,使其实现倍频,再通过一个滤波器,选择我们需要的频率,从而实现倍频;分频是通过JK触发器实现,其原理是利用JK触发器的保持及翻转功能,实现分频,再通过一个滤波整流电路,得到所需的基波;其大致框图如下图1:图1三、单元电路设计与参数计算1、 LC三点式正弦波振荡电路原理图如下图2所示,其中包括输入滤波电路和输出滤波电路,消除噪音信号;其产生的正弦波频率主要与C1、C6和L3相关;计算公式如下:图22、倍频实现电路如下图3所示,其中包括乘法电路和选频滤波电路,分别实现二倍频和四倍频;用乘法器实现倍频原理:有公式如22cos1sin2wxwx-=)(,通公式可知,乘法器可实现倍频功能,同时也带来直流分量;所以,在其后有整流选频滤波电路,实现去高频和直流分量功能;而选频的计算公式如下:图33、分频电路如图4所示,其中包括JK触发器,和选频整流滤波电路;JK触发器是实现分频,其原理是利用JK触发器的保持和翻转功能实现分频,产生方波;然后通过选频滤波电路实现选频和滤波,去除方波中的高频谐波部分和直流分量,保持基波,使其产生正弦波;其计算公式如下:图4四、总原理图及元器件清单1.总原理图2.元件清单型号参数名称五、安装与调试1、在LC 三点式正弦波振荡电路中,只需讨论其输出频率相关的元器件参数,我们需要其输出的是大于12MHz 的频率,由图2可知,影响其输出频率的元器件是C1,C6和L3,其输出频率计算公式如下:代人参数算出结果为f=13.2MHz,而经过调试结果表明,其结果是正确的,结果如图5所示:图5图6 图7 2、在倍频放大电路中,其中乘法器和选频整流滤波电路可实现二倍频和四倍频,乘法器实现频率的放大,而滤波电路实现去除直流和高频分量;其所用到的公式如下:22cos 1sin 2wx wx -=)( , LCf π21= 其二倍频的组成元件为C8=1pf 和L6=34uH,四倍频的组成元件为C9=1pf 和L7=8.54uH,代人公式分别得f2=26.4MHz,f4=52.8MHz;测试结果如图6、7所示;3、在分频电路中,其由JK 触发器及选频整流滤波电路组成,如图4所示;JK 触发器利用其保持及翻转特性,把正弦波转换成方波并实现分频,然后经过选频滤波电路转换为二分频和四分频的正弦波;所用到的公式如下:选频整流滤波电路的二分频和四分频电路分别由C10=1pf和L4=0.54uH、及C11=1pf和L5=2.16uH组成,其分别代入公式得f’2=6.5MHz,f’4=3.2MHz;测试结果如图8、9所示;图8 图9六、性能测试与分析1、LC三点式正弦波振荡电路此振荡电路可实现5-30MHz范围的频率,可以通过改变C6来控制;刚开始时,输入的直流电源和输出的正弦波没有经过滤波而得到的正弦波是很不稳定,后来经过查阅资料及与同学讨论,我才发现输入的直流电源也是有噪音波的,但后来发现在输入直流电源加了滤波后还是效果不大,最后在输出的正弦波也加滤波后,图形才稳定下来;如图10所示;2、二、四倍频电路如图3所示,初始时并不了解要在乘法器后加选频整流滤波电路,就直接输出了;不过图形是不进人意,因为在正弦波相乘后会有直流分量和一些高频谐波;后来在其后加了滤波电路,效果便出来了,如图10所示;3、二、四倍频电路如图4所示,开始时我也没有加选频整流滤波电路,输出的是能实现分频的方波,后来经过了解到方波含有基波及许多高频谐波和直流分量,这是傅里叶的知识;然后我设计了选频整流滤波电路,使其只输出基波;如图11所示;图10 图11七、结论与心得1、结论:本次课程设计,在完成倍频电路和分频电路的设计中,本文采用的乘法器和滤波整流电路实现了倍频功能,采用JK触发器和滤波整流电路实现了分频功能;实验表明,此方案是可行的;2、心得:通过为期两周的模电课程设计,我重新温习了一遍模电书,收益匪浅;俗话说得好啊,纸上得来终觉浅,要知此事须躬行;以前学习模拟电子技术这门课程,现在看来都是理论的知识,只是知道一个概念,只会考试做题,这便失去了学习模电知识的真正的作用;在刚开始做课程设计时,我面对着要选的题目一无所知,完全不知知道那个跟那个,对应的题目要用到哪些知识点来做都不知道,这时我才意识到平时只会考试的结果;这时我又想起了一句话:面对要学习的东西,如果你只是去看,那你只是能得到10%;如果你只是去听,那你能得到15%;而如果你去实践了,那你能得到80%;现在我才真正理解这话的意义;我们要学习,我们更要学而智用;在整个课程设计中,我几乎是与同学共同完成的,说得难听一点,是别人的结果,而我只是利用别人的结果来学习;说句实话,我的模电考试得九十多分分,而我去请教的那位同学远不如我的高,这是什么原因,我缺乏的是操作能力实践能力;有时候我们学习的知识只会想到期末考试能过就行,或是要拿奖学金;我想着并不是我们真正要的;我们要的是一种操作能力、创新能力;随着社会的发展,高学历的所谓人才越来越多,而真正有实力的、能做事的,又有多少呢反而,失业率也变得越来越高,这是社会对我们的要求提高了吗当然这是其中的一个,不过我想,更重要的是我们没有真正的学会学习,考试考高分本人认为这并不代表你会学习,而真正会学习的是:你学到的东西要会用,能做出东西来;这是我做课程设计过程中的一些感触,也反映了本人在大学期间的一些只会考试的学习方法;知识是财富,关键是我们要如何用他去创造财富,如果只是把他用来考试,那就可伶了;就像以前,我对考试的题目也挺会做的,要我求什么参数啊放大倍数啊,感觉都很熟悉,就是从来没有想过它们的实际用处,可惜,太可惜了以上是本人在模电课程设计的一些心得体会,通过这次课程设计,我认识了很多自己的不足,同时也悟道了知识的博大精深和自己现在的目光短浅与渺小,这是我在这期间的最大体会和收获,因为一个人只能在认识自己的渺小才能有机会使自己进步;同时也认识自己的学习方法的不足,还要继续努力加油八、参考文献1、模拟电子技术2、数字电子技术3、百度。

倍频器电路设计倍频器是一种常见的电路,用于将一个输入信号的频率提高为原始频率的两倍或更多倍。

倍频器通常由非线性元件(例如二极管)和滤波器组成,用于增强原始信号的谐波成分。

本文将介绍倍频器电路的设计原理、常见的倍频器类型以及一些注意事项。

倍频器电路的设计原理主要基于非线性元件的特性。

在一个正常的非线性元件(例如二极管)中,电流和电压之间的关系不是直线的,而是曲线的。

这意味着,当输入信号的幅值增加时,输出信号的谐波成分也会增加。

首先,让我们来看一个简单的倍频器电路。

这个电路由一个二极管和一个滤波器组成。

输入信号通过二极管,然后通过滤波器。

滤波器的作用是去除非期望的频率成分,只留下所需的谐波成分。

在一个典型的倍频器电路中,输入信号的频率为f1,输出信号的频率为2f1。

当输入信号通过二极管时,非线性特性将产生许多谐波。

然后,滤波器会选择所需的谐波成分,将其放大并输出。

常见的倍频器类型包括倍频器链、倍频器阵列和锁相倍频器。

倍频器链是由多个倍频器级联而成的电路。

每个级别的倍频器将输入信号的频率提高一倍,并将其传递给下一个级别。

倍频器链的优点是可以实现较高的倍频比,但缺点是它对输入信号的频率精度要求较高。

倍频器阵列是由多个倍频器并联而成的电路。

每个倍频器都将输入信号的频率提高一倍,并将其输出到同一输出节点。

倍频器阵列的处理能力比较强,但它对输入信号的幅度和频率范围有一定的限制。

锁相倍频器是一种特殊的倍频器,它在输入信号和输出信号之间建立了一个反馈回路。

锁相倍频器能够精确地将输入信号的频率提高一倍,并输出到一个稳定的输出信号。

锁相倍频器通常由相位锁定环路和多级频率倍增器组成。

在设计倍频器电路时,我们需要注意一些关键问题。

首先,非线性元件的选择非常重要。

二极管是最常见的非线性元件之一,但还有其他的选择,如场效应管和三极管。

我们需要根据具体的需求选择合适的非线性元件并优化电路参数。

其次,滤波器的设计也很重要。

滤波器的作用是去除非期望的频率成分,只留下所需的谐波成分。

分频电路的设计 【2 】在数字电路的设计中,我们会经常碰到分频电路,并且分频电路输出旌旗灯号频率的稳固性.准确度与全部电路的稳固性有着很大的关系.本文就一些常用分频电路作一总结.一.n 2分频众所周知,2分频是最简略的分频,平日用D 触发器用作反相器即可以实现2分频,要想实现n 2分频,最简略的办法就是将2分频电路级联,n 级联在一路就组成了n 2分频.我们以n=5为例,用MAX+plus II 进行仿真,电路如图1所示,我们得到的波形如图2所示:图1图2由波形我们可以看出,该电路能实现32分频,但因为它采用的是行波时钟,Q4的输出与CL K 之间延时为5co t .n 越大,延时就越大.改良图1的电路,我们可以采用同步计数来实现32分频,如图2所示,个中5BITcounter 是在MAX+plus II 顶用生成的5位二进制加法计数器.Q4输出就是32分频的旌旗灯号,波形如图4所示.图3图4因为图3是采用同步计数器,所以每个输出的延时都一样,都为co t .保证了体系的同步运行.同样的道理,若n 增大时,我们只要转变计数器的位数即可.二.2n 分频在数字电路的设计中,2n 分频也是经常碰到的.对于2n 分频,我们常采用两级分频的办法,第一级用来n 分频,第二级用作2分频,如许做的目标就是保证输出旌旗灯号有50%的占空比,若对占空比无请求则可随意率性实现n 分频. 以n=25为例,在MAX+plus II 中,应用结构一个5bit 模为25的加法计数器,电路如图5所示,out 即为50分频后的输出,波形如图6所示.图5图6从图6可以看出,out 与输入时钟CLK 之间的延时是2co t =6ns.三.M N2分频在一些特别的数字电路中,可能会用到M N 2分频,因为分频是小数,我们不可能对输入旌旗灯号准确地分频,只能保证输出旌旗灯号的平均频率与幻想的分一再率相等.我们这里以26/3分频为例来介绍这种分频办法.剖析:26/3分频的本质就是在26个CLK 周期内产生3个周期的输出旌旗灯号.我们照样采用采用两级分频办法,目标是为了保证占空比为50%,第一级分频倍数为13/3,即13个CLK 周期内产生3个周期的输出旌旗灯号.如许我们结构一个模13的4bit 加法计数器,应用门电路输出三个周期旌旗灯号,计数器从0计到3时A 输出1,计到7时B 输出1,计到12时C 输出1,将A.B.C 三路旌旗灯号相或就得到我们想要的波形,电路如图7所示,波形如图8所示.图7图8从波形上可以看出,输出out 的平均频率为准确的频率值,但具体到每个周期,它的同期与准确值之间有个小的误差,它的误差在一个输入时钟周期内.四.M n2分频在数字电路中,有时会碰到统一个电路能产生不同频率的波形,如谐波产生器.FSK 的调制等.此时输出频率和输入的频率之间的关系是:M f f nclkout 2M 是可变的,M 取不同的值对不同的输出频率.这里我们可以采用累加器的办法[1]来实现如许的分频电路.如图9所示.图9累加器的进位输出output 即为Mn 12-分频的频率,再经D 触发器便可得到我们想要的频率.这里的FREQUENCY CONTROL(n)为公式中的M,它是累加器的加数,经由过程D 触发器把每次累加的成果送到累加器,作为累加器的被加数.每个时钟周期内累加器加一个M,如许到进位有输出时刚好加了MOD (M n 12-)次,进位后如有余数则再送入累加器,用作下次累加,如许就保证了平均频率等于准确的频率.我们为以n=5为例来解释这个办法,电路如图10所示.图10 M=2时的输出波形,分频系数是32,如图11所示;图11 M=5时输出波形如图12所示;图12。

一种简单而实用电子分频音频放大电路设计设计一个简单而实用的电子分频和音频放大电路,可以按照以下步骤进行。

1.确定所需的输入和输出功率。

根据实际应用需求,确定所需的输入和输出功率,这将有助于选择合适的电子元件和电路设计参数。

2.选择适当的滤波器。

根据所需的分频和放大功能,选择适当的滤波器。

常见的滤波器类型包括低通滤波器(用于分频功能)和放大滤波器(用于音频放大功能)。

3.设计低通滤波器电路。

选择合适的电容和电感元件,设计一个低通滤波器电路,以实现所需的频率分频功能。

使用传统的RC电路设计方法,可以计算所需的电容和电感值。

4.设计放大器电路。

使用放大器电路来增强音频信号。

选择适当的放大器类型(如晶体管放大器、集成电路放大器等),并根据输出功率要求和输入电平来设计合适的放大器电路。

5.连接滤波器和放大器。

将低通滤波器和放大器电路连接在一起,以实现分频和放大的功能。

确保电路连接正确,并使用适当的元件(如耦合电容器)来进行信号传递。

6.测试和优化电路。

连接适当的输入源和负载,对电路进行测试和调优。

使用示波器和信号发生器等测试设备来检查电路的性能,并根据需要进行调整和优化。

7.验证电路的性能。

使用合适的音频信号源和扬声器来验证电路的分频和放大功能。

测试并记录电路的频率响应、失真和功率输出等参数,并与所需的规格进行比较。

8.优化和改进电路设计。

根据实际测试结果和反馈,对电路进行优化和改进。

可能需要调整滤波器参数、放大器电路配置或选择更适合的元件来改善电路的性能。

总结:设计一个简单而实用的电子分频和音频放大电路可以按照以上步骤进行。

关键是明确需求、选择合适的元件和电路,并进行测试和优化来确保电路的性能符合预期。

通过不断的优化和改进,可以实现一个满足需求的电子分频和音频放大电路设计。

D触发器实现二分频与二倍频先来二分频的

其基本思想是将D触发器改成T触发器,每隔一个时钟周期,输出时钟反向一次;这样就达到了二分频的目的;

下面列出Verilog代码:

module div2clk,rst_n,clk_out;

input clk,rst_n;

output clk_out;

wire clk_temp;

always posedge clk

begin

if~rst_n

begin

clk_out<=0;

end

else

clk_out<=clk_temp;

end

assign clk_temp=~clk_out;

endmodule

仿真图如下:

下面是二倍频的

基本思想:通过逻辑延时,使同频时钟相位改变,而后将两个时钟相或即可得到二倍频电路,不过占空比不可调,由两个时钟相位差决定;

Verilog代码如下:

module twice clk, clk_out;

input clk; output clk_out;

wire clk_temp;wire d_outn;reg d_out=0;

assign clk_temp = clk ^ d_out ;assign clk_out = clk_temp ;assign d_outn = ~d_out ;alwaysposedge clk _tempbegind_out <= d_outn ; endendmodule

由于它是靠延时产生的时钟,所以只能进行时序仿真才能看到波形,仿真波形如下:

大家可以自己在quartus下仿真。

单片机分频倍频

单片机分频和倍频是数字信号处理中的常见概念。

分频就是将单片机的时钟频率降低,而倍频则是将单片机的时钟频率提高。

在单片机中,通常有一个振荡器用于产生时钟信号,这个时钟信号是单片机执行各种操作的基础。

如果将这个时钟信号进行分频,就可以得到较低频率的时钟信号,从而降低单片机的运行速度。

例如,如果将时钟信号分频为原来的1/2,则单片机的运行速度也会降低为原来的1/2。

相反,倍频则是将单片机的时钟频率提高,从而加快单片机的运行速度。

例如,如果将时钟信号倍频为原来的2倍,则单片机的运行速度也会提高为原来的2倍。

在实际应用中,分频和倍频可以通过数字逻辑电路实现。

例如,通过使用计数器和触发器等数字逻辑元件,可以设计出具有分频或倍频功能的电路。

这些电路可以将输入的时钟信号进行处理,得到所需的输出时钟信号。

需要注意的是,分频和倍频可能会对单片机的性能产生影响。

如果单片机的运行速度过快或过慢,可能会导致系统不稳定或者无法正常工作。

因此,在使用分频和倍频时需要慎重考虑,并确保所选择的频率是合适的。

倍频电路与分频电路的

设计

文件编码(GHTU-UITID-GGBKT-POIU-WUUI-8968)

课程设计说明书

课程名称:模拟电子技术课程设计

题目:倍频电路与分频电路的设计

学生姓名:

专业:

班级:

学号:

指导教师:

日期:年月日

一、设计任务与要求

1.设计一倍频电路,能完成2倍频、4倍频(甚至更多)功能。

且这些倍频能通过拨

可用晶振来完成);动开关转换。

(振荡电路自行设计、制作,振荡频率应不低于11MH

Z

2.设计一分频电路,能完成1/2分频、1/4分频(甚至更低)功能。

且这些分频能通过拨

可用晶振来完成)。

动开关转换。

(振荡电路自行设计、制作,振荡频率应不低于11MH

Z

二、方案设计与论证

随着通信技术的日益发展,倍频技术应用的领域也日益增长。

例如CPU的倍频,最初CPU的速度与系统总线的速度是一样的,但随着CPU的速度要求越高,相应的倍频技术也就得到了迅速的发展。

其工作原理是使系统总线工作在低频状态,而CPU的运行速度可以通过倍频技术来提升。

改变频率的方法有很多种,本文只讨论几种:傅里叶法,锁相环法及乘法器与滤波器法。

方案一、傅里叶法:这是一种最简单的变频方式,它采用了傅里叶级数。

任何一个周期信号都能表示为其基波和其谐波的和,如果将变换振荡电路输出的正弦波为方波,那它可以用一下的公式表示:

接着就需要选择正确的谐波,接着可以通过一个带通滤波器来选择所需的谐波。

缺陷:自适用于低频。

方案二、锁相环法:在这个方法中,其输出频率不是直接是基准频率的输出,而是通过一个电压控制的振荡电路输出,它是通过一个相位比较器和基准电路频率同步。

要被比较的频率是要除以倍频因子。

由于频率的分割,压控振荡电路必须产生一个乘以n的频率。

此过程便实现了频率的改变。

局限:在大的频率范围内容易实现,起抖动差。

方案三、乘法器和滤波器法:此方法是,首先建立一个振荡电路,使其产生正弦波,而后通过一个乘法器,使其实现倍频,再通过一个滤波器,选择我们需要的频率,从而实现倍频。

分频是通过JK触发器实现,其原理是利用JK触发器的保持及翻转功能,实现分频,再通过一个滤波整流电路,得到所需的基波。

其大致框图如下图(1):

三、单元电路设计与参数计算

1、LC三点式正弦波振荡电路原理图如下图(2)所示,其中包括输入滤波电路和输出滤波电路,消除噪音信号。

其产生的正弦波频率主要与C1、C6和L3相关。

计算公式如下:

图(2)

2、倍频实现电路如下图(3)所示,其中包括乘法电路和选频滤波电路,分别实现二倍频和四倍频。

用乘法器实现倍频原理:有公式如

22

cos

1

sin2wx

wx

-=

)

(,通公式可知,乘法器可实现倍频功能,同时也带来直流分量。

所以,在其后有整流选频滤波电路,实现去高频和直流分量功能。

而选频的计算公式如下:

图(3)

3、分频电路如图(4)所示,其中包括JK触发器,和选频整流滤波电路。

JK触发器是实现分频,其原理是利用JK触发器的保持和翻转功能实现分频,产生方波。

然后通过选频滤波电路实现选频和滤波,去除方波中的高频谐波部分和直流分量,保持基波,使其产生正弦波。

其计算公式如下:

图(4)

四、总原理图及元器件清单

1.总原理图

2.元件清单

型号参数名称

五、安装与调试

1、在LC三点式正弦波振荡电路中,只需讨论其输出频率相关的元器件参数,我们需要其输出的是大于12MHz的频率,由图(2)可知,影响其输出频率的元器件是C1,C6和L3,其输出频率计算公式如下:

代人参数算出结果为f=13.2MHz,而经过调试结果表明,其结果是正确的,结果如图(5)所示:

图(5)图(6)图(7)

2、在倍频放大电路中,其中乘法器和选频整流滤波电路可实现二倍频和四倍频,乘法器实现频率的放大,而滤波电路实现去除直流和高频分量。

其所用到的公式如下:

22cos 1sin 2wx wx -=)(,LC

f π21= 其二倍频的组成元件为C8=1pf 和L6=34uH ,四倍频的组成元件为C9=1pf 和L7=8.54uH,代人公式分别得f2=26.4MHz,f4=52.8MHz 。

测试结果如图(6)、(7)所示。

3、在分频电路中,其由JK 触发器及选频整流滤波电路组成,如图(4)所示。

JK 触发器利用其保持及翻转特性,把正弦波转换成方波并实现分频,然后经过选频滤波电路转换为二分频和四分频的正弦波。

所用到的公式如下:

选频整流滤波电路的二分频和四分频电路分别由C10=1pf 和L4=0.54uH 、及C11=1pf 和L5=2.16uH 组成,其分别代入公式得f ’2=6.5MHz,f ’4=3.2MHz 。

测试结果如图(8)、

(9)所示。

图(8)图(9)

六、性能测试与分析

1、LC 三点式正弦波振荡电路

此振荡电路可实现5-30MHz 范围的频率,可以通过改变C6来控制。

刚开始时,输入的直流电源和输出的正弦波没有经过滤波而得到的正弦波是很不稳定,后来经过查阅资料及与同学讨论,我才发现输入的直流电源也是有噪音波的,但后来发现在输入直流电源加了滤波后还是效果不大,最后在输出的正弦波也加滤波后,图形才稳定下来。

如图(10)所示。

2、二、四倍频电路

如图(3)所示,初始时并不了解要在乘法器后加选频整流滤波电路,就直接输出了。

不过图形是不进人意,因为在正弦波相乘后会有直流分量和一些高频谐波。

后来在其后加了滤波电路,效果便出来了,如图(10)所示。

3、二、四倍频电路

如图(4)所示,开始时我也没有加选频整流滤波电路,输出的是能实现分频的方波,后来经过了解到方波含有基波及许多高频谐波和直流分量,这是傅里叶的知识。

然后我设计了选频整流滤波电路,使其只输出基波。

如图(11)所示。

图(10)图(11)

七、结论与心得

1、结论:

本次课程设计,在完成倍频电路和分频电路的设计中,本文采用的乘法器和滤波整流电路实现了倍频功能,采用JK触发器和滤波整流电路实现了分频功能。

实验表明,此方案是可行的。

2、心得:

这次实习可以说很困难,因为需要设计电路,而我对于模电一窍不通,所以,我面临巨大的考验,我接过别人设计的电路图,自己研究,虽然没有弄明白,但是也是一次不错的经历,以后会慢慢的珍惜这种课程活动,增加自己的思考和创作能力。

八、参考文献

1、模拟电子技术

2、数字电子技术

3、百度。