加法器设计--数字逻辑电路(电子科技大学)

- 格式:doc

- 大小:47.00 KB

- 文档页数:4

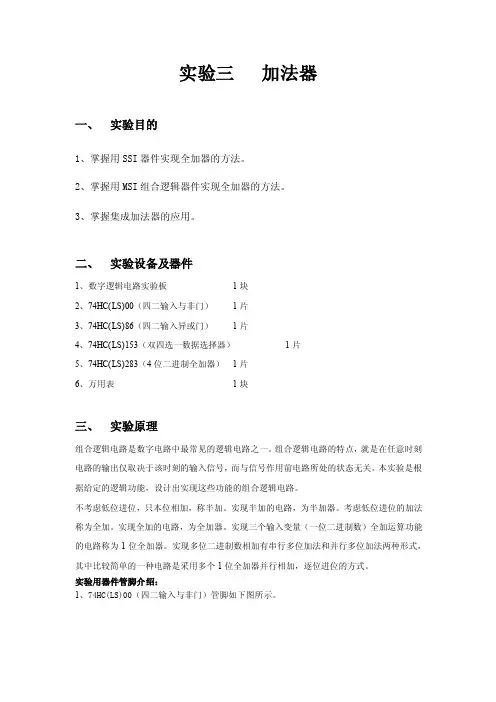

实验三加法器一、实验目的1、掌握用SSI器件实现全加器的方法。

2、掌握用MSI组合逻辑器件实现全加器的方法。

3、掌握集成加法器的应用。

二、实验设备及器件1、数字逻辑电路实验板1块2、74HC(LS)00(四二输入与非门)1片3、74HC(LS)86(四二输入异或门)1片4、74HC(LS)153(双四选一数据选择器)1片5、74HC(LS)283(4位二进制全加器)1片6、万用表1块三、实验原理组合逻辑电路是数字电路中最常见的逻辑电路之一。

组合逻辑电路的特点,就是在任意时刻电路的输出仅取决于该时刻的输入信号,而与信号作用前电路所处的状态无关。

本实验是根据给定的逻辑功能,设计出实现这些功能的组合逻辑电路。

不考虑低位进位,只本位相加,称半加。

实现半加的电路,为半加器。

考虑低位进位的加法称为全加。

实现全加的电路,为全加器。

实现三个输入变量(一位二进制数)全加运算功能的电路称为1位全加器。

实现多位二进制数相加有串行多位加法和并行多位加法两种形式,其中比较简单的一种电路是采用多个1位全加器并行相加,逐位进位的方式。

实验用器件管脚介绍:1、74HC(LS)00(四二输入与非门)管脚如下图所示。

2、74HC(LS)86(四二输入异或门)管脚如下图所示。

3、74HC(LS)153(双四选一数据选择器)管脚如下图所示。

4、74HC(LS)283(4位二进制全加器)管脚如下图所示。

四、 实验内容与步骤1、用门电路实现全加器(基本命题)参照表达式i i i i C B A S ⊕⊕=,i i i i i i B A C B A C +⊕=+)(1,其中i S 为本位和,i C 为低位向本位的进位,1+i C 为本位向高位进位,设计用与非门74HC(LS)00及异或门74HC(LS)86实现1位全加器的实验电路图,搭接电路,用LED 显示其输出,并记录结果在下表中。

1.1电路图1.2实验结果(基本命题)2、用数选器实现全加器输出Sn参照和实验内容与步骤1完全相同的逻辑功能,设计用与非门74HC(LS)00和数选器74HC(LS)153实现1位全加器输出S n的实验电路图,搭接电路,用LED显示其输出,观察电路的逻辑功能是否与设计功能一致。

电子科技大学UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA数字逻辑设计实验报告实验题目: 4bit模9加法器学生姓名:指导老师:一、实验内容设计一个4bit模9加法器。

输入为两个4bit的二进制数,输出为两数相加后模9的结果。

其数学表达式为:y=(x1+x2)mod 9。

二、实验要求1、功能性要求:能够实现4bit无符号数的模9加法运算,即输入两个4比特数据时能够正确输出其相加并模9运算结果。

2、算法要求:模加法器有多种算法,可采用任意算法进行设计。

3、设计性要求:采用全加器、半加器和基本门结构化描述。

能够编写Test Bench文件,并利用Modelsim进行仿真。

在Modelsim仿真正确的基础上,能够生成bit文件并上板验证其正确性。

4、基本上板要求:在上板实验时,输入的两个4bit数采用拨码开关输入,输出采用LED灯进行显示。

三、设计思路1、整体思路:为了实现4bit无符号数的模9加法运算,可以先将两个4bit的加数a和b 先分别模9,相加之后再模9得到最终结果。

2、模9器:先找出读入的5bit数与模9后的4bit数之间的关系,画出卡诺图,再根据卡诺图得出其相应的逻辑表达式即可。

设读入的5bit数为carry、a、b、c、d,模9后得到的4bit数为w、x、y、z。

则化简后得到的逻辑表达式分别为:w = carry’ab’c’d’,x= carry’bc + carry’a’b + carry’bd + carrya’b’c’d’,y = carry’a’c + carry’cd + carry’abc’d’ + carrya’b’c’d’,z= carry’a’d + carry’acd’ + carry’abd’ + carry a’b’c’d’。

3、全加器:全加器可以实现两个1bit数a、b和进位输入cin的相加,其真值表如下所示:这里全加器由半加器和或门构成,其原理图如下:4、半加器:半加器是全加器的基本组成单元,可以实现两个1bit数a和b的相加,并将进位输出,其真值表如下:半加器由一个异或门和一个与门构成,其原理图如下所示:5、数码管显示:单个数码管一共有7个端(不含小数点),用来表示组成一个数字的7个部分,故只要找到这7个段和模9后的4bit数间的对应关系,将其画出卡诺图并化简成逻辑表达式即可。

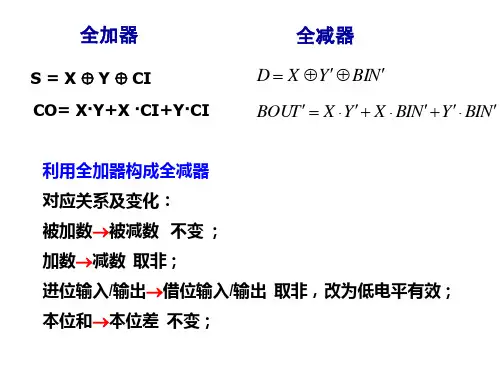

计算机专业类课程实验报告课程名称:数字逻辑实验学院:计算科学与工程专业:计算机科学与技术学生姓名:郭小明学号:2011060100010指导教师:蔡世民日期:2013年6月19日电子科技大学计算机学院实验中心电子科技大学实验报告实验一一、实验名称:基本门电路的功能和特性及组合逻辑电路实验二、实验学时:4三、实验内容和目的:目的:(1)基本门电掌握常用集成门电路的逻辑功能与特性(2)掌握各种门电路的逻辑符号(3)了解集成电路的外引线排列及其使用方法(4)学习组合逻辑电路的设计及测试方法内容:(1)部分TTL门电路逻辑功能验证(2)组合逻辑设计之全加器或全减器四、实验原理:1)组合逻辑电路的分析:对已给定的组合逻辑电路分析其逻辑功能。

步骤:(1)由给定的组合逻辑电路写函数式;(2)对函数式进行化简或变换;(3)根据最简式列真值表;(4)确认逻辑功能。

2).组合逻辑电路的设计:就是按照具体逻辑命题设计出最简单的组合电路。

步骤:(1)根据给定事件的因果关系列出真值表;(2)由真值表写函数式;(3)对函数式进行化简或变换;(4)画出逻辑图,并测试逻辑功能。

掌握了上述的分析方法和设计方法,即可对一般电路进行分析、设计,从而可以正确地使用被分析的电路以及设计出能满足逻辑功能和技术指标要求的电路。

五、实验器材(设备、元器件)•数字逻辑实验箱•双踪示波器(记录波形时,应注意输入、输出波形的时间相位关系,在座标中上下对齐。

)•集成电路:7400、7404、7432、7486六、实验步骤:1) 在实验箱上插入相应的门电路,并把输入端接实验箱的逻辑开关,输出端接发光二极管,接好电源正负极,即可进行逻辑特性验证实验。

将其逻辑特性制成表格。

2) 用7400连接的电路如图1.1所示,其中M端输入HZ级的连续脉冲,N端输入KHZ级的连续脉冲,X和Y接逻辑开关,在XY的四种输入组合下,用示波器观测A、B及F点的波形,并记录下来,写出F=f(M、N、X、Y)的逻辑表达式。

电子科技大学计算机学院标准实验报告(实验)课程名称数字逻辑综合实验xxx20160xxxxxxxxx电子科技大学教务处制表电子科技大学实验报告 1学生姓名:xxx 学号:指导教师:吉家成米源王华一、实验项目名称:中小规模组合逻辑设计二、实验目的:1.掌握非门、或门、与非门、异或门、数据选择器的逻辑功能。

2.掌握常有逻辑门电路的引脚排列及其使用方法。

3.采用中小规模逻辑门进行组合逻辑设计,掌握组合逻辑的设计方法。

三、实验内容:1.逻辑输入采用实验箱的K1-K11,逻辑输出接L1-L10。

测试实验箱上的HD74LS04P(非门)、SN74LS32N(或门)、SN74LS00N(与非门)、SN74HC86N(异或门)、SN74HC153(数据选择器、多路复用器)的逻辑功能。

2.采用小规模逻辑器件设计一位数据比较器:设一位数据比较器的输入为A、B,比较A>B,A=B,A<B,输出三个比较结果,输出采用低电平有效。

3.分别用小规模和中规模逻辑器件设计3输入多数表决器:设输入为A、B、C,当三个输入有两个或两个以上同意时,输出结果为同意,输入、输出的同意均为高电平有效。

四、实验原理:1.一块74LS04芯片上有6个非门。

非门的逻辑功能如表1所示,74LS04(非门、反相器)的逻辑符号和引脚排列如下图所示。

图1 74LS04的逻辑符号和引脚排列2.74LS32(或门)的逻辑符号、引脚排列如下图所示。

图2 74LS32的逻辑符号和引脚排列输入输出YA BL L LL H HH L HH H H3.74LS00输入输出YA BL L HL H HH L HH H L图3 74LS00逻辑符号和引脚排列4.一块74HC86芯片上有4个异或门。

异或门的逻辑功能如表4所示,74HC86(异或门)的逻辑符号、引脚排列如图4所示。

表4异或门的逻辑功能输入输出YA BL L LL H HH L HH H L图4 74HC86逻辑符号和引脚排列5.74HC153芯片上有两个4选1数据选择器。

《课程设计—加减法器》报告

电工17班王兴2011029170010

1.分析及设计方法:

要设计4位的全加全减器,首先要设计一位的全加器。

一位的全加器,需要3个输入,相加数A和B,还有进位输入Cin,2个输出,相加后的值S和进位输出Cout。

考虑到有一个控制端Addsub,所以要加一个输入。

然后考虑加法器转换为减法器。

转化方法为:将减数B取反,然后进位输入Cin变为1,再进行加法运算。

设计好1为的全加全减器后进行封装。

然后用四个全加全减单元串联组成四位全加全减器。

然后关于控制端Sel ,只需用一个二选一的Mux,选择A或Z。

溢出的判断,不论是加法还是减法,在转化为加法运算后。

判断依据:两相加数符号相同,运算结果符号不同,则发生溢出。

2.电路设计:

设计软件:Quartus II 8.1

1.一位全加全减单元的电路图:(进行减法运算时初始进位的变化在完整电

路中用Addsub做Cin实现)

封装后:

一位全加/减器的仿真结果:(Cin=Addsub)

2.Sel控制端的实现电路:

封装后:

3.判断溢出的实现电路:

封装后:

4.完整电路图:。

《课程设计—加减法器》报告

电工17班王兴2011029170010

1.分析及设计方法:

要设计4位的全加全减器,首先要设计一位的全加器。

一位的全加器,需要3个输入,相加数A和B,还有进位输入Cin,2个输出,相加后的值S和进位输出Cout。

考虑到有一个控制端Addsub,所以要加一个输入。

然后考虑加法器转换为减法器。

转化方法为:将减数B取反,然后进位输入Cin变为1,再进行加法运算。

设计好1为的全加全减器后进行封装。

然后用四个全加全减单元串联组成四位全加全减器。

然后关于控制端Sel ,只需用一个二选一的Mux,选择A或Z。

溢出的判断,不论是加法还是减法,在转化为加法运算后。

判断依据:两相加数符号相同,运算结果符号不同,则发生溢出。

2.电路设计:

设计软件:Quartus II 8.1

1.一位全加全减单元的电路图:(进行减法运算时初始进位的变化在完整电

路中用Addsub做Cin实现)

封装后:

一位全加/减器的仿真结果:(Cin=Addsub)

2.Sel控制端的实现电路:

封装后:

3.判断溢出的实现电路:

封装后:

4.完整电路图:。