6_集成触发器及其应用电路设计与计数译码显示电路.ppt

- 格式:ppt

- 大小:3.54 MB

- 文档页数:40

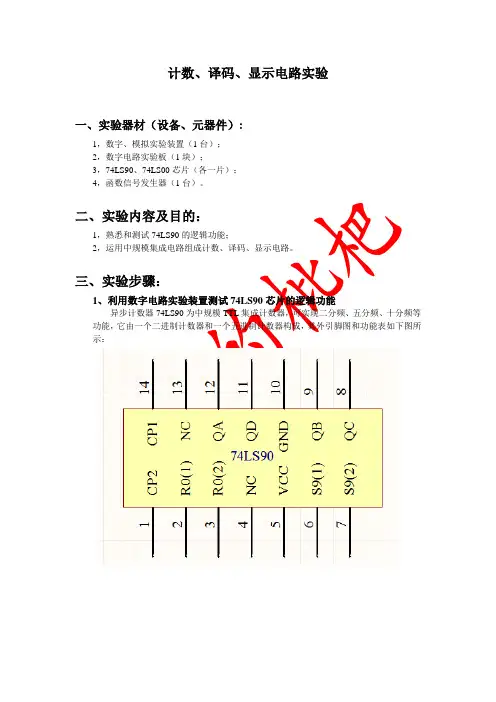

计数、译码、显示电路实验一、实验器材(设备、元器件):1,数字、模拟实验装置(1台);2,数字电路实验板(1块);3,74LS90、74LS00芯片(各一片);4,函数信号发生器(1台)。

二、实验内容及目的:1,熟悉和测试74LS90的逻辑功能;2,运用中规模集成电路组成计数、译码、显示电路。

三、实验步骤:1、利用数字电路实验装置测试74LS90芯片的逻辑功能异步计数器74LS90为中规模TTL集成计数器,可实现二分频、五分频、十分频等功能,它由一个二进制计数器和一个五进制计数器构成,其外引脚图和功能表如下图所示:异步:同步:满足1)2()1(00=∙R R ,1)2()1(=∙Sq Sq 时:①1CP =CP ,2CP =0时:二进制计数; ②1CP =0,2CP =CP 时:五进制计数;③1CP =CP ,2CP =A Q 时:8421码二进制计数; ④1CP =D Q ,2CP =CP 时:5421码十进制计数。

插好74LS90芯片,连好电源和接地端,计数脉冲由函数信号发生器提供,)1(0R 、)2(0R 、)1(9S 、)2(9S 分别接逻辑开关,四个输出端接电平显示或数码管,按功能表拨动开关验证其结果。

2,设计一个显示星期的计数器,使之重复0——6的显示(用74LS90与74LS00实现)利用反馈归零法可以使74LS90实现十以内的N 进制计数器,即从0记到要设计的进制时使清零端)1(0R 、)2(0R 有效(同时为高电平),进而反馈清零。

此实验实现0——6显示,即设计七进制数,当计数器计到111时,用反馈清零法使之为000,故先将)1(9S 、)2(9S 接地,1CP 接计数脉冲CP ,2CP 接A Q ,构成十进制数,再由于此只为七进制,故只用到A Q 、B Q 、C Q ,又用74LS00,故可使C Q 接B Q 、A Q 与非后再和“1”与非后接)2(0R ,使得当计数器计到111时,)1(0R 、)2(0R 实现清零。