硅外延及其应用

- 格式:docx

- 大小:46.23 KB

- 文档页数:12

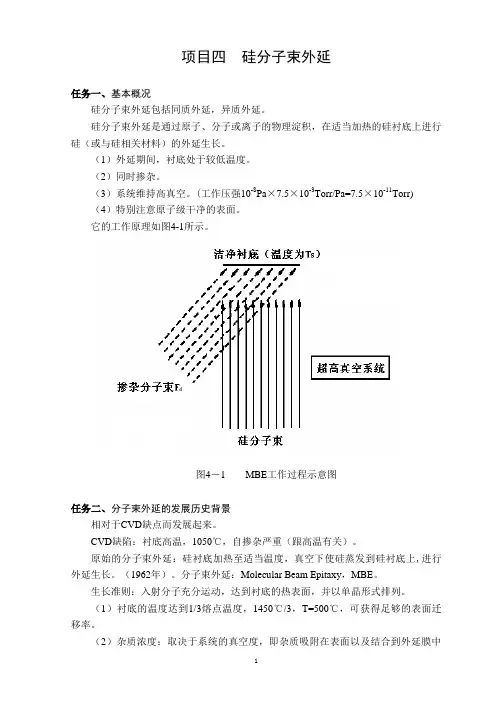

项目四硅分子束外延任务一、基本概况硅分子束外延包括同质外延,异质外延。

硅分子束外延是通过原子、分子或离子的物理淀积,在适当加热的硅衬底上进行硅(或与硅相关材料)的外延生长。

(1)外延期间,衬底处于较低温度。

(2)同时掺杂。

(3)系统维持高真空。

(工作压强10-8Pa×7.5×10-3Torr/Pa=7.5×10-11Torr)(4)特别注意原子级干净的表面。

它的工作原理如图4-1所示。

图4-1 MBE工作过程示意图任务二、分子束外延的发展历史背景相对于CVD缺点而发展起来。

CVD缺陷:衬底高温,1050℃,自掺杂严重(跟高温有关)。

原始的分子束外延:硅衬底加热至适当温度,真空下使硅蒸发到硅衬底上,进行外延生长。

(1962年)。

分子束外延:Molecular Beam Epitaxy,MBE。

生长准则:入射分子充分运动,达到衬底的热表面,并以单晶形式排列。

(1)衬底的温度达到1/3熔点温度,1450℃/3,T=500℃,可获得足够的表面迁移率。

(2)杂质浓度:取决于系统的真空度,即杂质吸附在表面以及结合到外延膜中的程度。

硅蒸发技术:1、电阻加热,瞬间蒸发。

2、电子轰击蒸发。

在低工作压强中进行,玷污成主要问题。

氧、氢存在,表面只有小部分结合,晶体产生缺陷,衬底温度T S升高,生长速率增高,1μm/min增至1.5μm/min, T S=1200︒C,但掺杂无法控制。

超高真空系统出现(Ultrahigh Vacuum UHV),本底真空度降至10-9Pa,生长速率R e下降,T S下降。

在杂质吸附系数S、衬底温度T S条件下,可根据图4-2定性地估计杂质的浓度。

图4-2 本底杂质浓度和本底压强的关系外延膜掺杂浓度随掺杂源浓度、生长速率以及衬底温度的变化有不同的模型,它可用脱附系数,吸附系数,以及蒸气压来表示。

至今MBE的参杂仍是一个重要课题。

过去曾得到硅中掺锑的外延膜,摸索并了解得吸附系数与锑流量及衬底温度之间的关系。

硅基锗材料的外延生长及其应用摘要:硅是最重要的半导体材料,在信息产业中起着不可替代的作用。

但是硅材料也有一些物理局限性,比如它是间接带隙半导体材料,它的载流子迁移率低,所以硅材料的发光效率很低,器件速度比较慢。

在硅衬底上外延生长其它半导体材料,可以充分发挥各自的优点,弥补硅材料的不足。

本文介绍了硅衬底上的锗材料外延生长技术进展,讨论了该材料在微电子和光电子等方面的可能应用,重点介绍了它在硅基高速长波长光电探测器研制方面的应用。

关键词:硅基;锗,外延;光电探测器Epitaxy and application of Ge layer on Silicon substrateHuiwen Nie1, Buwen Cheng2(1.Hunan Chemical Engineering Machinery School, Hunan Industrial Technology College2.State Key Laboratory on Integrated Optoelectronics, Instituteof Semiconductors, Chinese Academy of Sciences, Beijing 100083)Abstract: Silicon is the most important semiconductor material and it is irreplaceable in the information industry. But Silicon also has some shortcomings, such as very low luminescence efficiency and low device speed due to the indirect bandgap and low carrier mobility. Growing other semiconductors on Si substrate can take the advantages of the different semiconductors and improve the performance of theSi-based devices and integrated circuits. The progress of Ge growth on Si was introduced in the paper. The application of the Si-based Ge epitaxy layer was discussed, especially the application on Si-based high speed photodetectors operating at long wavelength.Key words: Si-based, Germanium, Epitaxy, Photodetector1引言硅基光电集成将微电子技术和光子学技术进行融合,是微电子技术的继承和发展,是信息技术发展的重要前沿研究领域。

外延工艺在集成电路制造产业中的应用外延工艺是一种在集成电路制造过程中广泛应用的工艺技术。

它通过在硅基材料上形成一个或多个较厚的外延层,使晶体管等器件得以制造和集成。

这种工艺的应用不仅提升了晶体管的性能和质量,还促进了集成电路的封装密度和可靠性。

首先,外延工艺在集成电路制造中的应用体现在提高晶体管性能方面。

通过外延工艺,可以在晶片表面上形成高质量的薄膜材料,这些薄膜可以用于制造不同类型的器件。

例如,外延层可以用于制造MOS晶体管的栅极、源极和漏极等关键部件,从而提高晶体管的导电性和开关速度。

其次,外延工艺在集成电路制造中的应用还体现在提高集成度方面。

外延工艺可以实现不同材料之间的垂直和水平集成。

在垂直集成方面,通过在原有晶片上叠加外延层,可以制造多层晶体管结构,从而提高芯片的功能集成度。

在水平集成方面,外延工艺可以实现在同一晶片上集成不同材料的器件,如光电二极管和磁电传感器等,从而拓宽了集成电路的应用领域。

此外,外延工艺的应用还能提升集成电路的可靠性。

外延层具有较高的晶体质量和良好的晶体匹配性,因此可以有效减少晶体管的漏电流和热噪声等问题,提高电路的稳定性和可靠性。

同时,由于外延层具有良好的电学和机械性能,可以减少封装过程中的应力和热膨胀问题,降低退化和失效的风险。

综上所述,外延工艺在集成电路制造产业中具有广泛的应用。

它可以提高晶体管的性能和质量,拓宽集成度,提升电路可靠性,为集成电路制造业带来更多的发展机遇。

随着科技的不断进步和需求的不断变化,相信外延工艺在集成电路制造领域的应用前景将更加广阔。

当谈及外延工艺在集成电路制造产业中的应用时,有几个关键方面需要考虑。

首先,外延工艺可以实现材料的选择和调控。

在集成电路制造中,选择合适的材料对电路性能至关重要。

通过外延工艺,可以在晶片表面沉积不同材料的薄膜层,例如氮化镓、氮化铝和氮化硅等。

这种材料的选择可以根据电路应用的需求来进行调控,从而实现对电路性能和功耗的优化。

硅外延及其应用徐远志;胡亮;吴忠元【摘要】Silicon epitaxy growth technology is introduced,and three kindsof technologies applied to silicon epitaxy are summarized:molecular beam epitaxy (MBE),chemical vapor deposition (CVD),liquid deposition (LPE),and the application of Si base epitaxial material device is also introduced.%介绍了硅外延生长技术,综述了应用于硅外延的分子束外延(MBE)、化学气相沉积(CVD)、液相沉积(LPE)三种工艺,并介绍了Si基外延材料器件的应用.【期刊名称】《云南冶金》【年(卷),期】2013(042)003【总页数】5页(P46-50)【关键词】MBE;CVD;LPE;硅外延;应用【作者】徐远志;胡亮;吴忠元【作者单位】昆明冶研新材料股份有限公司,云南昆明650031;昆明理工大学化学工程学院,云南昆明650500;昆明理工大学化学工程学院,云南昆明650500;昆明理工大学化学工程学院,云南昆明650500【正文语种】中文【中图分类】TN304.1+2硅具有储量丰富、价格低廉、热性能与机械性能优良、易于生长大尺寸高纯度晶体等优点。

目前,硅半导体材料仍是电子信息产业最主要的基础材料,95%以上的半导体器件和99%以上的集成电路(IC)是用硅材料制作的。

在21 世纪,它的主导和核心地位仍不会动摇。

半导体制造商生产IC 芯片用硅片分别采用硅抛光片(PW)和硅外延片以及非抛光片三种类型,用量最多的为前二类硅片。

半导体硅材料自从60 年代被广泛应用于各类电子元器件以来,其用量保持高速增长。

SEMI(国际半导体设备与材料协会)报告预测了晶圆的需求前景,2013 年预计99.95 亿in2 (不包括非抛光硅片)。

20 世纪80 年代早期开始使用外延片,它具有标准PW 所不具有的某些电学特性并消除了许多在晶体生长和其后的晶片加工中所引入的表面/近表面缺陷。

因此,硅外延片广泛应用于制作不可恢复器件,包括MPU、逻辑电路芯片、快闪存储器、DRAM 等,在CM OS 电路中应用最广泛,在提高器件性能和芯片成品率方面,比抛光片更有优势。

外延生长是制备半导体材料和器件的一项重要技术。

外延生长的方法很多,主要有气相外延(VPE)、分子束外延(MBE)、液相外延(LPE)等,采用这些方法已经制备出了CMOS 产品、红外焦平面探测器、光波导、光调制器等大量的半导体器件。

1 硅外延生长及硅外延片结构形式1.1 半导体硅材料与硅外延生长人类的科学发展过程可以看成是一个不停寻找新材料的过程。

半导体材料的发展开启了信息时代的大门,信息时代的特征性材料是硅,如今,以硅为原料的电子元件产值超过了以钢为原料的产值,人类的历史因而正式进入了一个新时代──硅器时代。

硅是地壳中最常见的元素,把石头变成硅片的过程是一项点石成金的成就也是近代科学的奇迹之一。

电子工业的发展历史表明,没有半导体硅材料的发展,就不可能有集成电路、电子工业和信息技术的发展。

半导体硅材料分为多晶硅、单晶硅、硅外延片以及非晶硅、浇注多晶硅、淀积和溅射非晶硅等。

现行多晶硅生产工艺主要有改良西门子法和硅烷热分解法。

主要产品有棒状和粒状两种,主要是用作制备单晶硅以及太阳能电池等。

生长单晶硅的工艺可分为区熔(FZ)和直拉(CZ)两种。

其中,直拉硅单晶(CZ-Si)广泛应用于集成电路和中小功率器件。

区域熔单晶(FZ-Si)目前主要用于大功率半导体器件,比如整流二极管,硅可控整流器,大功率晶体管等。

单晶硅和多晶硅应用最广。

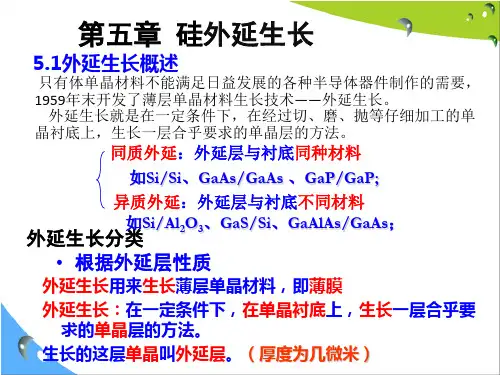

只有体单晶材料不能满足日益发展的各种半导体器件制作的需要。

为了制造高频大功率器件,需要减小集电极串联电阻,1959 年末开发了薄层单晶材料生长技术──外延生长。

外延生长实质上是一种材料科学的薄膜加工方法,其含义是:在一个单晶衬底上,沿着原来的结晶方向定向生长出与基底晶态结构相同或类似的晶态薄膜层。

由于所生长的薄膜层是衬底晶格的延伸,所以叫做外延层。

在外延生长过程中,一般要求能控制结晶的生长取向和杂质的含量,是产生具有特殊物理性质的半导体晶态薄膜层的重要方法[1-3]。

随着集成电路特征线宽尺寸的不断减小,对硅片的要求越来越高,控制单晶的原生缺陷变得愈来愈困难,因此外延片越来越多地被采用。

目前8 in硅片有很大部分是以外延片形式提供的,而12 in芯片生产线将全部采用外延。

今后,集成电路高集成度、微型化和低成本的要求对半导体单晶材料的电阻率均匀性、金属杂质含量、微缺陷、晶片平整度、表面洁净度等提出了更加苛刻的要求,晶片大尺寸和高质量成为必然趋势。

目前全球主流硅晶片已由直径8 in 逐渐过渡到12 in 晶片,研制水平已达到16 in。

1.2 硅外延生长类型根据外延层的性质,生长方法和器件制作方式不同,可以把外延分成不同的种类。

1)按照衬底和外延层的化学成分异同分类同质外延:外延层与衬底是同种材料,例如在硅衬底上外延生长硅;异质外延:衬底材料和外延层是不同种材料,例如在蓝宝石上外延生长硅。

2)按器件位置分类正外延:器件制作在外延层上;反外延:器件制作在衬底上,外延层只起支撑作用。

3)按外延生长方法分类直接外延:用加热、电子轰击或外加电场等方法使生长的材料原子获得足够能量,直接迁移沉积在衬底表面上完成外延生长的方法,如真空淀积、溅射、升华等。

例如硅的电子束蒸发外延生长;间接外延:利用化学反应在衬底表面上沉积生长外延层,广义上称为化学气相沉积(chemical vapor deposition,CVD)。

但CVD 所生长的薄膜不一定是单晶,因此严格地讲只有生长的薄膜是单晶的CVD 才是外延生长。

这种方法设备简单,外延层的各种参数较容易控制,重复性好。

目前硅外延生长主要是利用这种方法。

该方法还发展出了金属有机物 CVD (MOCVD)、等离子增强 CVD(PECVD)、超高真空CVD (UHVCVD)、快速热处理CVD (RTCVD)及激光、可见光、X 射线辅助CVD 等多种方法。

4)按照反应机理可分为利用化学反应的外延生长和利用物理反应的外延生长。

5)按向衬底输运外延材料的原子的方法不同又分为真空外延、气相外延、液相外延等。

6)按生长过程中的相变方式可分为气相外延、液相外延和固相外延等。

1.3 硅外延片结构形式硅片厚度一般为0.6 mm 左右,制作在其表面的IC 只占用约0.1%的深度(相当于几百nm),余下的绝大部分对IC 起支撑作用,所以称为衬底。

根据外延层与衬底的物质成分,外延层可分为同质生长层和异质生长层。

根据外延层与衬底的结晶形态,可将外延层可分为共度生长层和不共度生长层。

衬底与生长层的晶格类型相同且晶格常数相等(匹配)时,称为共度生长。

同质外延都是共度生长。

不共度生长的含义是衬底与生长层的晶格常数略有不同(称为失配)。

典型例子有蓝宝石上的硅生长和硅上的GaAs 生长。

当晶格常数略有不同(失配)时,对于较薄的异质外延层,外延层与衬底之间产生的是应力而不是缺陷,这种情况称为赝晶生长,例如硅上外延生长GexSi1-x 层。

外延生长与掺杂技术的目的类似,都是形成具有一定导电类型和杂质浓度的半导体层,其质量要求主要有下面几条:①具有一定的厚度,且厚度均匀。

②掺杂浓度(表现为电阻率)均匀并符合设计要求。

③位错、层错、麻坑、雾状缺陷、伤痕等缺陷尽量少④杂质分布满足要求。

2 外延生长方法为了提高半导体器件的成品率和性能,降低成本,研制新器件,对硅外延提出了多种要求,为此外延工作者做了大量的研究工作,发展了外延生长技术:液相外延、化学气相外延、减压外延、低温外延、选择外延、抑制外延、分子束外延和原子层外延等。

下面主要介绍分子束外延、化学气相外延和液相外延。

2.1 分子束外延分子束外延(MBE)是50 年代用真空蒸发技术制备半导体薄膜材料发展而来的一种新的晶体生长技术,并随着超高真空技术的发展而日趋完善,开拓了一系列崭新的超晶格器件,扩展了半导体科学应用的新领域。

其方法是将半导体衬底放置在超高真空腔体中,和将需要生长的单晶物质按元素的不同分别放在喷射炉中,由分别加热到相应温度的各元素喷射出的分子流能在上述衬底上生长出极薄的单晶体和几种物质交替的超晶格结构。

分子束外延技术在新型电子器件制造、电磁应用、光学应用等领域中,被用于氧化物材料的沉积[4]。

周立庆[5]等采用分子束外延法,在3 in Si 晶片上进行碲镉汞外延用CdTe 复合衬底的制备研究。

结果表明复合衬底的表面宏观缺陷密度低于300cm-2,双晶衍射峰宽值在80 arcsec 以下,位错密度的平均值低于5.0×106/cm2。

测试分析结果表明碲化镉薄膜的晶向得到了较好的控制,孪晶得到了抑制,且具有较好的晶体结构质量和均匀性。

苏少坚等[6]采用分子束外延法在Si (001)衬底上生长出Ge0.975Sn0.025 合金薄膜。

测试结果表明Ge0.975Sn0.025 合金薄膜具有很好的晶体质量,并且没有发生Sn 表面分凝,在500℃下具有很好的热稳定性。

唐军等[7]利用分子束外延共沉积法,首先在Si (111)衬底上生长高质量的SiC缓冲层,然后在SiC/Si 表面直接沉积碳原子制备石墨烯薄膜,并研究了不同衬底温度对薄膜结构的影响。

测试结果表明衬底温度为1000℃时结晶质量最好。

2.2 化学气相沉积法化学气相沉积法(CVD)是反应物质在气态条件下与基体表面相互作用,并在基体表面形成一种金属或化合物固态薄膜或镀层[8],是一种制备无机材料的新技术。

随着工业生产要求的不断提高,CVD 的工艺及设备得到不断改进,不仅启用了各种新型的加热源,还充分利用等离子体、激光、电子束、紫外光等辅助方法降低了反应温度,开发了诸如等离子体化学气相沉积(PECVD)、激光辅助化学气相沉积(LCVD)[9]、超高真空化学气相沉积(UHVCVD)、紫外光能量辅助化学气相沉积(UVCVD)[10]和热丝化学气相沉积法(HWCVD)[11]等新技术,使其应用的范围更加广阔。

目前,CVD 技术广泛应用于制备粉体材料,新晶体材料等领域,在作为大规模集成电路技术的光电材料、铁电材料的薄膜制备技术方面,更是发挥着巨大的作用。

戴显英等[12]采用了UVCVD 和UHVCVD 相结合的技术外延生长SiGe/Si HBT 材料,并研制出了SiGe HBT 器件。

结果表明该技术能显著降低材料的外延生长温度,减小有害杂质的污染,提高材料的性能。