一种集成电路产品测试系统的设计与实现

- 格式:pdf

- 大小:233.22 KB

- 文档页数:4

基于PMU的小型集成电路测试系统实现及性能分析祝新军;纪效礼;何少佳【摘要】文中给出了一种基于精密测量单元的小型集成电路测试系统的设计方法,并对小功率范围进行详细实验验证;该测试系统将电压/电流钳位技术、比较技术、功率扩展技术、恒流源和恒压源技术和四象限驱动技术等多项技术相结合,能够对被测器件(DUT)施加精确地激励值,并准确测量DUT在激励下的响应,该系统同时具备大功率扩展能力满足多种电路测试的需求;系统借助四通道集成仪表放大器电路,结合嵌入式控制器、功率扩展电路以及上位机控制界面共同完成设计,解决了nA级电流无法准确测量的问题,通过优化补偿电路设计,提高电路测试速度;系统性能分析结果表明,文章所设计的小型集成电路测试系统测量精度高、施加激励稳定可靠、响应速度快,相比类似产品节约2/3的硬件设计成本,能够满足集成电路测试中直流参数测试的要求.【期刊名称】《计算机测量与控制》【年(卷),期】2018(026)004【总页数】4页(P52-55)【关键词】集成电路;精密测量单元;直流参数测试;性能分析;嵌入式【作者】祝新军;纪效礼;何少佳【作者单位】绍兴职业技术学院,浙江绍兴312000;桂林电子科技大学机电工程学院,广西桂林541000;桂林电子科技大学机电工程学院,广西桂林541000【正文语种】中文【中图分类】TM1350 引言随着集成电路集成度的不断提高,集成电路的测试难度不断增大。

目前,主要依赖于集成电路自动测试仪(Automatic Test Equipment)完成集成电路测试。

ATE的测试原理是通过对被测器件(Device Under Test)施加激励和收集响应信号,与DUT的技术手册参数进行比对,从而判断DUT是否合格[1]。

集成电路测试仪主要应用在晶圆测试(中测)和成品测试(成测),文章中的集成电路测试系统针对成测中的直流参数测试进行设计。

从半导体技术的发展情况来看,芯片测试技术落后于芯片的制造速率,高性能的测试仪器价格昂贵,大大提高了电路测试的成本[2]。

一款SoC的功能测试系统的设计

关华深;罗春;罗明清

【期刊名称】《电子工程师》

【年(卷),期】2005(31)4

【摘要】针对一款基于ARM7TDMI处理器核的SoC(片上系统),设计了一个经济实用的功能测试系统,该系统采用宿主机/目标机结构。

文中分析了该系统的Host 程序和Monitor程序,然后以片外存储器接口模块测试、片上eSRAM(增强型SRAM)模块测试和USB客户端控制器模块测试为例,介绍SoC片上模块的测试方法。

该系统符合模块化的构建思想,对于设计其他SoC功能测试系统具有一定的借鉴作用。

【总页数】4页(P16-18)

【关键词】SoC;测试系统;模块测试;ARM7TDMI

【作者】关华深;罗春;罗明清

【作者单位】东南大学国家专用集成电路系统工程技术研究中心

【正文语种】中文

【中图分类】TN407

【相关文献】

1.一种基于总线复用的SoC功能测试结构设计 [J], 虞致国;魏敬和;罗静

2.一款BD2/GPS双模导航芯片SoC子系统设计方案 [J], 林广栋;马宏星;朱家兵;陈金忠

3.SOC功能测试系统的设计与实现 [J], 何雷;赵文登;黄少珉

4.一款高端数字SOC设计的系统级验证 [J], 杜敏;王世明

5.SOC功能测试系统的设计与实现 [J], 何雷;赵文登;黄少珉

因版权原因,仅展示原文概要,查看原文内容请购买。

集成电路的片上系统集成与设计技术手段集成电路(IC)是现代电子设备的核心组成部分,它通过将大量的微小电子元件,如晶体管、电阻、电容等,集成在一块小的硅片上,实现了复杂的功能。

随着科技的快速发展,集成电路的功能越来越强大,片上系统(System-on-Chip, SoC)的概念应运而生。

片上系统集成与设计技术手段成为集成电路领域的重要研究方向。

1. 片上系统集成片上系统集成是指将整个系统或多个系统集成在一块集成电路芯片上,从而实现各种功能。

这种集成方式可以大大缩小系统的体积,降低功耗,提高性能和可靠性。

SoC的集成度可以从简单的微处理器核心和几块模拟电路,到复杂的包含多个处理器核心、图形处理单元、数字信号处理器、存储器、接口等全功能系统。

2. 设计技术手段为了实现高集成度的片上系统,设计人员需要采用多种先进的设计技术手段:2.1 硬件描述语言(HDL)硬件描述语言是用于描述电子系统结构和行为的语言,如Verilog和VHDL。

通过使用HDL,设计人员可以在抽象层次上描述整个系统,而无需关心底层电路的具体实现。

这使得设计人员能够更加专注于系统的功能和性能,提高设计效率。

2.2 库和IP核心在片上系统集成过程中,利用已有的库和IP(Intellectual Property)核心可以大大缩短设计周期。

库提供了常用的模块,如乘法器、加法器等;IP核心则是预先设计好的模块,如处理器核心、DSP核心等。

通过复用这些模块和核心,设计人员可以快速构建复杂的片上系统。

2.3 综合和布局规划综合是将HDL描述转换为底层电路的过程。

在这个过程中,综合工具会考虑电路的性能、面积和功耗等因素,自动选择合适的电路实现。

布局规划则是确定电路在芯片上的位置和连接关系,其目标是优化电路的性能和功耗,同时满足面积和制造要求。

2.4 仿真和验证在设计过程中,需要进行多次仿真和验证,以确保设计的正确性和可靠性。

仿真是在软件层面上模拟电路的行为,验证则是通过测试芯片来验证电路的功能和性能。

高速集成电路器件测试仪器的多通道设计与实现摘要:本文旨在设计和实现一套高速集成电路器件测试仪器的多通道系统,以提高测试效率和准确度。

首先,介绍了高速集成电路器件测试的背景和意义。

然后,详细讨论了多通道设计的原理和方法。

接着,提出了一种基于嵌入式系统的多通道测试仪器的设计方案,并对系统的硬件和软件进行了详细说明。

最后,通过实验验证了该系统的性能和可靠性,并对其进行了评估和总结。

1.引言高速集成电路器件的测试是集成电路产业中不可或缺的一环。

随着技术的进步,集成电路器件的速度和复杂性越来越高,传统的单通道测试设备已无法满足对高速器件的测试需求。

因此,设计一套多通道测试仪器具有重要意义。

2.多通道设计原理与方法多通道设计是通过同时测试多个器件来提高测试效率的技术。

其中,一个关键问题是如何实现多个通道的同步控制与数据处理。

常用的方法有硬件同步控制和数字信号处理技术。

2.1 硬件同步控制硬件同步控制是通过硬件电路实现多个通道的同步工作。

其核心是设计一个时钟同步电路,保证多个通道的时钟信号保持同步。

此外,还需要设计一个触发电路,用于控制测试信号和采样时机。

通过合理设计电路,可以实现多个通道的精确同步。

2.2 数字信号处理技术数字信号处理技术是通过软件算法对采样到的信号进行处理和分析,以提取关键信息。

常用的数字信号处理技术包括滤波、频谱分析和时域分析等。

通过合理选择数字信号处理算法,可以提高测试的准确度和可靠性。

3.基于嵌入式系统的多通道测试仪器设计方案基于嵌入式系统的多通道测试仪器具有体积小、功耗低以及可编程性强的优点,适用于高速集成电路器件的测试。

本文提出一种基于嵌入式系统的多通道测试仪器设计方案,包括硬件和软件两部分。

3.1 硬件设计硬件设计包括多通道测试仪器的模拟前端电路、数字信号处理电路和通信接口电路。

模拟前端电路负责信号的采样和增益调节,数字信号处理电路负责信号的处理和分析,通信接口电路负责与外部设备的数据交互。

集成电路综合自动测试系统硬件平台设计摘要:集成电路作为信息技术等领域的基石,是各类战略性新兴产业发展的关键基础。

集成电路测试贯穿集成电路设计、制造、封装、应用整个过程,根据不同环节的不同,可以分成设计验证测试、工艺监控测试、圆片测试、成品测试、可靠性测试和用户测试;根据测试电路对象不同,可以分为针对低集成度、单一功能芯片的专用低端设备,针对高集成度、低功耗新型SOC类芯片的测试设备,以及针对高性能DSP、高端SOC芯片设备。

下面,文章就集成电路综合自动测试系统硬件平台设计展开论述。

关键词:集成电路;测试系统;硬件平台1研究背景党的二十大报告提出:“推动战略性新兴产业融合集群发展,构建新一代信息技术、人工智能、生物技术、新能源、新材料、高端装备、绿色环保等一批新的增长引擎”。

集成电路作为信息技术等领域的基石,是各类战略性新兴产业发展的关键基础。

2022年,国家发展改革委、教育部、财政部、商务部等多个国家部委就集成电路产业税收优惠、推进基础电路领域人才培养、打造集成电路企业和产品市场准入平台等多个方向发布了各类支持政策。

2021年,国务院发布的《“十四五”数字经济发展规划》中指出,瞄准传感器、量子信息、网络通信、集成电路等战略性、前瞻性领域,提高数字技术基础研发能力。

完善5G、集成电路、新能源汽车、人工智能、工业互联网等重点产业链供应链体系[1]。

针对当前国内集成电路产业快速发展的现状,为进一步提升国产高性能集成电路测试设备水平、满足产量不断提升的高性能国产集成电路设计验证、量产测试等测试需求,研制国产超大规模集成电路综合自动测试系统,未来可有效满足国产超大规模集成电路测试需要。

2系统总体设计超大规模集成电路综合自动测试验证系统主要包含硬件平台、软件平台。

硬件平台作为基础支撑平台,提供被测试集成电路所需的硬件测试资源。

软件平台作为实现测试验证的基础软件环境。

超大规模集成电路综合测试验证系统总体组成框图如图1所示。

集成电路制造中的先进制程控制系统设计与实现导言:随着科技的不断进步和人类对高性能电子产品的日益需求,集成电路技术的发展迅猛。

而在集成电路的制造过程中,制程控制系统的设计与实现起着至关重要的作用。

本文将详细介绍集成电路制造中先进制程控制系统的设计与实现的关键技术和方法。

一、先进制程控制系统的基本概念和作用先进制程控制系统是指在集成电路制造过程中,采用先进技术和方法,对关键制程参数进行精确控制和调整的自动化系统。

它通过对制程参数的实时监测、数据处理和决策,以及对设备和工艺参数的调整,实现集成电路制造过程的稳定和高效。

先进制程控制系统的设计与实现可以提升制程品质、降低制程成本,同时提高晶片性能和可靠性。

二、先进制程控制系统设计的关键技术和方法1. 建立制程参数模型:通过对制程过程和设备进行建模,识别出关键制程参数和其与晶片性能之间的关系,建立准确的制程参数模型,为后续的控制和优化提供基础。

2. 实时监测和质量控制:通过在制程过程中安装传感器和监测装置,实时对关键制程参数进行监测,并将数据与理论模型进行比对和分析,及时发现异常情况并采取相应措施,保障制程品质的稳定和一致性。

3. 智能决策与调整:基于制程参数模型和实时监测数据,利用人工智能和机器学习算法,对制程过程进行智能化决策和调整。

通过对历史数据的分析和模式识别,系统能够预测制程偏差和异常情况,提前调整设备参数或工艺流程,实现制程的自适应优化。

4. 设备和工艺参数优化:通过对设备和工艺参数进行优化调整,以尽量减小制程偏差和提高晶片品质。

利用先进的优化算法和自动控制方法,对制程过程中的设备运行状态和工艺参数进行实时调整和优化,以达到最优的制程控制效果。

三、先进制程控制系统的实现案例以半导体制造为例,现代先进制程控制系统的实现有很多成功案例。

例如,某大型半导体制造企业利用先进制程控制系统,成功实现了制程参数的实时监测和调整。

通过对金属印刷、光刻和化学机械抛光工艺的控制,实现了晶圆表面的平整度和平行度的提高,大幅度降低了晶圆的损坏率和制程缺陷率。

数字集成电路测试系统的设计与实现摘要:基于AT89C51单片机,设计出一种简易的数字集成电路测试系统。

测试仪所采取的是多值参数相比较的方法,再利用单片机控制功能以及数学运算的功能,测试数字IC的功能,并同步完成每项直流参数的测试。

各路显示测试项目参数以及测量过程中量程的切换等,由8279键盘进行控制实现。

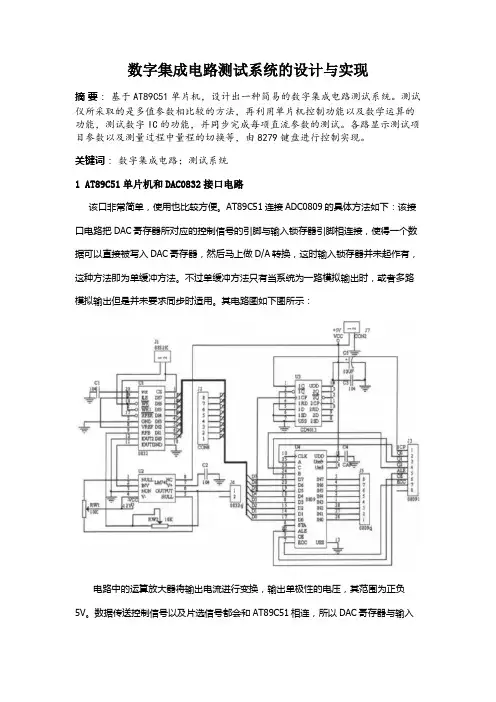

关键词:数字集成电路;测试系统1 AT89C51单片机和DAC0832接口电路该口非常简单,使用也比较方便。

AT89C51连接ADC0809的具体方法如下:该接口电路把DAC寄存器所对应的控制信号的引脚与输入锁存器引脚相连接,使得一个数据可以直接被写入DAC寄存器,然后马上做D/A转换,这时输入锁存器并未起作有,这种方法即为单缓冲方法。

不过单缓冲方法只有当系统为一路模拟输出时,或者多路模拟输出但是并未要求同步时适用。

其电路图如下图所示:电路中的运算放大器将输出电流进行变换,输出单极性的电压,其范围为正负5V。

数据传送控制信号以及片选信号都会和AT89C51相连,所以DAC寄存器与输入锁存器的地址相同。

WR1和WR2都会连接AT89C51的写信号线。

当CPU对DAC0832执行一次写操作时,会把一个数据直接写进DAC寄存器,则DAC0832输出模拟量也会随之变化。

因为DAC0832本身具备数字量输入锁存的功能,因此能直接AT89C51P0口送入数字量。

VREF的极性决定电路的极性,如果VRER为正,则VOUT 是负,反之则为正。

2 多路模拟开关电路该模拟电路所采用的是三片CD4066四双向模拟开关,该开关主要对高电平输入时关断进行控制,是独立的双模拟开关,通常用在信号的开关、调制解调以及消波电路等。

分别有四个独立模拟开关在CD4066的封装内,各模拟开关又有三个端子来进行输出、输入以及控制,输出和输入端子可以互相交换。

如果在控制端加高电平,开关处于导通状态,加低电平则开关断开。

当模拟开关处于导通状态时,电阻一般有几十欧,如果模拟开关处于断开的状态,则会呈现出高阻抗,为开路。

数字集成电路是现代电子产品中不可或缺的一部分,它们广泛应用于计算机、手机、汽车、医疗设备等领域。

数字集成电路通过在芯片上集成大量的数字电子元件,实现了电子系统的高度集成和高速运算。

本文将从电路、系统与设计三个方面探讨数字集成电路的相关内容。

一、数字集成电路的电路结构数字集成电路的电路结构主要包括逻辑门、寄存器、计数器等基本元件。

其中,逻辑门是数字集成电路中最基本的构建元件,包括与门、或门、非门等,通过逻辑门的组合可以实现各种复杂的逻辑功能。

寄存器是用于存储数据的元件,通常由触发器构成;而计数器则可以实现计数和计时功能。

这些基本的电路结构构成了数字集成电路的基础,为实现各种数字系统提供了必要的支持。

二、数字集成电路与数字系统数字集成电路是数字系统的核心组成部分,数字系统是以数字信号为处理对象的系统。

数字系统通常包括输入输出接口、控制单元、运算器、存储器等部分,数字集成电路在其中充当着处理和控制信号的角色。

数字系统的设计需要充分考虑数字集成电路的特性,包括时序和逻辑的正确性、面积和功耗的优化等方面。

数字集成电路的发展也推动了数字系统的不断完善和创新,使得数字系统在各个领域得到了广泛的应用。

三、数字集成电路的设计方法数字集成电路的设计过程通常包括需求分析、总体设计、逻辑设计、电路设计、物理设计等阶段。

需求分析阶段需要充分了解数字系统的功能需求,并将其转化为具体的电路规格。

总体设计阶段需要根据需求分析的结果确定电路的整体结构和功能分配。

逻辑设计阶段是将总体设计转化为逻辑电路图,其中需要考虑逻辑函数、时序关系、并行性等问题。

电路设计阶段是将逻辑电路图转化为电路级电路图,包括门电路的选择和优化等。

物理设计阶段则是将电路级电路图转化为实际的版图设计,考虑布线、功耗、散热等问题。

在每个设计阶段都需要充分考虑电路的性能、面积、功耗等指标,以实现设计的最优化。

结语数字集成电路作为现代电子系统的关键组成部分,对于数字系统的功能和性能起着至关重要的作用。

电子设计领域集成电路测试与验证的技术方法在电子设计领域中,集成电路的测试与验证是确保电路设计质量和可靠性的重要环节。

随着电子技术的不断发展和集成电路复杂度的增加,测试与验证技术的重要性也日益凸显。

本文将介绍几种常用的集成电路测试与验证技术方法。

一、功能验证功能验证是测试与验证的基础环节,旨在验证电路在不同输入条件下是否能够正确地产生预期输出。

在功能验证中,可以采用仿真验证和实际硬件验证两种方法。

1. 仿真验证仿真验证是利用计算机软件对电路进行模拟和测试的方法。

通过建立电路的数学模型,可以模拟电路在不同输入下的输出情况,进而验证电路的功能和性能。

仿真验证的优点是成本低、可重复使用和调试方便,可以在电路设计的早期阶段进行验证。

常用的仿真工具有SPICE、Verilog和VHDL等。

2. 实际硬件验证实际硬件验证是将电路设计制作成实际的硬件原型,并通过实验室设备对其进行测试和验证的方法。

相比仿真验证,实际硬件验证更加接近真实环境,可以更准确地评估电路的性能。

实际硬件验证的缺点是成本高、周期长、调试困难,适合在电路设计的后期阶段进行验证。

二、电路板级测试和芯片级测试电路板级测试和芯片级测试是针对电路板和集成电路芯片进行的测试与验证方法,用于确保电路板和芯片的运行正常和性能优良。

1. 电路板级测试电路板级测试是针对整个电路板进行测试的方法。

在电路板级测试中,可以使用测试点和测试仪器对电路板进行全面的功能测试,以确保整个电路板的正常运行。

电路板级测试一般包括功能测试、耐压测试、温度测试等环节。

2. 芯片级测试芯片级测试是针对集成电路芯片进行测试的方法。

由于芯片集成度高、结构复杂,芯片级测试需要运用先进的测试技术和设备。

芯片级测试一般包括逻辑测试、信号测试、功耗测试等环节。

常用的芯片级测试方法有扫描链(Scan Chain)测试、缺陷模拟测试等。

三、自动化测试和在线测试自动化测试和在线测试是通过引入计算机和自动化设备来提高测试效率和精度的测试与验证方法。

集成电路设计与测试技术研究随着科技的迅速发展,集成电路设计与测试技术成为了电子产业的核心之一。

集成电路(Integrated Circuit,IC)是电子器件的核心,也是计算机、通信和各种电子设备的基础。

因此,研究集成电路设计和测试技术对于满足现代社会对数字化和智能化需求具有重要意义。

一、集成电路设计技术集成电路设计技术是指将多种功能电路集成于一片芯片上。

在集成电路设计中,主要涉及到以下几个方面的技术:1.电路设计方法电路设计包括逻辑电路设计和模拟电路设计。

逻辑电路设计主要关注数字电路的逻辑功能实现,采用的方法包括门电路设计、布线布局等。

模拟电路设计主要关注电路的波形与信号的连续性,采用的方法包括放大电路设计、滤波器设计等。

2.工艺技术工艺技术是指在集成电路设计的基础上,通过制造工艺将电路实现到硅片上。

工艺技术包括硅片制备、掩膜制备、微影技术、沉积与刻蚀技术等。

工艺技术的发展使得集成电路设计更加精密和复杂。

3.封装与封装技术封装是将芯片封装到外壳中,形成独立的集成电路芯片。

封装技术包括片上封装、球网阵列封装、多芯片模块封装等。

不同的封装方式适用于不同的应用场景,因此封装技术的选择对于集成电路设计至关重要。

二、集成电路测试技术集成电路测试技术是指通过各种测试手段对集成电路进行功能验证和可靠性评估。

在集成电路测试中,主要涉及以下几个方面的技术:1.功能测试技术功能测试是对集成电路进行各种功能的验证,确保其能够实现预期的功能。

功能测试技术包括边界扫描、逻辑仿真、故障模拟等。

通过功能测试可以发现电路中的故障,并及时进行修复。

2.可靠性测试技术可靠性测试是对集成电路进行长时间运行和极限工作条件下的测试,以验证其在不同工作环境下的可靠性和稳定性。

可靠性测试技术包括老化测试、温度测试、电压测试等。

可靠性测试可以提前识别电路在工作过程中可能出现的问题,避免不必要的损失。

3.自动化测试技术随着集成电路的复杂度不断增加,传统的手动测试已经无法满足需求。

基于PMU的小型集成电路测试系统实现及性能分析摘要:由于电路设计技术的飞速进步,集成电路的测试已成为确保电路可靠性的重要手段。

测试集成电路不仅可以确保其可靠性,还能够有效降低制造成本。

本文提出了一种基于PMU的小型集成电路测试系统的设计方法,该系统具有高精度、高稳定性、快速响应性的特点,同时,其硬件设计成本相对于其他类似产品明显降低,可以满足集成电路测试中对直流参数的需求。

关键词:PMU;小型集成电路;测试系统由于集成电路的技术日新月异,测试的难度也在不断攀升。

目前,测试方法主要是通过使用自动测试仪来完成。

结合我国半导体技术的发展状况来说,芯片测试技术已经远远落后于芯片制造速度,由于高性能测试仪器价格昂贵,这导致电路测试的成本大幅增加。

本文提出了一种全新的电路测试系统,旨在有效地降低集成电路测试的成本,同时满足小微集成电路测试用户对测试精度和速度的需求。

一、模拟集成电路测试仪的总体架构本文旨在探讨模拟集成电路测试仪的直流参数测试板(PAB)的设计原理、性能分析以及功能扩展,其由嵌入式控制器、总线接口电路、PAB板、MAB板和DUT适配板组成,可以满足多种应用场景的需求。

1、PAB电路的工作原理和结构组成为了确保模拟集成电路直流参数测试的准确性,DUT需接受恒流源和恒压源的激励,而PMU单元则负责施加激励,并进行相应的测量。

PAB板由电压源/电流源、钳位器件以及测量器件组成,为了满足测试系统的精确性和成本效益,我们采用了ADI公司的集成PMU外接功率扩展电路的方案来实施设计。

PMU由电压源、电流源、比较电路、钳位电路、测量电路以及补偿电路组成,具备良好的低频测量精度,但是由于功耗有限,因此需要通过额外功率对电路进行扩展。

DUT技术可以通过施加恒流源/恒压源激励来稳定电压/电流,以满足高功率需求,因此,我们使用了由大功率运算放大器和跟随器组成的负反馈电路。

经过对比,可以发现激励响应值与参数手册中的预期值存在差异,从而得出pass/fail的结论。

一种集成电路产品测试系统的设计与实现

曹维国1,邓中亮1,王峥2

1北京邮电大学电子工程学院,北京 (100876)

2凤凰微电子(中国)有限公司,北京 (100084)

E-mail:Weiguo.cao@

摘要:本文回顾了数字集成电路的测试技术;分析了该项技术在对SIM形式封装的数字集成电路测试中的缺陷和不足;针对目前的测试系统的单一和性能价格比例偏低的情况提出了一种新型的综合测试系统,详细介绍了该系统的工作原理及组成,讨论了该系统的软硬件设计方案,总结了其优点。

关键词:用户识别模块,集成电路,测试系统,精密测量单元

1.引言

数字集成电路测试的目的在于检测集成电路的故障并对检测到的故障进行定位、生成测试报告并对故障进行分类汇总以用于缺陷分析。

从测试技术上分可分为测试生成技术、响应鉴别技术、测试仪技术和易测设计技术等。

从测试方法上分可分为人工测试和穷举测试法、ATPG (自动测试图形生成)、DFT (Design For Test,可测性设计)、 BST (边界扫描测试)和BIST (Build In Self Test,内建自测试)[1]等。

从阶段可分为设计阶段测试、生产阶段测试和产品测试[2]。

测试技术和测试方法具有通用性和共用性,而阶段性测试则跟被测对象的不同会衍生不同的测试系统尤其是在产品测试阶段[3]。

设计阶段测试可借助强大的EDA(Electronic Design Automation,电子设计自动化)工具,生产阶段的测试由集成电路制造商完整的制造体系来保证,但是封装后的数字集成电路的外形各种各样,管脚有多有少,尤其是对SIM (Subscriber Identity Module,用户识别模块)形式封装的数字集成电路的产品外部只有8个管脚可以利用,从而造成了该类产品测试阶段通用性和专用性的矛盾。

目前针对SIM封装形式的数字集成电路进行产品测试的系统十分稀缺且都具有共同的不足:

1)没有补偿电路,无法进行回零测试;

2)只能进行电气性能的开短路和漏电流测试,无法进行加压测流和加流测压;

3)只能进行电气性能的测试,无法完成逻辑功能的测试;

4)价格比较高。

结合SIM封装形式的数字集成电路产品测试系统的要求和企业产品的具体应用进行设计开发了一套专用测试系统,实现对SIM封装形式的数字集成电路的逻辑功能测试和电气性能测试,并对测试的结果进行汇总分析形成报告以用于缺陷分析。

2.系统介绍

本测试系统由控制计算机﹑测试电路和测试适配器三部分组成.适用于SIM封装形式下的集成电路的开短路测试﹑工作电流测试﹑输入管脚漏电流测试﹑输出电平测试和基本逻辑功能测试。

并且具备16个芯片的并行测试能力。

系统框架图如图1所示:

图1 系统框架图

本测试系统的核心测试程序烧录在MCU(Micro Controller Unit,微控制单元)上[4],可以保证高效而又准确的对SIM进行电气性能的测试;PMU(Power Management Unit,精密测量单元)和DSP(Digital Signal Processing,数控电源)是本测试系统的核心部分,准确地为需要测试的管脚提供可编程电压、电流,并执行MCU的指令进行加压测流和加流测压;继电器矩阵则在上位机的控制下进行管脚的切换以完成测试逻辑功能模块和测试电气性能功能模块的切换,丰富测试系统的逻辑功能测试。

上位机完成对测试系统的控制,发送测试指令,接收测试结果并对结果进行判断,对不合格的产品的测量数据进行汇总和分析形成测试报告。

3.测试技术

3.1 逻辑功能测试

对SIM产品的逻辑功能测试即ATR(Answer To Reset,复位应答)测试。

ATR是SIM 对复位的响应而发送的一序列字节,它包括着与SIM传输协议有关的参数信息,这些信息是由SIM制造商预先写在SIM的ROM里的。

ATR要求的时序图如图2(图2中各管脚名称见表1)[5]:

图2 ATR时序图

表1 SIM管脚名称表

C1 C2 C3 C4 C5 C6 C7 C8

V CC RST CLK RFU GND V PP I/O RFU 3.2 电气性能测试

在进行电气性能测量之前测量系统会首先执行回零操作进行系统自身的校准。

本测试系

统采用12位A/D、D/A、分档和开尔文接发等手段来实现高精度测量。

主要的测量方法采

用FVMI(Force Voltage Measure Current,加压测流)、FIMV(Force Current Measure Voltage,

加流测压)和FVMV(Force Voltage Measure Voltage,加压测压)。

详细测量值、响应速度和分辨率要求范围请参阅参考文献[6]

,本文不进行详细说明。

4.软件设计

4.1 软件架构

以PC作为主机采用PCI扩展串口卡控制16个模块进行MOD1(电气性能测试模块)

和MOD2(SIM逻辑测试模块)两种模式的测试。

测试系统集成环境在Visual C++6.0下开

发完成,对话框为基本骨架,界面友好,可扩展性与可维护性都比较好。

图3 软件组织框架图

4.2 数据传输协议

表2数据传输协议

帧头AAH 地址字节后跟数据字节数N N-1个字节数据和校验字节

帧头AAH:作为一帧数据的开始地址字节:对应每个set的标志

后跟数据字节N:后面共有N字节的数据N-1个字节数据:测试数据体

校验字节:校验值[7]

5.结论

本文从产品测试的角度出发,结合了具体的SIM封装形式的数字集成电路的特殊要求,综合了逻辑功能测试和电气性能测试,在广泛调研、深人研讨和多次改版试验的基础上给出了基于SIM封装形式的数字集成电路的产品的测试方案。

不仅从设计的角度进行理论论证和从实用的角度进行分析,而且最终形成产品并在企业实际生产中得到了实践验证。

从实际生产的应用中再次证明了本系统能够高效准确地完成对不合格产品的筛选,并把不合格产品的故障进行定位,对不合格产品的故障类型进行分类汇总。

同时本测试系统的较低的成本和良好的可扩展性也为大规模的推广应用奠定了基础。

参考文献

[1]Steininger A.Testing and built-in self-test-A survey[J].Journal of Systems Architecture,2000,46:721.747

[2]Michael L. Bushnell, Vishwani D. Agrawal, 《超大规模集成电路测试》[M].北京:电子工业出版是,2005

[3]杨之廉.《集成电路导论》[M].北京:清华大学出版社, 2003

[4]何立民.《单片机高级教程》[M].北京:北京航空航天大学出版社, 2001

[5]Wolfgang Rankl, Wolfgang Effing, 《智能卡大全》[M].北京:电子工业出版是,2002

[6]中华人民共和国国家标准.《识别卡测试方法》GB/T 17554.3-2006[M].北京:中国标准出版社,2006

[7]李现勇.《Visual C++串口通讯技术与工程实现》[M],北京:人民邮电出版社,2002

An IC Testing System

Cao Weiguo1,Deng Zhongliang1,Wang Zheng2

1 Electronic Engineering School,Beijing University of Posts and Telecommunications,Beijing

(100876)

2 Phoenix Microelectronics (China) Co., Ltd.,Beijing (100084)

Abstract

This article briefly reviews the IC testing technology, and analyzes the disadvantages and limitations when it is applicable to the testing of ASIC packaged in SIM; meanwhile this article suggests a new integrated IC tesing system in order to improve the singleness and low performance-price ratio of the current testing system, then detailed illustrates the operation principle and structure of this new testing system and presents its software and hardware design solution as well as the system advantages. Keywords: SIM,IC,testing system,PMU。