第6章 寄存器与计数器

- 格式:ppt

- 大小:1.17 MB

- 文档页数:37

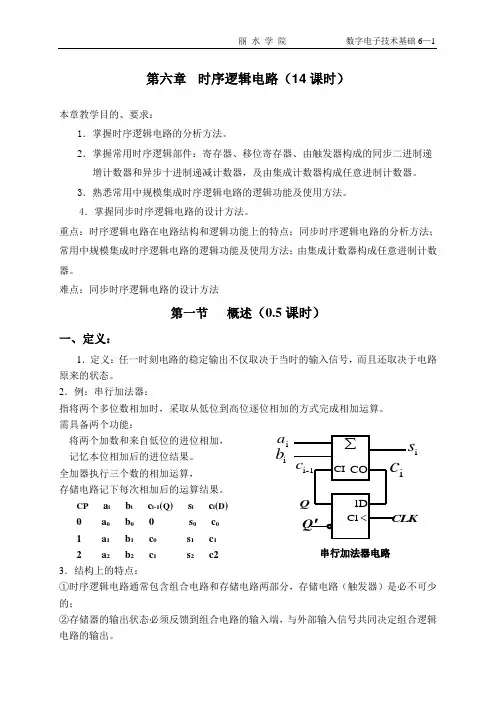

第六章 时序逻辑电路(14课时)本章教学目的、要求:1.掌握时序逻辑电路的分析方法。

2.掌握常用时序逻辑部件:寄存器、移位寄存器、由触发器构成的同步二进制递 增计数器和异步十进制递减计数器,及由集成计数器构成任意进制计数器。

3.熟悉常用中规模集成时序逻辑电路的逻辑功能及使用方法。

4.掌握同步时序逻辑电路的设计方法。

重点:时序逻辑电路在电路结构和逻辑功能上的特点;同步时序逻辑电路的分析方法;常用中规模集成时序逻辑电路的逻辑功能及使用方法;由集成计数器构成任意进制计数器。

难点:同步时序逻辑电路的设计方法第一节 概述(0.5课时)一、定义:1.定义:任一时刻电路的稳定输出不仅取决于当时的输入信号,而且还取决于电路原来的状态。

2.例:串行加法器:指将两个多位数相加时,采取从低位到高位逐位相加的方式完成相加运算。

需具备两个功能:将两个加数和来自低位的进位相加, 记忆本位相加后的进位结果。

全加器执行三个数的相加运算, 存储电路记下每次相加后的运算结果。

CP a i b i c i-1(Q ) s i c i (D )0 a 0 b 0 0 s 0 c 0 1 a 1 b 1 c 0 s 1 c 1 2 a 2 b 2 c 1 s 2 c2 3.结构上的特点:①时序逻辑电路通常包含组合电路和存储电路两部分,存储电路(触发器)是必不可少的;②存储器的输出状态必须反馈到组合电路的输入端,与外部输入信号共同决定组合逻辑电路的输出。

∑CI COCLKC1<1DQ 'Qia ic i-1c ib is 串行加法器电路二、时序电路的功能描述原状态:q1, q2, …, q l新状态:q1*,q2 *,…,q l*1.逻辑表达式。

Y = F [X,Q] 输出方程。

Z = G [X,Q] 驱动方程(或激励方程)。

Q* = H [Z,Q] 状态方程。

2.状态表、状态图和时序图。

三、时序电路的分类1. 按逻辑功能划分有:计数器、寄存器、移位寄存器、读/写存储器、顺序脉冲发生器等。

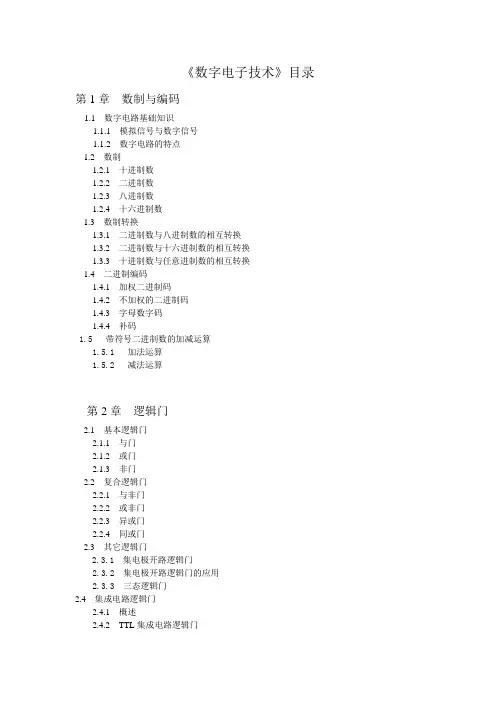

《数字电子技术》目录第1章数制与编码1.1 数字电路基础知识1.1.1 模拟信号与数字信号1.1.2 数字电路的特点1.2 数制1.2.1 十进制数1.2.2 二进制数1.2.3 八进制数1.2.4 十六进制数1.3 数制转换1.3.1 二进制数与八进制数的相互转换1.3.2 二进制数与十六进制数的相互转换1.3.3 十进制数与任意进制数的相互转换1.4 二进制编码1.4.1 加权二进制码1.4.2 不加权的二进制码1.4.3 字母数字码1.4.4 补码1.5带符号二进制数的加减运算1.5.1 加法运算1.5.2 减法运算第2章逻辑门2.1 基本逻辑门2.1.1 与门2.1.2 或门2.1.3 非门2.2 复合逻辑门2.2.1 与非门2.2.2 或非门2.2.3 异或门2.2.4 同或门2.3 其它逻辑门2.3.1 集电极开路逻辑门2.3.2 集电极开路逻辑门的应用2.3.3 三态逻辑门2.4 集成电路逻辑门2.4.1 概述2.4.2 TTL集成电路逻辑门2.4.3 CMOS集成电路逻辑门2.4.4 集成逻辑门的性能参数2.4.5 TTL与CMOS集成电路的接口*第3章逻辑代数基础3.1 概述3.1.1 逻辑函数的基本概念3.1.2 逻辑函数的表示方法3.2 逻辑代数的运算规则3.2.1 逻辑代数的基本定律3.2.2 逻辑代数的基本公式3.2.3 摩根定理3.2.4 逻辑代数的规则3.3 逻辑函数的代数化简法3.3.1 并项化简法3.3.2 吸收化简法3.3.3 配项化简法3.3.4 消去冗余项法3.4 逻辑函数的标准形式3.4.1 最小项与最大项3.4.2 标准与或表达式3.4.3 标准或与表达式3.4.4 两种标准形式的相互转换3.4.5 逻辑函数表达式与真值表的相互转换3.5 逻辑函数的卡诺图化简法3.5.1 卡诺图3.5.2 与或表达式的卡诺图表示3.5.3 与或表达式的卡诺图化简3.5.4 或与表达式的卡诺图化简3.5.5 含无关项逻辑函数的卡诺图化简3.5.6 多输出逻辑函数的化简*第4章组合逻辑电路4.1 组合逻辑电路的分析4.1.1 组合逻辑电路的定义4.1.2 组合逻辑电路的分析步骤4.1.3 组合逻辑电路的分析举例4.2 组合逻辑电路的设计4.2.1 组合逻辑电路的一般设计步骤4.2.2 组合逻辑电路的设计举例4.3 编码器4.3.1 编码器的概念4.3.2 二进制编码器4.3.3 二-十进制编码器4.3.4 编码器应用举例4.4 译码器4.4.1 译码器的概念4.4.2 二进制译码器4.4.3 二-十进制译码器4.4.4 用译码器实现逻辑函数4.4.5 显示译码器4.4.6 译码器应用举例4.5 数据选择器与数据分配器4.5.1 数据选择器4.5.2 用数据选择器实现逻辑函数4.5.3 数据分配器4.5.4 数据选择器应用举例4.6 加法器4.6.1 半加器4.6.2 全加器4.6.3 多位加法器4.6.4 加法器应用举例4.6.5 加法器构成减法运算电路*4.7 比较器4.7.1 1位数值比较器4.7.2 集成数值比较器4.7.3 集成数值比较器应用举例4.8 码组转换电路4.8.1 BCD码之间的相互转换4.8.2 BCD码与二进制码之间的相互转换4.8.3 格雷码与二进制码之间的相互转换4.9 组合逻辑电路的竞争与冒险4.9.1 冒险现象的识别4.9.2 消除冒险现象的方法第5章触发器5.1 RS触发器5.1.1 基本RS触发器5.1.2 钟控RS触发器5.1.3 RS触发器应用举例5.2 D触发器5.2.1 电平触发D触发器5.2.2 边沿D触发器5.3 JK触发器5.3.1 主从JK触发器5.3.2 边沿JK触发器5.4 不同类型触发器的相互转换5.4.1 概述5.4.2 D触发器转换为JK、T和T'触发器5.4.3 JK触发器转换为D触发器第6章寄存器与计数器6.1 寄存器与移位寄存器6.1.1 寄存器6.1.2 移位寄存器6.1.3移位寄存器应用举例6.2 异步N进制计数器6.2.1 异步n位二进制计数器6.2.2 异步非二进制计数器6.3 同步N进制计数器6.3.1 同步n位二进制计数器6.3.2 同步非二进制计数器6.4 集成计数器6.4.1 集成同步二进制计数器6.4.2 集成同步非二进制计数器6.4.3 集成异步二进制计数器6.4.4 集成异步非二进制计数器6.4.5 集成计数器的扩展6.4.6 集成计数器应用举例第7章时序逻辑电路的分析与设计7.1 概述7.1.1 时序逻辑电路的定义7.1.2 时序逻辑电路的结构7.1.3 时序逻辑电路的分类7.2 时序逻辑电路的分析7.2.1时序逻辑电路的分析步骤7.2.2 同步时序逻辑电路分析举例7.2.3 异步时序逻辑电路分析举例7.3 同步时序逻辑电路的设计7.3.1 同步时序逻辑电路的基本设计步骤7.3.2 同步时序逻辑电路设计举例第8章存储器与可编程器件8.1 存储器概述8.1.1 存储器的分类8.1.2 存储器的相关概念8.1.3 存储器的性能指标8.2 RAM8.2.1 RAM分类与结构8.2.2 SRAM8.2.3 DRAM8.3 ROM8.3.1 ROM分类与结构8.3.2 掩膜ROM8.3.3 可编程ROM8.3.4 可编程ROM的应用8.4 快闪存储器(Flash Memory)8.4.1 快闪存储器的电路结构8.4.2 闪存与其它存储器的比较8.5 存储器的扩展8.5.1 存储器的位扩展法8.5.2 存储器的字扩展法8.6 可编程阵列逻辑8.6.1 PAL的电路结构8.6.2 PAL器件举例8.6.3 PAL器件的应用8.7 通用阵列逻辑8.7.1 GAL的性能特点8.7.2 GAL的电路结构8.7.3 OLMC8.7.4 GAL器件的编程与开发8.8 CPLD、FPGA和在系统编程技术8.8.1 数字可编程器件的发展概况8.8.2数字可编程器件的编程语言8.8.3数字可编程器件的应用实例第9章D/A转换器和A/D转换器9.1 概述9.2 D/A转换器9.2.1 D/A转换器的电路结构9.2.2 二进制权电阻网络D/A转换器9.2.3 倒T型电阻网络D/A转换器9.2.4 D/A转换器的主要技术参数9.2.5 集成D/A转换器及应用举例9.3 A/D转换器9.3.1 A/D转换的一般步骤9.3.2 A/D转换器的种类9.3.3 A/D转换器的主要技术参数9.3.4 集成A/D转换器及应用举例第10章脉冲波形的产生与整形电路10.1 概述10.2 多谐振荡器10.2.1 门电路构成的多谐振荡器10.2.2 采用石英晶体的多谐振荡器10.3 单稳态触发器10.3.1 门电路构成的单稳态触发器10.3.2 集成单稳态触发器10.3.3 单稳态触发器的应用10.4 施密特触发器10.4.1 概述10.4.2 施密特触发器的应用10.5 555定时器及其应用10.5.1 电路组成及工作原理10.5.2 555定时器构成施密特触发器10.5.3 555定时器构成单稳态触发器10.5.4 555定时器构成多谐振荡器第11章数字集成电路简介11.1 TTL门电路11.1.1 TTL与非门电路11.1.2 TTL或非门电路11.1.3 TTL与或非门电路11.1.4 集电极开路门电路与三态门电路11.1.5 肖特基TTL与非门电路11.2 CMOS门电路11.2.1 概述11.2.2 CMOS非门电路11.2.3 CMOS与非门电路11.2.4 CMOS或非门电路11.2.5 CMOS门电路的构成规则11.3 数字集成电路的使用。

《单片机原理及接口技术》(第2版)人民邮电出版社第6章定时器/计数器思考题及习题61.下列哪些说法是正确的。

A.特殊功能寄存器SCON,与定时器/计数器的控制无关。

对B.特殊功能寄存器TCON,与定时器/计数器的控制无关。

错C.特殊功能寄存器IE,与定时器/计数器的控制无关。

错D.特殊功能寄存器TMOD,与定时器/计数器的控制无关。

错2.如果采用的晶振的频率为3MHz,定时器/计数器工作在方式0、1、2下,其最大定时时间各为多少?答:定时器/计数器工作方式0下,其最大定时时间为TMAX =8.192mS方式1下的最大定时时间为262.144ms;方式2下的最大定时时间为1024ms。

3.定时器/计数器用作定时器模式时,其计数脉冲由谁提供?定时时间与哪些因素有关?答:定时/计数器作定时时,其计数脉冲由系统振荡器产生的内部时钟信号12分频后提供。

定时时间与时钟频率和定时初值有关。

4.定时器/计数器用作计数器模式时,对外界计数频率有何限制?答:由于确认1次负跳变要花2个机器周期,即24个振荡周期,因此外部输入的计数脉冲的最高频率为系统振荡器频率的1/24。

5.采用定时器/计数器T0对外部脉冲进行计数,每计数100个脉冲后,T0转为定时工作方式。

定时1ms后,又转为计数工作方式,如此循环不止。

假定AT89S51单片机的晶体振荡器的频率为5MHz,请使用方式1实现,要求编写程序。

答:定时器/计数器T0在计数和定时工作完成后,均采用中断方式工作。

除了第一次计数工作方式设置在主程序完成外,后面的定时或计数工作方式分别在中断程序完成,用一标志位识别下一轮定时器/计数器T0的工作方式。

参考程序如下:ORG 0000HLJMP MAINORG 000BHLJMP IT0PMAIN: MOV TMOD,#06H ;定时器/计数器T0为计数方式2MOV TL0,#156 ;计数100个脉冲的初值赋值MOV TH0,#156SETB GATE ;打开计数门SETB TR0 ;启动T0,开始计数SETB ET0 ;允许T0中断SETB EA ;CPU开中断CLR F0 ;设置下一轮为定时方式的标志位WAIT: AJMP WAITIT0P: CLR EA ;CPU关中断JB F0,COUNT ;F0=1,转计数方式设置MOV TMOD,#00H ;定时器/计数器T0为定时方式0MOV TH0,#0FEH ;定时1ms初值赋值MOV TL0,#0CHSETB EARETICOUNT: MOV TMOD,#06HMOV TL0,#156SETB EARETI6.定时器/计数器的工作方式2有什么特点?适用于哪些应用场合?答:定时器/计数器的工作方式2具有自动恢复初值的特点,适用于精确定时,比如波特率的产生。