五段指令流水线kppt

- 格式:ppt

- 大小:401.00 KB

- 文档页数:7

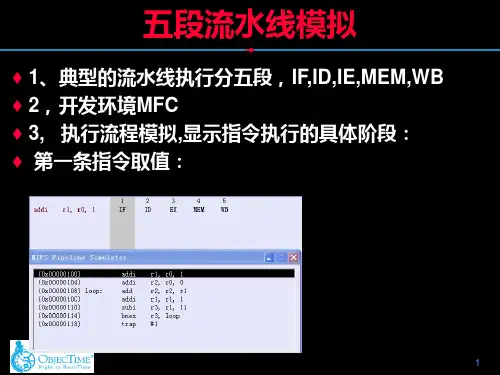

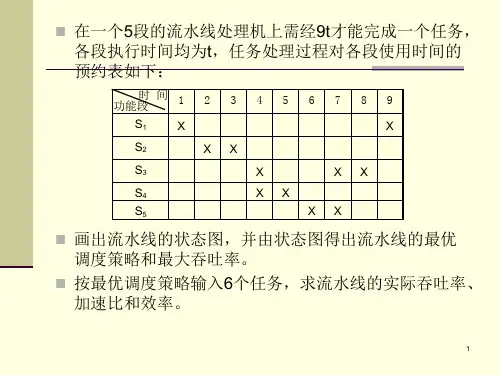

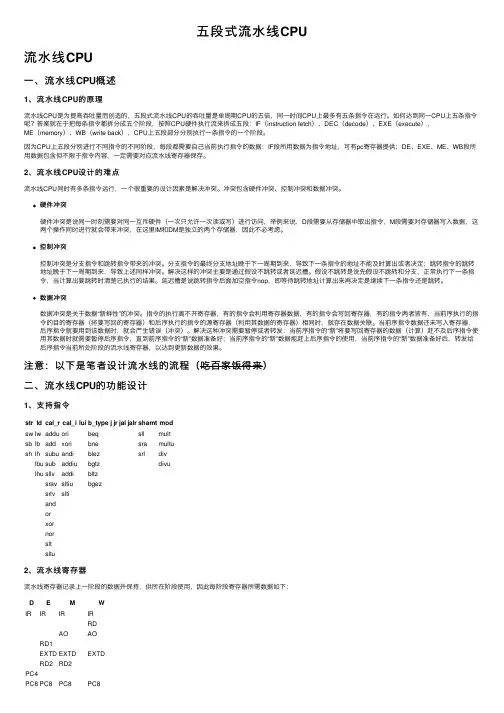

五段式流⽔线CPU流⽔线CPU⼀、流⽔线CPU概述1、流⽔线CPU的原理流⽔线CPU是为提⾼吞吐量⽽创造的,五段式流⽔线CPU的吞吐量是单周期CPU的五倍,同⼀时间CPU上最多有五条指令在运⾏。

如何达到同⼀CPU上五条指令呢?答案就在于把每条指令都拆分成五个阶段,按照CPU硬件执⾏流来拆成五段:IF(instruction fetch)、DEC(decode)、EXE(execute)、ME(memory)、WB(write back),CPU上五段部分分别执⾏⼀条指令的⼀个阶段。

因为CPU上五段分别进⾏不同指令的不同阶段,每段都需要⾃⼰当前执⾏指令的数据:IF段所⽤数据为指令地址,可有pc寄存器提供;DE、EXE、ME、WB段所⽤数据包含但不限于指令内容,⼀定需要对应流⽔线寄存器保存。

2、流⽔线CPU设计的难点流⽔线CPU同时有多条指令运⾏,⼀个很重要的设计因素是解决冲突。

冲突包含硬件冲突、控制冲突和数据冲突。

硬件冲突硬件冲突是说同⼀时刻需要对同⼀互斥硬件(⼀次只允许⼀次读或写)进⾏访问,举例来说,D段需要从存储器中取出指令,M段需要对存储器写⼊数据,这两个操作同时进⾏就会带来冲突,在这⾥IM和DM是独⽴的两个存储器,因此不必考虑。

控制冲突控制冲突是分⽀指令和跳转指令带来的冲突。

分⽀指令的最终分⽀地址晚于下⼀周期到来,导致下⼀条指令的地址不能及时算出或者决定;跳转指令的跳转地址晚于下⼀周期到来,导致上述同样冲突。

解决这样的冲突主要是通过假设不跳转或者延迟槽。

假设不跳转是说先假设不跳转和分⽀,正常执⾏下⼀条指令,当计算出要跳转时清楚已执⾏的结果。

延迟槽是说跳转指令后⾯加空指令nop,即等待跳转地址计算出来再决定是继续下⼀条指令还是跳转。

数据冲突数据冲突是关于数据“新鲜性”的冲突。

指令的执⾏离不开寄存器,有的指令会利⽤寄存器数据,有的指令会写回寄存器,有的指令两者皆有,当前序执⾏的指令的⽬的寄存器(将要写回的寄存器)和后序执⾏的指令的源寄存器(利⽤其数据的寄存器)相同时,就存在数据关联。