东北大学电子实验三基本门电路及触发器(终审稿)

- 格式:docx

- 大小:1011.82 KB

- 文档页数:7

基本门电路逻辑功能的测试数电实验报告实验目的

本次实验的主要目的是熟悉基本门电路,明确基本门的功能,直接运用电路仿真软件ISIS Proteus完成电路的搭建,使基本门的功能得到验证。

实验原理

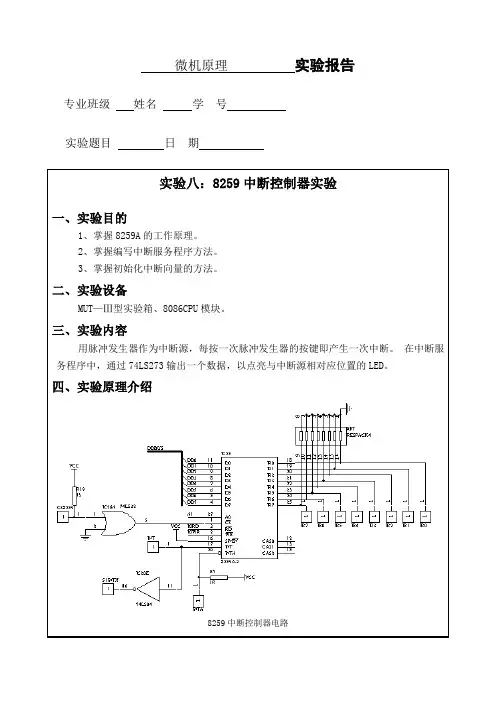

选定的实验装置电路示意图如下所示,是一实用OR门电路,要求A及B两端输入电平均为低电平时,Y输出端为低电平,而当A或B中有一端输入为高电平时,Y输出端为高电平,可实现OR门的功能。

实验装置

本次实验中,我们利用ISIS Proteus软件实现OR门电路的搭建。

实验装置的简单搭建过程如下:

1.首先,打开ISIS Proteus软件,进入典型电路组态视图。

2.然后,将所需的元件从Targets文件夹中拖入图纸,包括OR门、LED指示灯及拨码开关3个元件,并按照题目要求连接电路。

3.最后,以数据为基础运行仿真,通过实时变化模拟波形以及LED发光情况,验证OR 门电路的功能。

实验01基本逻辑门电路实验第一篇:实验01 基本逻辑门电路实验实验一基本逻辑门实验(1)一、实验目的1、通过实验学习掌握Quartus II软件的基本操作流程。

2、通过实验理解全加器电路的设计方法,并掌握在Quartus II软件中通过绘制电路图的形式进行芯片设计的过程。

3、学习Quartus II软件的“仿真”功能。

二、实验步骤1、在“我的电脑”中新建一个目录。

(注意:目录尽量建立在自带的U盘上,以防实验工程被还原)2、打开QuartusII软件,点击菜单中的“File->New Project Wizard”选项,启动新建工程向导程序,新建一个Quartus II工程。

工程文件保存在第1步创建的目录中,工程命名为:“Exp01”。

图1 新建工程向导启动图2 向导开始直接点击“Next”按钮图3 向导第1步,设置工程的路径和工程名向导第2步的设置是向新建工程中导入已经存在的设计文件,这里不用导入所以直接点击“Next”按钮跳过这一步。

向导第3步选择FPGA芯片,这里要按照实验箱上的芯片型号选择:Family选择“Cyclone II”,Available devices选择“EP2C5T144C8”,其它地方保持默认选择。

图4 向导第3步设置工程用芯片向导程序第4、5步不用做设置,直接点击完成按钮就可以完成工程的建立了。

图5 工程建立完成,Project Navigator出现工程列表3、点击菜单“File->New”选项,打开新建文件窗口,选择“Design Files->Block Diagram/Schematic File”,再点击“OK”按钮,创建一个电路图设计文件。

图6 新建文件窗口4、点击菜单“File->Save As”选项,将新建的电路图设计文件保存在工程目录中,注意:文件名要与工程名保持一致:Exp01.bdf。

图7 新建文件保存图8 文件名与工程名保持一致5、点击设计文件窗口上的“Symbol T ool”工具按钮,如图所示:中输入“xor”异或门,单击“OK”按钮。

东北大学考试《电子电路设计技术Ⅱ》考

核作业参考703

介绍

本文档提供了东北大学考试《电子电路设计技术Ⅱ》考核作业参考703的内容。

该考核作业涉及电子电路设计技术的相关知识和技能。

考核要求

参考703的考核作业要求学生展示他们在电子电路设计技术方面的理解和实践能力。

考核内容包括以下几个方面:

1. 电路分析与设计:要求学生能够进行电路的分析和设计,包括对电路参数的计算和设定等。

2. 电路元件与器件:要求学生掌握各种电路元件和器件的特性和应用,包括二极管、晶体管、集成电路等。

3. 电路模拟与仿真:要求学生能够使用模拟工具进行电路的仿真和性能分析。

4. PCB设计与制作:要求学生能够进行PCB布局和制作,包括选择合适的设计软件和处理器件。

考核建议

以下是对参考703的考核作业的建议,帮助学生更好地完成作业:

1. 研究理论知识:深入研究与电子电路设计技术相关的理论知识,了解电子元器件的基本原理和特性。

2. 实践操作:通过实践设计和制作电子电路,提高自己的实际操作能力。

3. 多做题目:多做相关题目,加深对电子电路设计技术的理解和应用。

4. 寻求帮助:在遇到问题时,及时寻求同学、老师或其他专业人士的帮助和指导。

总结

东北大学考试《电子电路设计技术Ⅱ》考核作业参考703要求学生展示电子电路设计技术方面的知识和技能。

通过深入学习和实践,学生可以更好地完成这份考核作业,并提高自己在电子电路设计技术方面的能力。

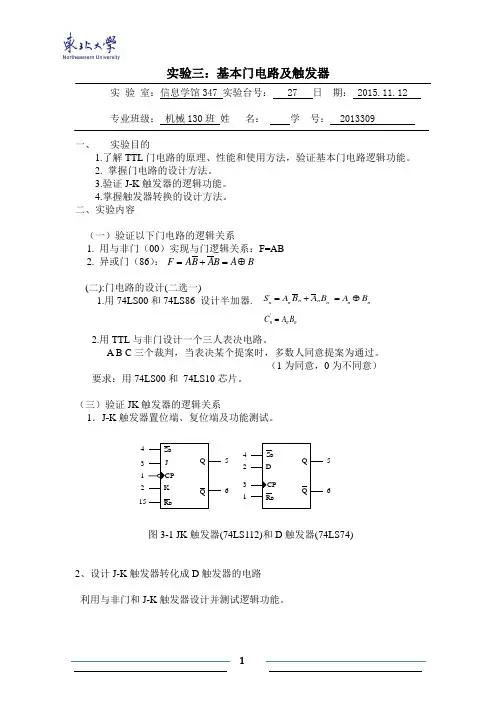

43121556423156实验三:基本门电路及触发器实 验 室:信息学馆347 实验台号: 27 日 期: 2015.11.12专业班级: 机械130班 姓 名: 学 号: 2013309一、 实验目的1.了解TTL 门电路的原理、性能和使用方法,验证基本门电路逻辑功能。

2. 掌握门电路的设计方法。

3.验证J-K 触发器的逻辑功能。

4.掌握触发器转换的设计方法。

二、实验内容(一)验证以下门电路的逻辑关系1. 用与非门(00)实现与门逻辑关系:F=AB2. 异或门(86):(二):门电路的设计(二选一)1.用74LS00和74LS86 设计半加器.2.用TTL 与非门设计一个三人表决电路。

A B C 三个裁判,当表决某个提案时,多数人同意提案为通过。

(1为同意,0为不同意) 要求:用74LS00和 74LS10芯片。

(三)验证JK 触发器的逻辑关系1.J-K 触发器置位端、复位端及功能测试。

图3-1 JK 触发器(74LS112)和D 触发器(74LS74)2、设计J-K 触发器转化成D 触发器的电路利用与非门和J-K 触发器设计并测试逻辑功能。

B A B A B A F ⊕=+=n n n n n n n B A B A B A S ⊕=+='nn n B A C ='AB F三、实验原理图图3-2与门电路 图3-3异或门电路图3-4半加器四、实验结果及数据处理1. 直接在实验原理图上标记芯片的引脚。

2. 写出实验结果。

(1)与门、异或门实验结果表(用数字万用表测量高低电平1、0的电压值。

)=1AB F(2)半加器实验结果(3) 表决电路结果(4)表决电路图(可以拍照图):(5)J-K 触发器的功能测试(6)设计J-K触发器转化成D触发器的电路(可以拍照图),验证电路的正确性。

五、思考题1.实验用的与非门和或门中不用的输入端如何处理?答:实验用的与非门中不用的输入端长接高电位“1”端处理。

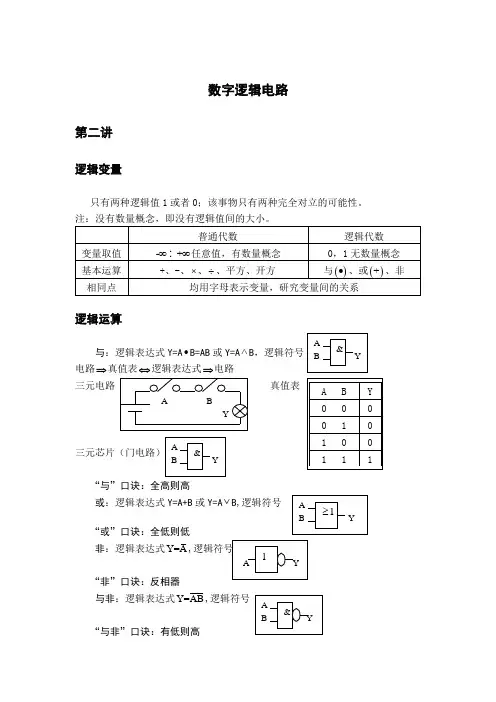

数字逻辑电路第二讲逻辑变量只有两种逻辑值1或者0;该事物只有两种完全对立的可能性。

注:没有数量概念,即没有逻辑值间的大小。

逻辑运算与:逻辑表达式Y=A ∙B=AB 或Y=A ∧B ,逻辑符号电路⇒真值表⇔逻辑表达式⇒电路三元电路真值表“与”口诀:全高则高或:逻辑表达式Y=A+B 或Y=A ∨B ,逻辑符号“或”口诀:全低则低非:逻辑表达式Y=A ,“非”口诀:反相器与非:逻辑表达式Y=AB ,逻辑符号“与非”口诀:有低则高或非:逻辑表达式Y=A+B“或非”口诀:有高则低 与或非:逻辑表达式Y=AB+CD“与或非”口诀:有门电路高则低 异或:逻辑表达式Y=A B=AB+AB ⊕,逻辑符号或“异或”口诀:不同则高例:Y =A B C ⊕⊕可转化为A 1=A ⊕ A 0=A⊕ A A =0⊕ A A=1⊕同或:(没有专门的同或门,是异或非门)逻辑表达式Y=A B=AB+A B ⊕,逻辑符号或“同或”口诀:相同则高 优先级:非、与、或;对“与非”化简需加括号。

逻辑代数的基本公式和常用公式0 1律:0+A=A 1A=A ∙ 1+A=1 0A=0∙ 重叠律:A +A =A A A=A ∙ 互补律:A+A =1 A A =0∙ 交换律:A+B=B+A A B=B A ∙∙ 结合律:()()A+B+C =A+B +C ()()A B C =A B C ∙∙∙∙ 分配率:()A B+C =A B+A C ∙∙∙ ()()A+B C=A+B A+C ∙∙ 反演律:A+B=A B ∙ A B=A +B ∙ 否定律:A =A 吸收定理:A+AB=A A+AB=A+B AB+A B=A 摩根定理:(反演律)A+B=A B ∙ A B=A +B ∙ 利用互补律证明:设X =A+B ,Y=A B ∙ 则()()()X +Y =A+B +A B =A+B+A =1∙, ()()X Y =A+B A B =A A B +B A B =0∙∙∙∙∙故X 与Y 互补,即X=Y A+B=A B ⇒∙ 同理可证:A B=A +B ∙。

实验名称:数字电路基础实验实验日期:2023年X月X日实验地点:XX实验室实验指导教师:XXX实验目的:1. 理解数字电路的基本组成和基本逻辑门的工作原理。

2. 掌握常用数字电路的分析方法和设计方法。

3. 培养动手能力和实验操作技能。

实验原理:数字电路是电子技术中的重要组成部分,它利用数字信号进行信息的传输和处理。

本实验主要涉及以下内容:1. 逻辑门:与门、或门、非门、异或门等。

2. 编码器、译码器、数据选择器等组合逻辑电路。

3. 移位寄存器、计数器等时序逻辑电路。

实验器材:1. 数字电路实验箱2. 实验用电路板3. 逻辑门芯片4. 电源、示波器、数字万用表等实验内容:一、逻辑门实验1. 实验目的:掌握逻辑门的工作原理和基本操作。

2. 实验步骤:(1)搭建与门、或门、非门、异或门等逻辑门电路。

(2)用示波器观察输入信号和输出信号,验证逻辑门的功能。

(3)分析实验现象,总结逻辑门的工作原理。

二、编码器实验1. 实验目的:掌握编码器的工作原理和基本操作。

2. 实验步骤:(1)搭建编码器电路,包括8-3线优先编码器。

(2)用示波器观察输入信号和输出信号,验证编码器功能。

(3)分析实验现象,总结编码器的工作原理。

三、译码器实验1. 实验目的:掌握译码器的工作原理和基本操作。

2. 实验步骤:(1)搭建译码器电路,包括2-4线译码器。

(2)用示波器观察输入信号和输出信号,验证译码器功能。

(3)分析实验现象,总结译码器的工作原理。

四、数据选择器实验1. 实验目的:掌握数据选择器的工作原理和基本操作。

2. 实验步骤:(1)搭建数据选择器电路,包括4选1数据选择器。

(2)用示波器观察输入信号和输出信号,验证数据选择器功能。

(3)分析实验现象,总结数据选择器的工作原理。

五、移位寄存器实验1. 实验目的:掌握移位寄存器的工作原理和基本操作。

2. 实验步骤:(1)搭建移位寄存器电路,包括串行进位移位寄存器。

(2)用示波器观察输入信号和输出信号,验证移位寄存器功能。

东北大学电子实验三基本门电路及触发器

公司内部档案编码:[OPPTR-OPPT28-OPPTL98-OPPNN08]

实验三:基本门电路及触发器

实 验 室:信息学馆347 实验台号: 27 日 期:

专业班级: 机械130班 姓 名: 学 号: 2013309

一、 实验目的

1.了解TTL 门电路的原理、性能和使用方法,验证基本门电路逻辑功能。

2. 掌握门电路的设计方法。

3.验证J-K 触发器的逻辑功能。

4.掌握触发器转换的设计方法。

二、实验内容

(一)验证以下门电路的逻辑关系

1. 用与非门(00)实现与门逻辑关系:F=AB

2. 异或门(86):

(二):门电路的设计(二选一)

1.用74LS00和74LS86 设计半加器.

2.用TTL 与非门设计一个三人表决电路。

A B C 三个裁判,当表决某个提案时,多数人同意提案为通过。

(1为同意,0为不同意) 要求:用74LS00和 74LS10芯片。

B

A B A B A F ⊕=+=n

n n n n n n B A B A B A S ⊕=+='n

n n B A C ='

&A B

&

F

J CP K S D R D

Q

Q

S D R D

D CP Q Q 431215

5

6

42315

6

(三)验证JK 触发器的逻辑关系

1.J-K 触发器置位端、复位端及功能测试。

图3-1 JK 触发器(74LS112)和D 触发器(74LS74)

2、设计J-K 触发器转化成D 触发器的电路

利用与非门和J-K 触发器设计并测试逻辑功能。

三、实验原理图

图3-2与门电路 图3-3异或门电路

图3-4半加器

四、实验结果及数据处理

1.

直接在实验原理图上标记芯片的引脚。

=1

A B

F

2.

写出实验结果。

(1)与门、异或门实验结果表(用数字万用表测量高低电平1、0的电压值。

)

输入 与门 异或门

A B F Uo (V )

F 0 0 0

0 0 1 0

1 1 0 0

1 1

1

1 0

(2)半加器实验结果

(3) 表决电路结果

An Bn n S '

n

C ' 0 0 0 1 1 0 1

1

(4)表决电路图(可以拍照图):

(5)J-K 触发器的功能测试

输入端

输出原态

输出次态 D R -

D S -

J K Q n Q n+1 0 1 * * * 1 1

*

*

*

A B C F 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1

1

1

1

110000

110100

111001

111101

110011

110110

111011

111110

(6)设计J-K触发器转化成D触发器的电路(可以拍照图),验证电路的正确性。

五、思考题

1.实验用的与非门和或门中不用的输入端如何处理

答:实验用的与非门中不用的输入端长接高电位“1”端处理。

或门中不用的输入端长接高电位“0”端处理。

2.如果与非门的一个输入端接时钟,其余输入端应是什么状态时才允许脉冲通过

答:如果与非门的一个输入端接时钟,其余输入端应是1状态时才允许脉冲通过。

3.J-K触发器Qn=0时,如果时钟脉冲CP到来后,触发器处于“1”态,J-K两端应预先分别是什么状态

答:J、K端都置1;或J置1,K置0 皆可时钟脉冲CP到来后,触发器处于“1”态。

4.J-K触发器与D触发器的触发边沿有何不同

答:J-K触发器由脉冲下降沿(10)触发,D触发器由脉冲上升沿(01)触发。