以太网物理层器件

- 格式:pdf

- 大小:563.79 KB

- 文档页数:12

以太网原理MAC和PHY以太网是一种局域网(LAN)技术,用于在计算机之间传输数据。

以太网原理包括物理层(PHY)和媒体访问控制层(MAC)两个部分。

物理层(PHY)是以太网技术的底层,负责将传输的数据转化为电信号,并在网络中传输和接收数据。

PHY负责处理传输介质、传输速率等物理层面的细节。

MAC层是以太网技术的上层,负责管理和控制网络中的通信。

MAC层协议定义了数据的传输方式、帧结构、帧格式等规范,以确保数据的可靠传输和有效利用。

在以太网中,数据被分割成一系列的帧(Frame),每个帧由MAC层添加标识符和校验码,并传输到物理层。

物理层将数据转化成电信号,并通过传输介质(如双绞线、光纤等)传输到目标计算机。

PHY层通过一系列的电器和电子设备来处理数据的传输。

这些设备包括编码器、解码器、物理传输媒介、放大器等。

编码器和解码器负责将数据转化为电信号和相反的操作,物理传输媒介负责在不同的介质中传输数据,放大器用于增强信号的强度。

当数据传输到目标计算机后,物理层将电信号转化为数据,并传递给MAC层处理。

MAC层根据帧的标识符和校验码来验证数据的完整性和正确性,并将其传递给上层应用程序。

MAC层还负责管理和控制网络中的通信。

为了避免数据冲突,以太网采用了一种称为“载波侦听多址接入/碰撞检测”(Carrier Sense Multiple Access/Collision Detection,CSMA/CD)的协议。

该协议允许多个计算机同时发送数据,但如果检测到冲突,则发送方会停止发送,等待一段随机时间后重新发送。

以太网的传输速率通常用Mbps(兆位每秒)来衡量,常见的速率有10Mbps、100Mbps和1000Mbps(即千兆以太网,也被称为千兆网)。

总结起来,以太网的原理包括物理层(PHY)和媒体访问控制层(MAC)两个部分。

PHY层负责将数据转化为电信号,并在物理介质上传输和接收数据。

MAC层负责管理和控制网络中的通信,确保数据的可靠传输和有效利用。

以太网知识讲座()——物理层器件以太网知识讲座(3)——物理层器件2010-05-2513:24(天津光电通信产业集团恒光科技有限公司;天津300211)摘要:系统地介绍了以太网的基本要领介质接入控制和物理层标准规范,以太网信号的帧结构、网络硬件设备、网络组成及主要性能,以及以太网信号在PDH、SDH/SONET中的传输等等。

由于以太网中的各种设备必需通物理层接口器件才能与网络传输介质相连,因此本部分主要介绍物理层器件。

关键词:以太网;物理层;接口1物理层器件物理层器件(PHY:Physical Layer Interface Devices)是将各网元连接到物理介质上的关键部件。

负责完成互连参考模型(OSI)第I层中的功能,即为链路层实体之间进行bit传输提供物理连接所需的机械、电气、光电转换和规程手段。

其功能包括建立、维护和拆除物理电路,实现物理层比特(bit)流的透明传输等。

通常物理层的功能均被集成在一个芯片之中,但有的芯片也将部分链路层的功能集成进来,如物理介质接入控制(MAC:Media Access Con-brol)子层的功能等。

其MAC/Repeater接口在10Mbit/s、100Mbit/s两种速率下有10/100MII、100M符号、10M串行和链路脉冲几种模式。

1.1PHY的结构如图1所示,物理层包括四个功能层和两上层接口。

两个层接口为物理介质无关层接口(MII)和物理介质相关层接口(MDI),在MII的上层是逻辑数据链路层(DLL),而MDI的下层则直接与传输介质相连。

以下对四个功能层和两个层接口分别进行介绍。

1.2MIIMII满足ISO/IEC8802-3和IEEE802.3标准的要求,支持以太网数据传输的速率为10Mbit/s,100Mbit/s、1000Mbit/s和10Gbit/s,有对应的运行时钟。

MII接口主要由与链路层之间的端口(MAC-PHY)和与站管理实体(STA:Station Management Entity)之间的端口(STA-PHY)两部分组成。

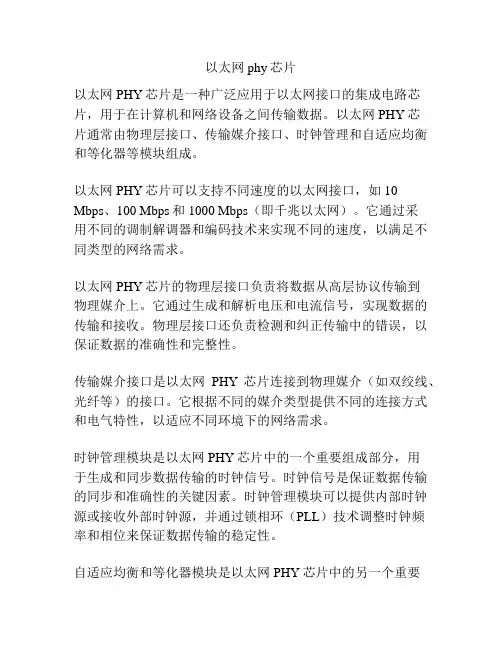

以太网phy芯片以太网PHY芯片是一种广泛应用于以太网接口的集成电路芯片,用于在计算机和网络设备之间传输数据。

以太网PHY芯片通常由物理层接口、传输媒介接口、时钟管理和自适应均衡和等化器等模块组成。

以太网PHY芯片可以支持不同速度的以太网接口,如10 Mbps、100 Mbps和1000 Mbps(即千兆以太网)。

它通过采用不同的调制解调器和编码技术来实现不同的速度,以满足不同类型的网络需求。

以太网PHY芯片的物理层接口负责将数据从高层协议传输到物理媒介上。

它通过生成和解析电压和电流信号,实现数据的传输和接收。

物理层接口还负责检测和纠正传输中的错误,以保证数据的准确性和完整性。

传输媒介接口是以太网PHY芯片连接到物理媒介(如双绞线、光纤等)的接口。

它根据不同的媒介类型提供不同的连接方式和电气特性,以适应不同环境下的网络需求。

时钟管理模块是以太网PHY芯片中的一个重要组成部分,用于生成和同步数据传输的时钟信号。

时钟信号是保证数据传输的同步和准确性的关键因素。

时钟管理模块可以提供内部时钟源或接收外部时钟源,并通过锁相环(PLL)技术调整时钟频率和相位来保证数据传输的稳定性。

自适应均衡和等化器模块是以太网PHY芯片中的另一个重要组成部分,用于对传输中的信号进行均衡和补偿,以减小信号损失和抖动,提高数据传输的可靠性。

自适应均衡和等化器模块根据接收到的信号特性自动调整均衡和补偿参数,以适应不同长度和质量的传输线路。

除了上述基本模块,以太网PHY芯片还可以包含一些其他功能,如电源管理、噪声抑制、故障检测和诊断等。

这些功能可以提供更高级的性能和功能,以满足不同网络设备的需求。

总的来说,以太网PHY芯片是一种集成电路芯片,用于实现不同速度和不同介质的以太网接口。

它通过物理层接口、传输媒介接口、时钟管理和自适应均衡和等化器等模块实现数据的传输和接收,以及网络的连接和管理。

随着以太网技术的发展和应用范围的扩大,以太网PHY芯片的功能和性能将会进一步提升,以满足不断变化的网络需求。

2024年以太网物理层芯片市场分析现状一、引言以太网物理层芯片是计算机网络中的重要组成部分,负责将数字信号转换为模拟信号,在计算机与网络设备之间传输数据。

以太网物理层芯片市场在近年来迅速发展,随着5G技术的普及和物联网的快速发展,预计在未来几年内将继续保持高速增长。

本文将对目前以太网物理层芯片市场的现状进行分析。

二、市场规模和潜力以太网物理层芯片市场在全球范围内已经形成了较大的规模,据市场调研公司数据显示,截至2020年末,全球以太网物理层芯片市场规模约为100亿美元,并且预计在2025年将达到200亿美元。

这一市场规模的增长主要受益于以下几个方面的因素:1.5G技术的普及:5G技术的广泛应用将直接带动以太网物理层芯片的需求增长。

由于5G网络的高速传输和低延迟需求,传统的以太网物理层芯片需要升级,以满足对更高性能和更低功耗的要求。

2.物联网的快速发展:物联网作为未来信息技术的重要趋势,将需要大量的以太网物理层芯片来实现设备之间的连接和通信。

各种智能设备的普及,如智能家居、智能工厂等,都需要以太网物理层芯片的支持。

3.云计算的兴起:云计算技术的兴起使得大量的数据需要在数据中心和云服务之间传输。

以太网物理层芯片在数据中心网络中起着关键作用,需要满足高速传输和低功耗的要求。

三、市场竞争格局目前,以太网物理层芯片市场竞争激烈,主要的竞争厂商包括英特尔、博通、思科等。

这些厂商拥有先进的制造工艺和技术优势,占据着市场的大部分份额。

此外,还有一些中小型芯片供应商在市场中争夺份额,如瑞昱半导体、博科微、迅为通信等。

竞争厂商在技术研发、产品性能和价格等方面展开竞争。

英特尔作为市场的龙头企业,通过自身技术优势和规模效应来保持市场份额的稳定。

博通和思科等企业则通过创新的产品设计和高性能的芯片来争夺份额。

中小型供应商则通过提供廉价的产品和个性化的服务来满足特定需求。

另外,政府的支持和产业政策也在市场竞争中起到重要作用。

以太网物理层芯片时钟同步PLL的设计方案在以太网中,物理层芯片(Physical Layer Interface Devices,PHY)是将各网元连接到物理介质上的关键部件。

负责完成互连参考模型(OSI)第I层中的功能,即为链路层实体之间进行位传输提供物理连接所需的机械、电气、光电转换和规程手段。

其功能包括建立、维护和拆除物理电路,实现物理层比特(bit)流的透明传输等。

物理层包括4个功能层和两个上层接口。

两个上层接口为物理介质无关层接口(MII)和物理介质相关层接口(MDI),在MII的上层是逻辑数据链路层(DLL),而MDI的下层则直接与传输介质相连。

而这些子层的正常工作都离不开一个稳定精确的时钟同步信号。

PLL在物理层芯片的时钟同步应用中,要求其输出时钟带宽覆盖范围广,电压控制频率线性度好,频谱纯度高。

在PLL设计过程中,VCO是最为关键的设计环节,其性能将直接决定PLL的设计工作质量。

近年来,VCO相位噪声得到越来越深入的研究,各种低噪声VCO结构不断涌现,文献中提到的交叉耦合电流饥饿型VCO便是其中一种。

电流饥饿是指电路单元的电流受到电流源的钳制而不能达到其应有的最大值。

本文在其基础上采用了一种有效控制电压变换电路,保证原有电路优点的同时扩展了线性度,提高抗噪声能力,有效降低了相位噪声。

1 VCO延迟单元工作原理图1所示为电流饥饿型VCO中的单级结构。

PNP管M1和NPN管M2是延迟单元的组成部分,Ictrl是用于控制电容的放电电流Id1和充电电流Id2,他们是构成环形振荡器的每一级。

Ictrl控制着流过M1管和M2管的电流,所以由M1管和M2管构成的延迟单元处于电流饥饿状态。

每一级迟单元处于电流饥饿状态。

每一级的电流都由同一个电流源所镜像,所以Id1=Id2同时电流大小由输入控制电流Ictrl控制。

反相延迟主要是2个原因:一个是RC的充电时间;另一个是反相器的预置电压。

而这2个延迟时间的产生都是可以通过调整宽长比来实现。

PHY基本介绍1、PHY基本概念在OSI 的7 层基准模型中我们使用的PHY 属于第一层--物理层( PHY),PHY是数据链路层的媒体访问控制部分和媒体的接口。

PHY 对所有传输的数据,只是进行编码转化,没有对有效数据信号进行任何分析或改变。

但是MAC 所有的数据传输都必须经过PHY 发送和接收才会传输到目标MAC。

PHY 还可以完成连接判断,自动协商以及冲突检测。

MAC 可以通过修改PHY 的寄存器完成对自动协商的监控,当然也可以读取PHY 的寄存器来判断PHY 的状态。

以太网接口类型以太网接口常用有双绞线接口(俗称电口)和光纤接口(俗称光口)2种。

另外还有早期的同轴电缆接口。

电口电口传输距离标准为100m,电口采用RJ-45接口。

图 1-1 RJ-45插座与RJ-45 插座相对应的是RJ-45 插头,如图4所示,一般为8PIN。

在10/100M以太网时,其中2根表示1对发送数据,另2根表示1对接收数据,剩下4根保留(100BASE-T4使用4对线,是为3类线设计的);在1000M以太网时,1000BASE-T使用的是4对双绞线,每一对线都作双向数据传输。

图 1-2 RJ-45插头我们常用的网线有两种:不带交叉网线(MDI)和带交叉网线(MDIX), 现在有些物理层芯片支持MDI和MDIX自动识别功能,具有此功能的PHY能够根据对方的发送和接收信号,决定使用MDI 或者是MDIX。

连接的双方,只要有一方具有Crossover,就可实现功能。

此时双方无论使用正线还是反线都能连接上。

光口目前以太网光模块封装有GBIC、SFF、SFP。

下图为GBIC(Gigabit Interface Converter)封装的光模块,其收发分开,采用SC光纤接头,多模的波长为850nm,单模有1310nm和1550nm,支持热插拔。

图 1-3 GBIC封装光模块下图为SFP(Small Form-factor Pluggable)封装的光模块,其收发分开,采用LC光纤,支持热插拔。

PRELIMINARY DATA SHEETI AC101AC101-DS01-R¥¥¥¥¥16215 Alton Parkway •P .O. Box 57013•Irvine, CA 92619-7013•Phone: 949-450-8700•Fax: 949-450-871006/04/01AC101QF/TF Ultra Low Power 10/100Ethernet TransceiverFigure 1:Functional Block Diagram GENERAL DESCRIPTIONFEATURES The AC101QF/TF is a highly integrated, 3.3V, low power,10BASE-T/100BASE-TX/FX, Ethernet transceiver implement-ed in 0.35 µm CMOS technology. Multiple modes of operation,including normal operation, test mode and power saving mode,are available through either hardware or software control.Features include MAC interfaces, encoder/decoders (EN-DECs), Scrambler/Descrambler, and Auto-Negotiation (ANeg)with support for parallel detection. The transmitter includes adual-speed clock synthesizer that only needs one external clocksource (crystal or clock oscillator). The chip has built-in waveshaping driver circuit for both 10 Mbps and 100 Mbps, eliminat-ing the need for an external hybrid filter. The receiver has anadaptive equalizer/DC restoration circuit for accurate clock anddata recovery for the 100BASE-TX signal. It also provides anon-chip low pass filer/Squelch circuit for the 10BASE-T signal.MAC interfaces to support 10/100 MII, 100M only SymbolMode, 10M only Symbol Mode and 10M only 7 wire interfaceare included.The AC101TF and the AC101QF are the same product in differ-ent packages.•MII MAC connection - 5 Volt tolerant and 2.5 Volt capable •10/100 TX/FX -Full-duplex or half-duplex -FEFI on 100FX •Two packages: 80TQFP and 100PQFP •Industrial temperature: -40°C to +85°C •Very low power – TYP < 280 mW (Total)-Cable Detect mode – TYP < 40 mW (Total)-Power Down mode – TYP < 3.3 mW (T otal)-Selectable TX drivers for 1:1 or 1.25:1 transformers for additional power reduction • 3.3 Volt .35 micron CMOS •Fully compliant with -IEEE 802.3/802.3u -MII •Baseline Wander Compensation •Multi-Function LED outputs •Legacy 10BASE-T 7 wire interface •100M Symbol Mode/10M Symbol Mode •Cable length indicator•Reverse polarity detection and correction with register bitindication – automatic or forced•8 programmable interrupts•Diagnostic registers 10T X 10R X 100R X 100T X 20 M H zC o n tro l/S ta tu s 25 M H z X T L P /N C K IN T E S T [3:0]L ED D riv e rsR XF L P M u x A u to -N e g o tia tio n10B A S E -T P L L C lk G e n T e s t/L E D C o n tro l M II S e ria l M a n a g e m e n tIn te rfa c e a n d R e g is te rs M II D a taIn te rfa c eP H Y A D [4:0]P M A o C lk R e c o v o L in k M o n o S ig n a l De t T P _P M D o M L T -3o B L W o S tre a m M A Co rR IC In te rfa c e P C S o F ra m e r o C a rrie r C ip h e r D e te c t o 4B /5B MII S e ria l M g m tIn te rfa c e T X O P /T X O N R X IP /R X IN F X T P /F X T N F X R P /F X R NRevision HistoryRevision Date Change DescriptionAC101-DS00-R5/22/01Initial release.AC101-DS01-R Changed signal names: FX_DIS, FXRP/FXRN, FXTP/FXTN, RXIP/RX-IN, and TXOP/TXON.Altima Communications, Inc.A Wholly Owned Subsidiary ofBroadcom CorporationP.O. Box 5701316215 Alton ParkwayIrvine, CA 92619-7013© 2001 by Altima Communications, Inc.All rights reservedPrinted in the U.S.A.Broadcom®, the pulse logo, and QAMLink are registered trademarks of Broadcom Corporation and/or its subsidiaries in the United States and certain other countries. All other trademarks are the property of their respective owners.Preliminary Data Sheet I AC101 06/04/01T ABLE OF C ONTENTSSection 1: Functional Description (1)Overview (1)MAC Interface (1)Media Independent Interface (MII) (1)Serial Management Interface (SMI) (1)Interrupts (2)Carrier Sense/RX_DV (2)7-Wire Serial Interface (2)PCS Bypass (3)100 Mbps PCS Bypass (3)10 Mbps PCS Bypass (3)Media Interface (3)10BASE-T Interface (3)Transmit Function (3)Receive Function (3)Link Monitor (3)100BASE-TX Interface (3)Transmit Function (4)Parallel to Serial, NRZ to NRZI, and MLT3 Conversion (4)Receive Function (4)Baseline Wander Compensation (5)Clock/Data Recovery (5)Decoder/De-scrambler (5)Link Monitor (5)100BASE-FX Interface (6)Transmit Function (6)Receive Function (6)Link Monitor (6)Far-End-Fault-Insertion (FEFI) (6)10BASE-T/100BASE-TX/FX Interface (6)Multi-Mode Transmit Driver (6)Adaptive Equalizer (7)BroadcomDocument AC101-DS01-R¥¥¥¥¥Page iiiI AC101Preliminary Data SheetT ABLE OF C ONTENTS06/04/01 PLL Clock Synthesizer (7)Jabber and SQE (Heartbeat) (7)Reverse Polarity Detection and Correction (7)Hardware Configuration (7)Software Configuration (7)LED Outputs (7)Auto-Negotiation (8)Parallel Detection (9)Diagnostics (9)Loopback Operation (9)Cable Length Indicator (9)Reset and Power (10)Clock Input (10)Section 2: Signal Definitions and Pin Assignments (11)Pin Descriptions (11)PHY Address Pins (11)MDI (Media Dependent Interface) Pins (11)MII (Media Independent Interface) 100 PCS Bypass Pins (12)10 Mbps PCS Bypass Pins (13)10 Mbps 7-Wire Interface Pins (13)Special/Test Pins (14)Control and Status Pins (14)LED Indicators Pins (16)Power and Ground Pins (17)No Connect Pins (18)Technology Selections (18)Advanced LED Selections (19)Section 3: Pinout Diagrams (21)AC101QF Pinout Diagram (21)AC101TF Pinout Diagram (22)Section 4: Register Descriptions (23)Register Summary (23)MII-Specified Registers (24)BroadcomPage iv Document AC101-DS01-R¥¥¥¥¥Preliminary Data Sheet I AC101 06/04/01T ABLE OF C ONTENTSRegister 0: Control Register (24)Register 1: Status Register (25)Register 2: PHY Identifier 1 Register (26)Register 3: PHY Identifier 2 Register (26)Register 4: Auto-Negotiation Advertisement Register (26)Register 5: Auto-Negotiation Link Partner Ability Register (27)Register 6: Auto-Negotiation Expansion Register (28)Register 7: Auto-Negotiation Next Page Transmit Register (28)Altima-Specified Registers (29)Register 16: Polarity and Interrupt Level Register (29)Register 17: Interrupt Control/Status Register (30)Register 18: Diagnostic Register (30)Register 19: Power/Loopback Register (31)Register 20: Cable Measurement Register (31)Register 21: Mode Control Register (32)Register 24: Receive Error Counter Register (33)4B/5B Code-Group Table (33)SMI Read/Write Sequence (34)Section 5: Electrical Characteristics (35)Operating Range (35)Total Power Consumption (35)TTL I/O Characteristics (35)REFCLK and XTAL Pin Characteristics (36)I/O Characteristics – LED/CFG Pin Characteristics (36)100BASE-TX Transceiver Characteristics (36)10BASE-T Transceiver Characteristics (37)100BASE-FX Transceiver Characteristics (37)10BASE-T Link Integrity Timing Characteristics (38)Section 6: Timing and AC Characteristics (39)Digital Timing Characteristics (39)Power on Reset Timing (39)Management Data Interface Timing (39)100BASE-TX/FX MII Transmit System Timing (40)100BASE-TX/FX MII Receive System Timing (41)BroadcomDocument AC101-DS01-R¥¥¥¥¥Page vI AC101Preliminary Data SheetT ABLE OF C ONTENTS06/04/01 10BASE-T MII Transmit System Timing (42)10BASE-T MII Receive System Timing (44)10BASE-T 7-Wire Transmit System Timing (45)10BASE-T 7-Wire Receive System Timing (46)10BASE-T 7-Wire Collision Timing (46)Recommended Board Circuitry (47)TX Application Termination (47)FX Application Termination (48)Power and Ground Filtering for AC101QF (49)Power and Ground Filtering for AC101TF (50)Section 7: Mechanical Information (51)Package Dimensions for AC101QF (100 pin PQFP) (51)Package Dimensions for AC101TF (80 pin TQFP) (52)BroadcomPage vi Document AC101-DS01-R¥¥¥¥¥Preliminary Data Sheet I AC101 06/04/01L IST OF F IGURESFigure 1:Functional Block Diagram (i)Figure 2:Multifunction LED Pin Connection (19)Figure 3:Dual-color LED Indicator for Link, Duplex, and Activity Status (20)Figure 4:AC101QF Pinout Diagram (21)Figure 5:AC101TF Pinout Diagram (22)Figure 6:Power-on Reset Timing (39)Figure 7:Management Data Interface Timing (40)Figure 8:100BASE-TX/FX MII Transmit Timing (41)Figure 9:100BASE-TX/FX MII Receive Timing (42)Figure 10:10BASE-T MII Transmit Timing (43)Figure 11:10BASE-T MII Receive Timing (44)Figure 12:10BASE-T 7-WireTransmit Timing (45)Figure 13:10BASE-T 7-Wire Receive Timing (46)Figure 14:10BASE-T 7-Wire Collision Timing (47)Figure 15:TX Application Termination Circuit (47)Figure 16:FX Application Termination Circuit (48)Figure 17:Power and Ground Filtering for the AC101QF (49)Figure 18:Power and Ground Filtering for the AC101TF (50)Figure 19:Package Dimensions for AC101QF (100 pin PQFP) (51)Figure 20:Package Dimensions for AC101TF (80 pin TQFP) (52)BroadcomDocument AC101-DS01-R¥¥¥¥¥Page viiI AC101Preliminary Data SheetL IST OF F IGURES06/04/01BroadcomPage viii Document AC101-DS01-R¥¥¥¥¥Preliminary Data Sheet I AC101 06/04/01L IST OF T ABLESTable 1:PHY Address Pins (11)Table 2:MDI (Media Dependent) Pins (11)Table 3:MII (Media Independent Interface) 100 PCS Bypass Pins (12)Table 4:10 Mbps PCS Bypass Pins (13)Table 5:10 Mbps 7-Wire Interface Pins (13)Table 6:Special/Test Pins (14)Table 7:Control and Status Pins (14)Table 8:LED Indicator Pins (16)Table 9:Power and Ground Pins (17)Table 10:No Connect Pins (18)Table 11:Technology Solutions (18)Table 12:Advanced LED Selections (19)Table 13:Register Summary (23)Table 14:Register 0: Control Register (24)Table 15:Register 1: Status Register (25)Table 16:Register 2: PHY Identifier 1 Register (26)Table 17:Register 3: PHY Identifier 2 Register (26)Table 18:Register 4: Auto-Negotiation Advertisement Register (26)Table 19:Register 5: Auto-Negotiation Link Partner Ability Register (27)Table 20:Register 6: Auto-Negotiation Expansion Register (28)Table 21:Register 7: Auto-Negotiation Next Page Transmit Register (28)Table 22:Register 16: Polarity and Interrupt Level Register (29)Table 23:Register 17: Interrupt Control/Status Register (30)Table 24:Register 18: Diagnostic Register (30)Table 25:Register 19: Power/Loopback Register (31)Table 26:Register 20: Cable Measurement Register (31)Table 27:Register 21: Mode Control Register (32)Table 28:Register 24: Receive Error Counter Register (33)Table 29:4B/5B Code-Group Table (33)Table 30:SMI Read/Write Sequence (34)Table 31:Total Power Consumption (35)Table 32:TTL I/O Characteristics (35)BroadcomDocument AC101-DS01-R¥¥¥¥¥Page ixI AC101Preliminary Data SheetL IST OF T ABLES06/04/01 Table 33:REFCLK and XTAL Pin Characteristics (36)Table 34:I/O Characteristics – LED/CFG Pin Characteristics (36)Table 35:100BASE-TX Transceiver Characteristics (36)Table 36:10BASE-T Transceiver Characteristics (37)Table 37:100BASE-FX Transceiver Characteristics (37)Table 39:Power On Reset Timing (39)Table 40:Management Data Interface Timing (39)Table 41:100BASE-TX/FX MII Transmit System Timing (40)Table 42:100BASE-TX/FX MII Receive System Timing (41)Table 43:10BASE-T MII Transmit System Timing (42)Table 44:10BASE-T MII Receive System Timing (44)Table 45:10BASE-T 7-Wire Transmit System Timing (45)Table 46:10BASE-T 7-Wire Receive System Timing (46)Table 47:10BASE-T 7-Wire Collision Timing (46)Table 48:Quad Flat Pack Outline: 20 x 14 mm (51)Table 49:Quad Flat Pack Outline: 12 x 12 mm (52)BroadcomPage x Document AC101-DS01-R¥¥¥¥¥06/04/01Section1:Functional DescriptionO VERVIEWThe AC101TF/QF PHYsical layer device (PHY) integrates the 100BASE-X and 10BASE-T functions in a single chip that is used in Fast Ethernet 10/100 Mbps applications. The 100BASE-X section consists of physical coding sublayer (PCS), phys-ical media attachment (PMA), and physical media dependent (PMD) functions and the 10BASE-T section consists of Manchester encoder/decoder (ENDEC) and transceiver functions. The device performs the following functions:•4B/5B•MLT3•NRZI•Manchester Encoding and Decoding•Clock and Data Recovery•Stream Cipher Scrambling/De-Scrambling•Adaptive Equalization•Line Transmission•Carrier Sense•Link Integrity Monitor•Auto-Negotiation (ANeg)•MII MAC connectivity•MII Management FunctionIt also provides an IEEE802.3u compatible Media Independent Interface (MII) to communicate with an Ethernet Media Ac-cess Controller (MAC). Selection of 10 or 100 Mbps operation is based on the settings of internal Serial Management Inter-face registers or determined by the on-chip ANeg logic. The device can operate in 10 or 100 Mbps with full-duplex or half-duplex mode.MAC I NTERFACEM EDIA I NDEPENDENT I NTERFACE (MII)The Media Independent Interface (MII) is an 18 wire MAC/PHY interface (see ”MII (Media Independent Interface) 100 PCS Bypass Pins” on page 12) described in 802.3u. The purpose of the interface is to allow MAC layer devices to attach to a variety of Physical Layer devices through a common interface. MII operates at either 100 Mbps or 10 Mbps, dependant on the speed of the Physical Layer. With clocks running at either 25 MHz or 2.5 MHz, 4 bit data is clocked between the MAC and PHY, synchronous with Enable and Error signals.At the time of PLL lock on an incoming signal from the wire interface, the PHY will generate RX_CLK at either 2.5 MHz for 10 Mbps or 25 MHz for 100 Mpbs.On receipt of valid data from the wire interface, RX_DV will go active signaling to the MAC that the valid data will be present-ed on the RXD[3:0] pins at the speed of the RX_CLK.On transmission of data from the MAC, TX_EN is presented to the PHY indicating the presence of valid data on TXD[3:0]. TXD[3:0] are sampled by the PHY synchronous to TX_CLK during the time that TX_EN is valid.Serial Management Interface (SMI)The PHY’s internal registers are accessible only through the MII 2-wire Serial Management Interface (SMI. see ”MII (Media06/04/01Independent Interface) 100 PCS Bypass Pins” on page 12). MDC is a clock input to the PHY which is used to latch in or out data and instructions for the PHY. The clock can run at any speed from DC to 25 MHz. MDIO is a bi-directional connection used to write instructions to, write data to, or read data from the PHY. Each data bit is latched either in or out on the rising edge of MDC. MDC is not required to maintain any speed or duty cycle, provided no half cycle is less than 20ns and that data is presented synchronous to MDC.MDC/MDIO are a common signal pair to all PHYs on a design. Therefore, each PHY needs to have its own unique Physical Address. The Physical Address of the PHY is set using the pins defined as PHYAD[4:0] (see ”PHY Address Pins” on page 11). These input signals are strapped externally and sampled as reset is negated. At idle, the PHY is responsible to pull MDIO line to a high state. Therefore, a 1.5K Ohms resistor is required to connect MDIO line to Vcc. The PHYAD can be reprogrammed via software. A detailed definition of the Serial Management registers follows.At the beginning of a read or write cycle, the MAC will send a continuous 32 bits of one at the MDC clock rate to indicate preamble. A zero and a one will follow to indicate start of frame. A read OP code is a one and a zero, while a write OP code is a zero and a one. These will be followed by 5 bits to indicate PHY address and 5 bits to indicate register address. Then 2 bits follow to allow for turn around time. For read operation, the first bit will be high impedance. Neither the PHY nor the station will assert this bit. During the second bit time, the PHY will assert this bit to a zero. For write operation, the station will drive a one for the first bit time, and a zero for the second bit time. The 16 bits data field is then presented. The first bit that is transmitted is bit 15 of the register content.InterruptsThe INTR pin (see ”MII (Media Independent Interface) 100 PCS Bypass Pins” on page 12) on the PHY will be asserted when-ever one of 8 selectable interrupt events occur. Assertion state is programmable to either high or low through the INTR_LEVL register bit (see ”Register 16: Polarity and Interrupt Level Register” on page 29). Selection is made by setting the appropriate bit in the upper half of the Interrupt Control/Status register (see ”Register 17: Interrupt Control/Status Register” on page 30). When the INTR bit goes active, the MAC interface is required to read the Interrupt Control/Status register to determine which event caused the interrupt. The Status bits are read only and clear on read. When INTR is not asserted, the pin is held in a high impedance state.Carrier Sense/RX_DVCarrier sense is asserted asynchronously on the CRS pins as soon as activity is detected on the receive data stream. RX_DV is asserted as soon as a valid SSD (Start-of-Stream Delimiter) is detected. Carrier sense and RX_DV are de-assert-ed synchronously upon detection of a valid end of stream delimiter or two consecutive idle code groups in the receive data stream. However, if the carrier sense is asserted and a valid SSD is not detected immediately, RX_ER is asserted instead of RX_DV. See ”MII (Media Independent Interface) 100 PCS Bypass Pins” on page 12.)In 10BASE-T mode, CRS is asserted asynchronously when the valid preamble and data activity is detected on the RXIP and RXIN pins.In the half-duplex mode, the CRS is activated during the transmit and receiving of data. In the full-duplex mode, the CRS is activated during data reception only.7-W IRE S ERIAL I NTERFACETo allow the PHY to run in legacy 10 Mbps only designs, the 7-wire serial interface, referred to as General Purpose Serial Interface (GPSI, see ”10 Mbps 7-Wire Interface Pins” on page 13) has been included. GPSI is an industry standard interface which has been implemented in many micro-controllers and micro-processors, as well as the majority of the 10 Mpbs MACs.The interface consists of 10 Mbps transmit and receive clocks, 10 Mbps serial transmit and receive data, transmit enable, receive enable and collision.When running the GPSI mode, the PHY must be forced to 10 Mbps only mode through hardware configuration.The 10BASE-T 7-wire interface is enabled when the GPIO[0] (see ”Control and Status Pins” on page 14) is pull low by 1 KΩduring reset.06/04/01PCS B YPASSThe AC101TF/QF is put into PCS bypass mode when the PCSBP pin is pull high (see ”Control and Status Pins” on page 14).100 Mbps PCS BypassIn MII designs, the encoding/decoding functions are performed in the PHY, thereby allowing 4-bit data exchange. Certain designs, however, require MAC/PHY data transfer to be in the form of 5-bit symbols. By selecting PCS Bypass mode of op-eration, the PHY will present data to, and accept data from the MAC layer as 5-bit symbols. In PCS Bypass mode the RX_ER and TX_ER pins are used as the RXD4 and TXD4 (see ”MII (Media Independent Interface) 100 PCS Bypass Pins” on page 12).10 Mbps PCS BypassWhen using PCS Bypass at 10 Mbps, the standard MAC/PHY interface is no longer valid. Differential drivers and receivers carry data serially between the MAC and PHY (see ”10 Mbps PCS Bypass Pins” on page 13).M EDIA I NTERFACEThe AC101TF/QF can be media-configured using any of the following three methods:•Hardware configuration: see ”Control and Status Pins” on page 14.•Software configuration: see ”Register 21: Mode Control Register” on page 32.•Auto-Negotiation (ANeg): see ”Control and Status Pins” on page 14 and ”MII-Specified Registers” on page 24.10BASE-T I NTERFACEWhen configured to run in 10BASE-T mode, either through hardware configuration, software configuration, or ANeg, the PHY will support all the features and parameters of the industry standards.Transmit FunctionIf the MII interface is used, Parallel to Serial logic is used to convert the 4-bit data into the serial stream. If the 7-Wire interface is used (see ”10 Mbps 7-Wire Interface Pins” on page 13), the serial data goes directly to the Manchester encoder where it is synthesized through the output waveshaping driver. The waveshaper reduces any EMI emission by filtering out the har-monics, therefore eliminating the need for an external filter.Receive FunctionThe received signal passes through a low-pass filter, which filters out the noise from the cable, board, and transformer. This eliminates the need for a 10BASE-T external filter. A Manchester decoder converts the incoming serial stream. If the 7-wire 10BASE-T interface is enabled (see ”10 Mbps 7-Wire Interface Pins” on page 13), the decoded serial data is presented to the MAC. If the MII interface is used (see ”MII (Media Independent Interface) 100 PCS Bypass Pins” on page 12), Serial to Parallel logic is used to generate the 4-bit data.Link MonitorThe 10-BASE-T link-pulse detection circuit will constantly monitor the RXIP/RXIN pins (see ”MDI (Media Dependent Inter-face) Pins” on page 11) for the presence of valid link pulses. In the absence of valid link pules, the Link Status bit will be cleared and the Link LED will de-assert.100BASE-TX I NTERFACEWhen configured to run in 100BASE-TX mode, either through hardware configuration, software configuration, or ANeg, the PHY will support all the features and parameters of the industry standards.06/04/01Transmit FunctionIn 100BASE-TX mode, the PHY transmit function converts synchronous 4-bit data nibbles from the MII to a pair of 125 Mbps differential serial data streams. The serial data is transmitted over network twisted pair cables via an isolation transformer. Data conversion includes 4B/5B encoding, scrambling, parallel to serial, NRZ to NRZI, and MLT-3 encoding. The entire op-eration is synchronous to 25 MHz and 125 MHz clock. Both clocks are generated by an on-chip PLL clock synthesizer that is locked on to an external 25 MHz clock source.The transmit data, in 4-bit nibbles at 25 MHz rate, is transmitted from the MAC to the PHY via the MII TXD[3:0] signals. The 4B/5B encoder replaces the first two nibbles of the preamble from the MAC frame with a /J/K/ code-group pair Start-of-Stream Delimiter (SSD), following the onset of TX_EN signal. The 4B/5B encoder appends a /T/R/ code-group pair End-of-Stream Delimiter (ESD) to the end of transmission in place of the first two IDLE code-groups that follow the negation of the TX_EN signal. The encapsulated data stream is converted from 4-bit nibbles to 5-bit code-groups. During the inter-packet gap, when there is no data present, a continuous stream of IDLE code-groups are transmitted. When TX_ER is asserted while TX_EN is active, the Transmit Error code-group /H/ is substituted for the translated 5B code word. The 4B/5B encoding is bypassed when Reg. 21.1 is set to “1”, or the PCSBP pin is strapped high. See ”MII (Media Independent Interface) 100 PCS Bypass Pins” on page 12.In 100BASE-TX mode, the 5-bit transmit data stream is scrambled as defined by the TP-PMD Stream Cipher function in order to reduce radiated emissions on the twisted pair cable. The scrambler encodes a plain text NRZ bit stream using a key stream periodic sequence of 2047 bits generated by the recursive linear function:X[n] = X[n-11] + X[n-9] (modulo 2)The scrambler reduces peak emissions by randomly spreading the signal energy over the transmitted frequency range, thus eliminating peaks at any single frequency. For repeater applications, where all ports transmit the same data simultaneously, signal energy is spread further by using a non-repeating sequence for each PHY (i.e., the scrambled seed is unique for each different PHY based on the PHY address).When Dis_Scrm (see ”Register 21: Mode Control Register” on page 32) is set to “0” the data scrambling function is disabled, the 5-bit data stream is clocked directly to the device’s PMA sublayer.Parallel to Serial, NRZ to NRZI, and MLT3 ConversionThe 5-bit NRZ data is clocked into PHY’s shift register with a 25 MHz clock and clocked out with a 125 MHz clock to convert it into a serial bit stream. The serial data is converted from NRZ to NRZI format, which produces a transition on Logic 1 and no transition on Logic 0. To further reduce EMI emissions, the NRZI data is converted to an MLT-3 signal. The conversion offers a 3dB to 6dB reduction in EMI emissions. This allows system designers to meet the FCC Class B limit. Whenever there is a transition occurring in NRZI data, there is a corresponding transition occurring in the MLT-3 data. For NRZI data, it changes the count up/down direction after every single transition. For MLT-3 data, it changes the count up/down direction after every two transitions. The NRZI to MLT-3 data conversion is implemented without reference to the bit timing or clock information. The conversion requires detecting the transitions of the incoming NRZI data and setting the count up/down di-rection for the MLT-3 data. Asserting FX_SEL high will disable this encoding.The slew rate of the transmitted MLT-3 signal can be controlled to reduce EMI emissions. The MLT-3 signal after the mag-netic has a typical rise/fall time of approximately 4 ns, which is within the target range specified in the ANSI TP- PMD stan-dard. This is guaranteed with either 1:1 or 1.25:1 transformer.Receive FunctionThe 100BASE-TX receive path functions as the inverse of the transmit path. The receive path includes a receiver with adap-tive equalization and DC restoration in the front end. It also includes a MLT-3 to NRZI converter, 125 MHz data and clock recovery, NRZI/NRZ conversion, Serial-to-Parallel conversion, de-scrambler, and 5B/4B decoder. The receiver circuit starts with a DC bias for the differential RX+/- inputs, followed with a low-pass filter to filter out high frequency noise from the trans-mission channel media. An energy detect circuit is also added to determine whether there is any signal energy on the media. This is useful in the power-saving mode. The amplification ratio and slicer’s threshold is set by the on-chip bandgap refer-ence.06/04/01Baseline Wander CompensationThe 100BASE-TX data stream is not always DC balanced. The transformer blocks the DC components of the incoming sig-nal, thus the DC offset of the differential receive inputs can drift. The shifting of the signal level, coupled with non-zero rise and fall times of the serial stream can cause pulse-width distortion. This creates jitter and possible increase in the bit error rates. Therefore, a DC restoration circuit is needed to compensate for the attenuation of the DC component. This PHY im-plements a patent-pending DC restoration circuit. Unlike the traditional implementation, the circuit does not need the feed-back information from the slicer or the clock recovery circuit. This design simplifies the circuit design and eliminates any random/systematic offset on the receive path. In the 10BaseT and the 100BASE-FX modes, the baseline wander correction circuit is not required, and therefore is disabled.Clock/Data RecoveryThe equalized MLT-3 signal passes through the slicer circuit, and gets converted to NRZI format. The PHY uses a propri-etary mixed-signal phase locked loop (PLL) to extract clock information from the incoming NRZI data. The extracted clock is used to re-time the data stream and set the data boundaries. The transmit clock is locked to the 25 MHz clock input while the receive clock is locked to the incoming data streams. When initial lock is achieved, the PLL switches to the data stream, extracts the 125 MHz clock, and uses it for the bit framing for the recovered data. The recovered 125 MHz clock is also used to generate the 25 MHz RX_CLK signal. The PLL requires no external components for its operation and has high noise im-munity and low jitter. It provides fast phase alignment and locks to data in one transition. Its data/clock acquisition time after power-on is less than 60 transitions. The PLL can maintain lock on run-lengths of up to 60 data bits in the absence of signal transitions. When no valid data is present, i.e. when the SD is de-asserted, the PLL will switch and lock on to TX_CLK. This provides a continuously running RX_CLK. At the PCS interface, the 5 bit data RXD[4:0] is synchronized to the 25 MHz RX_CLK. See ”MII (Media Independent Interface) 100 PCS Bypass Pins” on page 12.Decoder/De-scramblerThe de-scrambler detects the state of the transmit Linear Feedback Shift Register (LFSR) by looking for a sequence repre-senting consecutive idle codes. The de-scrambler acquires lock on the data stream by recognizing IDLE bursts of 30 or more bits and locks its frequency to its de-ciphering LFSR.Once lock is acquired, the device can operate with an inter-packet-gap (IPG) as low as 40 nS. However, before lock is ac-quired, the de-scrambler needs a minimum of 270 nS of consecutive idles in between packets in order to acquire lock.The de-ciphering logic also tracks the number of consecutive errors received while the RX_DV (see ”MII (Media Independent Interface) 100 PCS Bypass Pins” on page 12) is asserted. Once the error counter exceeds its limit currently set to 64 con-secutive errors, the logic assumes that the lock has been lost, and the de-cipher circuit resets itself. The process of regaining lock will start again.Stream cipher de-scrambler is not used in the 100BASE-FX and the 10BASE-T modes.Link MonitorSignal level is detected through a squelch detection circuitry. A signal detect (SD) circuit allows the equalizer to assert high whenever the peak detector detects a post-equalized signal with peak to ground voltage greater than 400 mV. This is ap-proximately 40% of a normal signal voltage level. In addition, the energy level must be sustained for longer than 2~3 µS in order for the signal detect signal to stay on. The SD gets de-asserted approximately 1~2 µs after the energy level drops consistently below 300 mV from peak to ground.The link signal is forced low during a local loopback operation (Loopback register bit is set) and forced to high when a remote loopback is taking place (EN_RPBK is set, see ”Register 21: Mode Control Register” on page 32).In forced 100BASE-TX mode, when a cable is unplugged or no valid signal is detected on the receive pair, the link monitor enters in the “link fail” state and NLP's are transmitted. When a valid signal is detected for a minimum period of time, the link monitor enters Link Pass State and transmits MLT-3 signal.。

资料编码产品名称使用对象产品版本编写部门资料版本以太网标准和物理层、数据链路层专题拟制:日期:审核:日期:审核:日期:批准:日期:华为技术有限公司版权所有侵权必究修订记录目录1以太网标准 (5)1.1以太网标准 (5)1.2IEEE标准 (5)1.3物理层 (8)1.3.1以太网接口类型 (8)1.3.2电口 (8)1.3.3光口 (11)1.4FE自协商 (12)1.4.1自协商技术的功能规范 (13)1.4.2自协商技术中的信息编码 (14)1.4.3自协商功能的寄存器控制 (16)1.4.4GE自协商 (18)1.5物理层芯片和MAC层芯片接口简介 (19)1.5.1MII (19)1.5.2MDIO管理寄存器 (20)1.5.3RMII (20)1.5.4SMII (21)1.5.5SS-SMII (21)1.5.6GMII (22)1.5.7TBI (22)2以太网数据链路层 (23)2.1以太网的帧格式 (23)2.2以太网的MAC地址 (25)2.3CSMA/CD算法 (26)2.3.1CSMA/CD发送过程 (27)2.3.2CSMA/CD如何接收 (28)2.4半双工以太网的限制 (31)2.5以太网流量控制 (34)2.5.1反压(Backpressure) (34)2.5.2PAUSE 流控 (34)关键词:以太网物理层数据链路局域网城域网协议标准祯结构摘要:本文详细地阐述了以太网的标准,以太网在各个传输层面的具体结构和工作方式以及控制方式。

缩略语清单:无。

参考资料清单无。

以太网标准和物理层、数据链路层专题1 以太网标准1.1 以太网标准局域网(LAN)技术用于连接距离较近的计算机,如在单个建筑或类似校园的集中建筑中。

城市区域网(MAN)是基于10-100Km的大范围距离设计的,因此需要增强其可靠性。

但随着通信的发展,从技术上看,局域网和城域网有融合贯通的趋势。

1.2 IEEE标准IEEE是电气和电子工程师协会(Institute of Electrical and ElectronicsEngineers)的简称,IEEE组织主要负责有关电子和电气产品的各种标准的制定。

千兆以太网物理层收发器功能测试方法作者:***来源:《现代信息科技》2022年第07期摘要:针对自主研发的一款千兆以太网物理层收发器(GPHY)的功能测试,设计了GPHY的测试系统。

为便于定位测试中的问题,按照信号流将测试分为三个阶段:先进行内回环测试,再进行外回环测试,最后移植LwIP实现ping测试。

采用一款Cortex-M4內核具备GMAC(Gigabit Media Access Control)外设的MCU作主设备,实现了GPHY的功能测试程序。

在程序中,创建了可动态调整的系统日志和结构化的多参数函数接口,使得查看测试结果和进行压力测试更加简便。

关键词:GPHY;功能测试;GMAC;Cortex-M4;LwIP中图分类号:TP311 文献标识码:A文章编号:2096-4706(2022)07-0042-04Function Test Method for Gigabit Ethernet Physical Layer TransceiverLIU Wenyuan(Network Communication Institute of CETC, Shijiazhuang 050011, China)Abstract: In view of the function test of the Gigabit Physical Layer Transceiver (GPHY),this paper designs a GPHY test system. In order to easily locate the problems in the test, the test isdivided into three stages according to the signal flow. Firstly it conducts the inner loop test, then conducts the outer loop test, and finally transplants the LwIP to achieve the ping test. This paper uses a Cortex-M4 kernel and MCU with GMAC (Gigabit Media Access Control) peripheral as the master device to realize the GPHY function test program. In the test program, it creates the dynamically adjustable system log and the structured multi-parameters function interface, which make it handier to view test results and perform stress tests.Keywords: GPHY; function test; GMAC; Cortex-M4; LwIP0 引言随着物联网时代的到来,嵌入式系统的以太网设备需求量与日俱增,而负责以太网数据编码和传输的物理层收发器的需求量也随之增长[1]。

以太网物理层芯片

什么是以太网物理层芯片?

以太网物理层芯片是一种用于将以太网通信报文以端到端的形式传输的硬件芯片。

它可以实现以太网的设备之间的物理连接,并将以太网上的数据信息转换为二进制形式,以实现快速和可靠地数据传输。

以太网物理层芯片可以处理多种以太网协议,如IEEE 802.3 10BaseT、IEEE 802.3u 100BaseT、IEEE 802.3ab 1000BaseT及其高级协议。

一、以太网物理层芯片的特点

1. 支持多种以太网协议:以太网物理层芯片支持各种以太网协议,如IEEE 80

2.3 10BaseT、IEEE 802.3u 100BaseT、IEEE 802.3ab 1000BaseT 及其高级协议。

2. 超高以太网传输速度:以太网物理层芯片可以提供超高的以太网传输速度,以满足用户的高数据传输量要求。

3. 芯片尺寸小、功耗低:以太网物理层芯片具有小体积尺寸和较低的功耗要求,可以满足可移植式设备要求。

4. 具有安全功能:以太网物理层芯片可以具备安全功能,可以满足企业网络的安全要求。

二、以太网物理层芯片的应用

1. 增强型PCI卡:增强型PCI卡可以使用以太网物理层芯片进行以太网通信,可以提供最高速度的数据传输服务。

2. 无线设备:无线设备可以使用以太网物理层芯片提供高效的数据传输速率,并可以支持高效能和安全性要求。

3. 智能家居:以太网物理层芯片可以提供高效的物理连接,可以为智能家居设备提供的高质量的服务。

4. 虚拟网络:以太网物理层芯片也可以用于构建虚拟网络,以满足企业网络实现资源共享及数据传输服务的要求。

MAC和PHY的区别一块以太网网卡包括OSI(开方系统互联)模型的两个层。

物理层和数据链路层。

物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。

数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。

1.网卡的基本结构以太网卡中数据链路层的芯片一般简称之为MAC控制器,物理层的芯片我们简称之为PHY。

许多网卡的芯片把MAC和PHY的功能做到了一颗芯片中,比如Intel 82559网卡的和3COM 3C905网卡。

但是MAC和PHY的机制还是单独存在的,只是外观的表现形式是一颗单芯片。

当然也有很多网卡的MAC和PHY是分开做的,比如D-LINK的DFE-530TX等。

图一:MAC和PHY分开的以太网卡(点击放大)图二:MAC和PHY集成在一颗芯片的以太网卡(点击放大)①RJ-45接口②Transformer(隔离变压器)③PHY芯片④MAC芯片⑤EEPROM ⑥BOOTROM插槽⑦WOL接头⑧晶振⑨电压转换芯片⑩LED指示灯2.什么是MAC?首先我们来说说以太网卡的MAC芯片的功能。

以太网数据链路层其实包含MAC(介质访问控制)子层和LLC(逻辑链路控制)子层。

一块以太网卡MAC芯片的作用不但要实现MAC 子层和LLC子层的功能,还要提供符合规范的PCI界面以实现和主机的数据交换。

MAC从PCI总线收到IP数据包(或者其他网络层协议的数据包)后,将之拆分并重新打包成最大1518Byte,最小64Byte的帧。

这个帧里面包括了目标MAC地址、自己的源MAC地址和数据包里面的协议类型(比如IP数据包的类型用80表示)。

最后还有一个DWORD(4B yte)的CRC码。

可是目标的MAC地址是哪里来的呢?这牵扯到一个ARP协议(介乎于网络层和数据链路层的一个协议)。

第一次传送某个目的IP地址的数据的时候,先会发出一个ARP包,其MAC的目标地址是广播地址,里面说到:”谁是xxx.xxx.xxx.xxx这个IP地址的主人?”因为是广播包,所有这个局域网的主机都收到了这个ARP请求。

以太网知识讲座(3)——物理层器件王廷尧,马克城(天津光电通信产业集团恒光科技有限公司;天津 300211)摘 要:系统地介绍了以太网的基本要领介质接入控制和物理层标准规范,以太网信号的帧结构、网络硬件设备、网络组成及主要性能,以及以太网信号在PDH、SDH/SONET中的传输等等。

由于以太网中的各种设备必需通物理层接口器件才能与网络传输介质相连,因此本部分主要介绍物理层器件。

关键词:以太网;物理层;接口1 物理层器件物理层器件(PHY:Physical Layer Interface Devices)是将各网元连接到物理介质上的关键部件。

负责完成互连参考模型(OSI)第I层中的功能,即为链路层实体之间进行bit传输提供物理连接所需的机械、电气、光电转换和规程手段。

其功能包括建立、维护和拆除物理电路,实现物理层比特(bit)流的透明传输等。

通常物理层的功能均被集成在一个芯片之中,但有的芯片也将部分链路层的功能集成进来,如物理介质接入控制(MAC:Media Access Con-brol)子层的功能等。

其MAC/Repeater接口在10Mbit/s、100Mbit/s两种速率下有10/100MII、100M符号、10M串行和链路脉冲几种模式。

1.1 PHY的结构如图1所示,物理层包括四个功能层和两上层接口。

两个层接口为物理介质无关层接口(MII)和物理介质相关层接口(MDI),在MII的上层是逻辑数据链路层(DLL),而MDI的下层则直接与传输介质相连。

以下对四个功能层和两个层接口分别进行介绍。

1.2 MIIMII满足ISO/IEC 8802-3和IEEE 802.3标准的要求,支持以太网数据传输的速率为10Mbit/s,100Mbit/s、1000Mbit/s和10Gbit/s,有对应的运行时钟。

MII接口主要由与链路层之间的端口(MAC-PHY)和与站管理实体(STA:Station Management Entity)之间的端口(STA-PHY)两部分组成。

1.2.1 MAC-PHY端口这是MAC与PHY器件之间的接口,包括同步收发接口和介质状态控制接口。

在介质状态控制接口中有载波读出信号(CRS:Carrier Sense Signal)和碰撞检测信号(COL:Collision Detection Signal)等。

1.2.2 STA-PHY端口STA-PHY作为MII接口的一部分,用于在STA和PHY器件之间交换有关控制、状态和配置方面的信息。

为此,ISO/IEC、IEEE规范了这个双线串行管理接口的相关协议及管理信息帧的结构和管理寄存器的标准。

(1)管理寄存器按标准,管理寄存器集(Management Registerset)包括强制性“基本控制”寄存器(Mandatory “Basic Control”Registers)、状态寄存器(Status Re-gisters)和专用扩展寄存器ICS(Specifie Extended Registers)几部分。

(2)管理信号帧结构管理接口是一个双向串行接口,用于交换PHY与STA之间的配置、控制和状态数据,利用定义的寄存器集实现PHY和STA的数据交换。

STA可以启动所有的处理功能。

ISO/IEC、IEEE对串行管理数据流定义了相关管理帧结构和协议(管理信号帧的结构已在第一讲中讨论)。

1.3 物理编码子层物理编码子层(PCS)有两个对外接口,一是与MII的接口,二是与物理介质连接子层(PMA:Physical Medium Attachment Sublayer)的接口。

PCS子层遵循ISO/IEC 8802.3和IEEE 802.3标准,功能包括对信号的编译码、收发处理、管理和控制等。

这里可用100Base-TX速率来讨论PCS子层要完成的功能。

1.3.1 PCS在100Mbit/s与10Mbit/s 下的工作模式一般称10Base-T为以太网,10Base-TX为快速以太网,两者信号的速率,执行的协议以及采用的传输介质均有所不同。

PCS子层对于10Base-TX 信号进行4B/5B编译码、扰码(Serambled)和MLT-3编码,将信号交换为62.5MHz的三元数据,然后通过隔离变压器送入5类双绞线电缆或者比5类双绞线电缆更好地电缆线路中传输。

对于10Base-T信号则需进行曼乇斯特(Manchester)编译码和相关的处理。

对10Base-TX信号和10Base-T信号处理的功能比较如表1所示。

1.3.2 PCS发送子层这里讨论10Mbit/s和100Mbit/s两种情况。

PCS发送子层的功能是编码、碰撞检测与并/串变换等。

(1)100Mbit/s PCS发送子层PCS发送10Base-TX的数据需要进行4B/5B编码,即是将4bit数据组成的奈培(nib)变换成由5bit数据组成的码字。

4B/5B编码的目的就是将数据包的起始符、帧结束、空载与控制功能等符号都编成码组进行传输。

将4B码的nib映射入5B码字的过程是按IEEE 802.3标准规范进行的。

每个MAC/Repeater帧的前16nib(16×4=64bit)表示帧前序(Frame Preamble)。

PCS将前二个nb用数据流起始标帜符/J/K/代替,并在帧结束时加入数据流结束标帜符/T/R/,用于表示包的结束(ESD:End-of-Stream Delimiter)。

4B/5B编码器同样在包之间充满间隔空信号(Idle Period)。

用间隔空(Idle)符号实现数据流的连续性。

表2即是4B/5B编码表。

编码后的符号送入后面的扰码器。

PCS发送的子层4B/5B编码,有32种5bit的编码组合,其中16种5bit 组合用于表示原16捉nib(4bit)的组合;另16种5bit组合,IEEE标准定义了6种用于控制使用的组合,还有10种认为非法的组合。

IEEE定义的6种控制码组是:a./H/表示一个发送差错;b./I/表示一个IDLE空载;c.两个码组表示数据流启始标帧符(SSD);d./J/和/K/;e.两个码组表示数据流结束标帜符(ESD);f./T/和/R/;(2)10Mbit/s的PCS发送子层按ISO/IEC、IEEE标准的要求,10Mbit/s 的PCS发送子层采用Manchester编码,即利用数据与时钟相“异或”,使数据每bit的前一半取数据的补码,后一半取数据的原码,从而保证跃变沿总是发生在每bit 的中央处。

Manchester编码器在数据包结束后加入一个起始空脉冲(SOI:Start of Idle Pulse)。

在编码过程中与包之间的间隔则不进行编码,由链路脉冲填充。

Manchester编码过程的时间关系如图2所示。

从MAC/Repeater接口来的4bit的nib流或串行bit流,利用Manchester编码进行编码。

编码的逻辑是:a.二进制NRZ数据“1”当码元(bit)周期前半周期时取负值;当码元(bit)周期后半周期时取正值。

b.二进制NRZ数据“0”当码元(bit)周期前半周期时取正值;当码元(bit)周期后半周期时取负值。

使用Manchester编码的优点,一是每个bit周期可有一编码时钟;二是不必考虑数据本身是“0”还是“1”,增加了数据的跃变沿。

但它的缺点是编码后的数据率增加了一倍。

PCS子层还可完成碰撞检测,即在数据传输和接收同时发生时,需按标准规范和根据工作模式进行处理。

在半双工工作模式下,发生碰撞时产生检测信号(COL:Collision Detection Signal),而在全双工工作模式下,不产生COL。

1.3.3 PCS接收子层(1)PCS接收子层的功能PCS接收子层主要完成以下功能:a.串/并变换;b.载波检测;c.4B/5B或Manchester译码;d.码组成帧。

即PCS接收子层状态机连续接收从PMA来的数据,将其由串行变换为并行,以及成帧和译码,之后送到MAC/Pepeater接口。

接收状态机则在接收和数据状态判断之间进行转换并连续这个过程,直到发生下述情况之一时为止:数据流结束标帜符(ESD,即/T/R/符号);有差错发生;过早结束(空号)。

依据ESD,接收状态机返回到Idle状态时,ESD并没有被送入MAC/Pepeater接口,因此检测出的差错将迫使接收状态机宣告接收错,并等待后面符号。

若接收状态机检出“过早结束信号(Prematureend)”,同样也要宣告接收错,而返回Idle状态。

(2)100Mbit/s的PCS接收子层4B/5B译码器4B/5B编码,因此在收端必须利用4B/5B译码器进行译码,即将5B码组映射成4B码。

4B/5B译码器的输入严自解扰器(Descrambler)。

按表3所示,将5bit码组变换为4bit的nib。

4B/5B译码器应首先将SSD帧符(/J/K/符号)拆除并用两个4B数据“5”nb(/5/符号)来代替,对ESD帧符(/T/R/符号)也需被拆除并用两个4B数据“0”nib(/I/符号)代替。

(3)10Mbit/s PCS接收子层Manchester译码Manchester译码器将从双绞线对接收到的Manchester编码信号变换为原NRZ信号,并将空载开始脉冲 (SOI:Start of Idle)拆除。

在发送端,NRZ数据S被Manchester编剧骊,即MS=S⊕C(C为时钟<Clock>)。

在收端,MS数据重新被译码为S,即图3、图4即为ML2653型10Base-T物理接口芯片发收Manchester信号编译码的一时图。

PCS子层提供CRS载波检测信号(Carrier Sense Signal)和碰撞检出信号(Collision Detection Signal),用这两个控制信号实现对MII接口的控制与管理。

1.4 PMA子层PMA与PCS及PMD子层相连,因此必须有两个接口;一个是到上边PCS 子层的接口,另一个是到下边PMD子层的接口。

PMA子层主要功能是:(1)链路监测(Link Monitoring);(2)载波检测(Carrier Dete-cting);(3)MRZI编/译码(NRZI En-coding/Decoding);(4)发送时钟合成(Transmit Clock Synthesis);(5)接收时钟恢复(Receive Clock Recovery)。

1.4.1 PMA发送子层PMA发送子层(PMA Transmit Sublayer)从PCS子层接收串行比特流并且将其变换为NRZI格式(10Mbit/s不用),然后将其送入物理介质相关子层(PMD)。