用VHDL语言实现的数码管显示程序(包含动态和静态)

- 格式:doc

- 大小:15.50 KB

- 文档页数:2

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下➢可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下➢可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

VHDL 语言数码管静态显示5080211 EDA课程设计Dennis静态扫描显示电路设计专业:自动化班级学号:姓名:Dennis20XX年 12 月 11 日1Dennis一、设计实验目的:在MAX+plusII软件平台上,熟练运用VHDL语言,完成静态扫描显示电路的VHDL语言编程、编译、综合、仿真,使用EDA实验箱,实现静态扫描显示电路的硬件功能。

二、设计实验说明及要求:1、静态扫描显示电路组成:计数器、显示译码器、扫描电路组成。

在静态扫描显示电路中最关键的是如何在每一个数码管静态显示固定的数字,除此之外,静态扫描显示电路需清零控制端\\启动控制端使静态扫描显示电路清零及启动。

2、静态扫描显示电路要在七个数码管实现静态显示每位同学的班级学号显示。

3、能够完成清零、启动功能。

三、数字时钟组成及功能:1、计数器:用来产生实现数码管分配;2、扫描显示译码器:完成对7字段数码管显示的控制;四、系统硬件要求:1、时钟信号为10MHz;2、FPGA芯片型号EPM7128SLC84-15、EP1K30TC144-3或EP1K100QC208-3;3、8个7段扫描共阴级数码显示管;4、按键开关;五、设计内容及步骤:1、设计思路:静态扫描显示电路的主要组成为:计数器、显示译码器、扫描电路组成。

我的学号为5080211,因为需要七个数码管,所以用七进制计数器即可,计数器从0到6计数,到6后归0,接着开始从0到6计数。

然后扫描电路根据每个时刻的计数器计数值,输出相应的数码管,从而选择控制,即sel2,sel1,sel0。

从试验箱的一排数码管从最右端向第七个数码管循环扫描。

例如:sel2,sel1,sel0为“000”则选择地的是最右边的数码显示管。

当扫描到一个数码管,根据此时需要输出的数值,利用显示译码器翻译为相应的数码管显示编码即可,比如要sel=“000”时,要输出的数值是“0100”,将“0100”,翻译为“1100110”给sel选中的数码管显示出来即可。

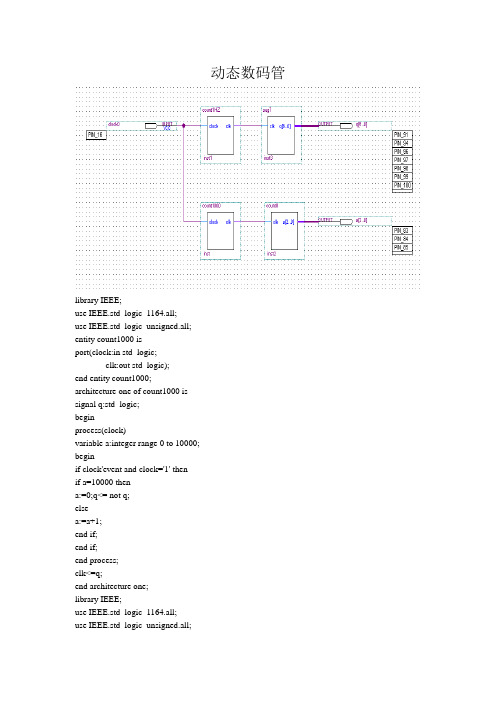

动态数码管library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;entity count1000 isport(clock:in std_logic;clk:out std_logic);end entity count1000;architecture one of count1000 issignal q:std_logic;beginprocess(clock)variable a:integer range 0 to 10000;beginif clock'event and clock='1' thenif a=10000 thena:=0;q<= not q;elsea:=a+1;end if;end if;end process;clk<=q;end architecture one;library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;entity count8 isport(clk:in std_logic;a:buffer std_logic_vector(2 downto 0)); end entity count8;architecture one of count8 isbeginprocess(clk)beginif clk'event and clk='1' thenif a=7 thena<="000";elsea<=a+1;end if;end if;end process;end one;library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;entity seg7 isport(clk:in std_logic;q:out std_logic_vector(6 downto 0));end entity seg7;architecture one of seg7 issignal w:std_logic_vector(3 downto 0):="0000"; beginprocess(clk)beginif clk'event and clk='1' thenif w="1111" thenw<="0000";elsew<=w+1;end if;end if;end process;process(w)begincase w iswhen "0000"=> q<="1111110";when "0001"=> q<="0110000";when "0010"=> q<="1101101";when "0011"=> q<="1111001";when "0100"=> q<="0110011"; when "0101"=> q<="1011011"; when "0110"=> q<="1011111";when "0111"=> q<="1110000";when "1000"=> q<="1111111";when "1001"=> q<="1111011";when "1010"=> q<="1110011";when "1011"=> q<="0011111";when "1100"=> q<="1001110";when "1101"=> q<="0111101";when "1110"=> q<="1001111";when others=> q<="1000111";end case;end process;end one;library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all; entity count1HZ isport(clock:in std_logic;clk:out std_logic);end entity count1HZ;architecture one of count1HZ is signal q:std_logic;beginprocess(clock)variable a:integer range 0 to 10000000; beginif clock'event and clock='1' thenif a=10000000 thena:=0;q<= not q;elsea:=a+1;end if;end if;end process;clk<=q;end architecture one;。

EDA实验二七段数码管显示译码的设计一、实验目的1、掌握七段数码管译码器的工作原理;2、学会运用波形仿真测试检验程序的正确性;3、学会运用波形仿真测试检验程序的正确性。

二、实验设备ZYE1502C型实验箱三、内容要求1、用拨位开关输入8421BCD码,七段数码管显示“0-F”16个16进制的数字。

2、观察字符亮度和显示刷新的效果:(1)在8个七段数码管上同时显示某一数字;(2)在8个七段数码管上动态显示某一数字。

3、扩展内容:(1)动态显示时,能即时改变显示的顺序;(2)动态显示时,实现显示数字从0~F的循环显示。

四、实验步骤1、输入:设计部分采用VHDL语言完成;2、编译;3、仿真;4、下载;5、连线。

(1)四个拨位开关(在P1、P2处选择)连接D3、D2、D1、D0信号所对应的管脚。

时钟CLK所对应的管脚同实验箱上的时钟源相连。

(2)扫描片选信号DIG(0 TO 3)的管脚同七段数码管(共阴)相连;(3)七段数码管驱动信号A,B,C,D,E,F,G的管脚分别同扫描数码管的段输入PCLK处的连接线孔A,B,C,D,E,F,G相连。

五、实验报告1、论述实验过程和步骤;2、填写正确的实验结果。

(1)通过两种显示效果分析:字符显示亮度同扫描频率的关系,且让人眼感觉不出光闪烁现象的最低扫描频率是多少?答:扫描频率越高,显示亮度越低。

人眼看是否闪烁与所用的时钟和分频方式有关,在频率稳定和分频均匀的情况下,最低扫描频率为256Hz,若分频不均匀或频率不稳定,则需更高频率。

(2)字形编码的种类,即一个7段数码管可产生多少种字符,产生所有字符需要多少根被译码信号线?答:一个7段数码管可产生2^7=128种字符,产生所有字符至少需要7根被译码信号线。

但假如只编译0-F,16个字符,则至少只需要4根被译码信号线。

六、实验小结。

答:1、不同控制端需要预先分配控制优先级,否则编写的时候会出现很多问题。

优先级分为普通和特殊,一般错误情况可以跨越权限显示出来。

可实现功能:数码管显示,最右侧的一位数码管以1Hz变化由0-9循环往复分频+计数+显示整合之后(请注意改名后使用)100%成功:library ieee;use ieee.std_logic_1164.all;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity zhengti28 isport(clk:in std_logic;zhengti28:out std_logic;cp,clear:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);cat:OUT STD_LOGIC_VECTOR(5 DOWNTO 0));end;architecture one of zhengti28 issignal cnt:std_logic_vector(2 downto 0);signal clk_temp:std_logic;SIGNAL temp:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL tmp: INTEGER RANGE 0 TO 49999999;SIGNAL clk_out: STD_LOGIC;constant m:integer:=5;beginprocess(clk)beginif clk'event and clk='1' thenif cnt=m thenclk_temp<=not clk_temp;cnt<="000";elsecnt<=cnt+1;end if;end if;end process;zhengti28<=clk_temp;P1:PROCESS(cp)BEGINIF cp'event AND cp='1' THENIF tmp=49999999 THENtmp<=0;ELSEtmp<=tmp+1;END IF;IF tmp<=24999999 THENclk_out<='0';ELSEclk_out<='1';END IF;END IF;END PROCESS P1;P2:PROCESS(clear,clk_out)BEGINIF clear='1' THEN temp<="0000";ELSIF (clk_out'event and clk_out='1') THENIF temp="1001"THENtemp<="0000";ELSEtemp<=temp+1;END IF;END IF;END PROCESS P2;q<=temp;PROCESS(temp)BEGINCASE temp ISWHEN "0000"=>LED7S<="0111111";--X"3F"->0WHEN "0001"=>LED7S<="0000110";--X"06"->1WHEN "0010"=>LED7S<="1011011";--X"5B"->2WHEN "0011"=>LED7S<="1001111";--X"4F"->3WHEN "0100"=>LED7S<="1100110";--X"66"->4WHEN "0101"=>LED7S<="1101101";--X"6D"->5WHEN "0110"=>LED7S<="1111101";--X"7D"->6WHEN "0111"=>LED7S<="0000111";--X"07"->7WHEN "1000"=>LED7S<="1111111";--X"7F"->8WHEN "1001"=>LED7S<="1101111";--X"6F"->9WHEN OTHERS=>LED7S<="0000000";--X"6F"->null END CASE;cat<="111110";END PROCESS;END;其管脚设置:异步复位8421码十进制计数器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY BCDcoder ISPORT(cp,clear:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END BCDcoder;ARCHITECTURE a OF BCDcoder ISSIGNAL temp:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL tmp: INTEGER RANGE 0 TO 49999999; SIGNAL clk_out: STD_LOGIC;BEGINP1:PROCESS(cp)BEGINIF cp'event AND cp='1' THENIF tmp=49999999 THENtmp<=0;ELSEtmp<=tmp+1;END IF;IF tmp<=24999999 THENclk_out<='0';ELSEclk_out<='1';END IF;END IF;END PROCESS P1;P2:PROCESS(clear,clk_out)BEGINIF clear='1' THEN temp<="0000";ELSIF (clk_out'event and clk_out='1') THENIF temp="1001"THENtemp<="0000";ELSEtemp<=temp+1;END IF;END IF;END PROCESS P2;q<=temp;END a;分频器(上图为分频结果)library ieee;use ieee.std_logic_1164.all;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity fenpin28 isport(clk:in std_logic;fenpin28:out std_logic);end;architecture one of fenpin28 issignal cnt:std_logic_vector(2 downto 0);signal clk_temp:std_logic;constant m:integer:=5;beginprocess(clk)beginif clk'event and clk='1' thenif cnt=m thenclk_temp<=not clk_temp;cnt<="000";elsecnt<=cnt+1;end if;end if;end process;fenpin28<=clk_temp;end;计数器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY jishu28 ISPORT(cp,clear:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END jishu28;ARCHITECTURE a OF jishu28 ISSIGNAL temp:STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL tmp: INTEGER RANGE 0 TO 49999999; SIGNAL clk_out: STD_LOGIC;BEGINP1:PROCESS(cp)BEGINIF cp'event AND cp='1' THENIF tmp=49999999 THENtmp<=0;ELSEtmp<=tmp+1;END IF;IF tmp<=24999999 THENclk_out<='0';ELSEclk_out<='1';END IF;END IF;END PROCESS P1;P2:PROCESS(clear,clk_out)BEGINIF clear='1' THEN temp<="0000";ELSIF (clk_out'event and clk_out='1') THENIF temp="1001"THENtemp<="0000";ELSEtemp<=temp+1;END IF;END IF;END PROCESS P2;q<=temp;END a;数码管:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY shuma28 ISPORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);cat:OUT STD_LOGIC_VECTOR(5 DOWNTO 0));END;ARCHITECTURE ONE OF shuma28 ISBEGINPROCESS(A)BEGINCASE A ISWHEN "0000"=>LED7S<="0111111";--X"3F"->0WHEN "0001"=>LED7S<="0000110";--X"06"->1WHEN "0010"=>LED7S<="1011011";--X"5B"->2WHEN "0011"=>LED7S<="1001111";--X"4F"->3WHEN "0100"=>LED7S<="1100110";--X"66"->4WHEN "0101"=>LED7S<="1101101";--X"6D"->5WHEN "0110"=>LED7S<="1111101";--X"7D"->6WHEN "0111"=>LED7S<="0000111";--X"07"->7WHEN "1000"=>LED7S<="1111111";--X"7F"->8WHEN "1001"=>LED7S<="1101111";--X"6F"->9WHEN OTHERS=>LED7S<="0000000";--X"6F"->null END CASE;cat<="111110";END PROCESS;END;一个有很多vhdl代码的网址:/download/shaoqso111/1901736。