《数字系统设计I》补充作业(20140317)

- 格式:pdf

- 大小:608.82 KB

- 文档页数:19

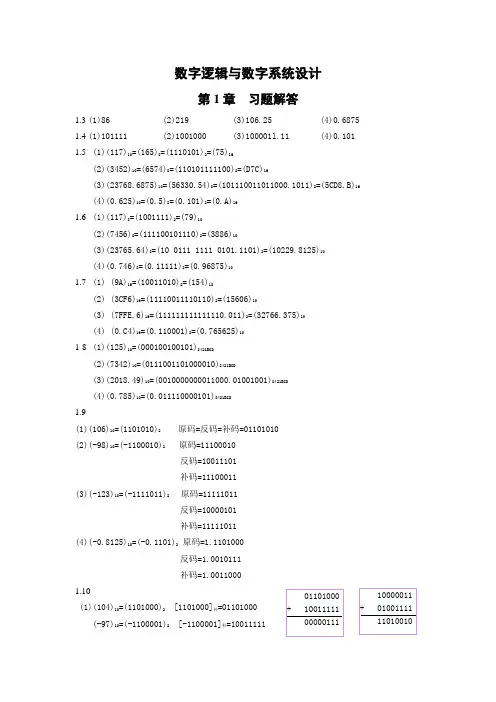

将下列各式写成按权展开式:()10=3×102+5×101+2×100+6×10-1()2=1×22+1×20+1×2-1+1×2-3()8=5×81+54×80+6×8-1()16=1×162+3×161+10×160+4×16-1+15×16-2按十进制0~17的次序,列表填写出相应的二进制、八进制、十六进制数。

解:略二进制数00000000~和0000000000~11分别可以代表多少个数?解:分别代表28=256和210=1024个数。

将下列个数分别转换成十进制数:(00)2,(1750)8,(3E8)16解:(00)2=(1000)10(1750)8=(1000)10(3E8)16=(1000)10将下列各数分别转换为二进制数:(210)8,(136)10,(88)16解:结果都为:()2将下列个数分别转换成八进制数:(111111)2,(63)10,(3F)16解:结果都为(77)8将下列个数分别转换成十六进制数:()2,(377)8,(255)10解:结果都为(FF)16转换下列各数,要求转换后保持原精度:解:()10=()10——小数点后至少取10位(0010 1011 0010)2421BCD=()2()余3循环BCD码=()2用下列代码表示(123)10,()2:解:(1)8421BCD码:(123)10=(0001 0010 0011)8421BCD()2=()10=(0001 0101)8421BCD(2)余3 BCD码(123)10=(0100 0101 0110)余3BCD()2=()10=(0100 1000)余3BCD已知A=(1011010)2,B=(101111)2,C=(1010100)2,D=(110)2(1)按二进制运算规律求A+B,A-B,C×D,C÷D,(2)将A、B、C、D转换成十进制数后,求A+B,A-B,C×D,C÷D,并将结果与(1)进行比较。

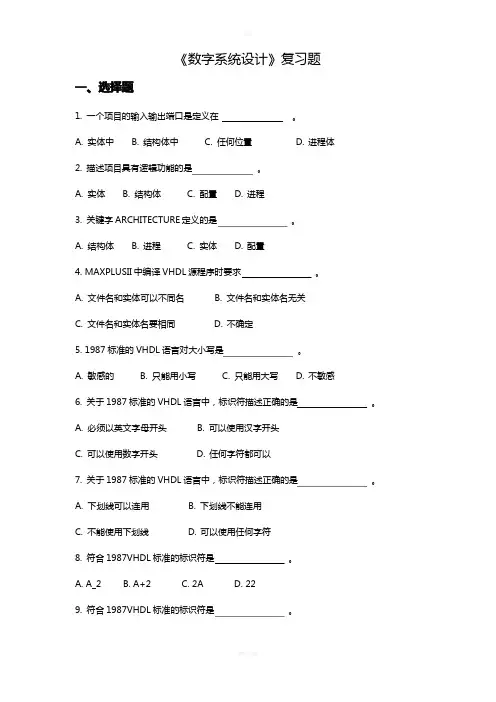

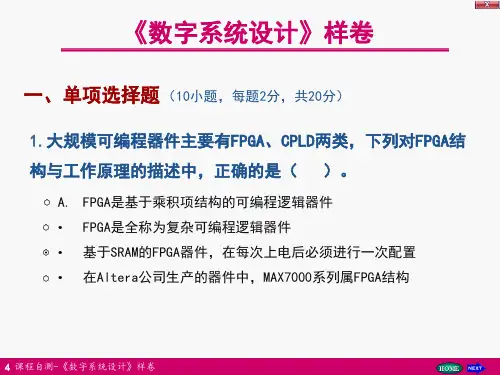

《数字系统设计》复习题一、选择题1.一个项目的输入输出端口是定义在。

A.实体中B.结构体中C.任何位置D.进程体2.描述项目具有逻辑功能的是。

A.实体B.结构体C.配置D.进程3.关键字ARCHITECTURE定义的是。

A.结构体B.进程C.实体D.配置4. MAXPLUSII中编译VHDL源程序时要求。

A.文件名和实体可以不同名B.文件名和实体名无关C.文件名和实体名要相同D.不确定5. 1987标准的VHDL语言对大小写是。

A.敏感的B.只能用小写C.只能用大写D.不敏感6.关于1987标准的VHDL语言中,标识符描述正确的是。

A.必须以英文字母开头B.可以使用汉字开头C.可以使用数字开头D.任何字符都可以7.关于1987标准的VHDL语言中,标识符描述正确的是。

A.下划线可以连用B.下划线不能连用C.不能使用下划线D.可以使用任何字符8.符合1987VHDL标准的标识符是。

A. A_2B. A+2C. 2AD. 229.符合1987VHDL标准的标识符是。

A. a_2_3B. a_2C. 2_2_aD. 2a10.不符合1987VHDL标准的标识符是。

A. a_1_inB. a_in_2C. 2_aD. asd_111.不符合1987VHDL标准的标识符是。

A. a2b2B. a1b1C. ad12D. %5012. VHDL语言中变量定义的位置是。

A.实体中中任何位置B.实体中特定位置C.结构体中任何位置D.结构体中特定位置13. VHDL语言中信号定义的位置是。

A.实体中任何位置B.实体中特定位置C.结构体中任何位置D.结构体中特定位置14.变量是局部量可以写在。

A.实体中B.进程中C.线粒体D.种子体中15.变量和信号的描述正确的是。

A.变量赋值号是:=B.信号赋值号是:=C.变量赋值号是<=D.二者没有区别16.变量和信号的描述正确的是。

D.二者没有区A.变量可以带出进程 B.信号可以带出进程 C.信号不能带出进程别17.关于VHDL数据类型,正确的是。

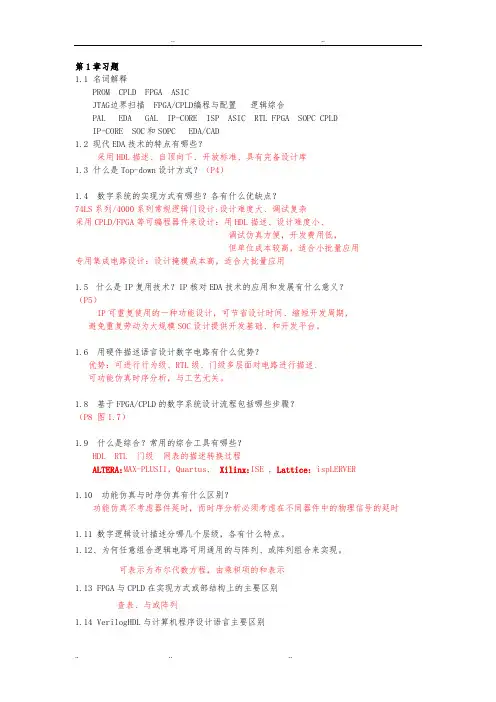

第1章习题1.1 名词解释PROM CPLD FPGA ASICJTAG边界扫描 FPGA/CPLD编程与配置逻辑综合PAL EDA GAL IP-CORE ISP ASIC RTL FPGA SOPC CPLDIP-CORE SOC和SOPC EDA/CAD1.2 现代EDA技术的特点有哪些?采用HDL描述、自顶向下、开放标准、具有完备设计库1.3 什么是Top-down设计方式?(P4)1.4 数字系统的实现方式有哪些?各有什么优缺点?74LS系列/4000系列常规逻辑门设计:设计难度大、调试复杂采用CPLD/FPGA等可编程器件来设计:用HDL描述、设计难度小、调试仿真方便,开发费用低,但单位成本较高,适合小批量应用专用集成电路设计:设计掩模成本高,适合大批量应用1.5什么是IP复用技术?IP核对EDA技术的应用和发展有什么意义?(P5)IP可重复使用的一种功能设计,可节省设计时间、缩短开发周期,避免重复劳动为大规模SOC设计提供开发基础、和开发平台。

1.6 用硬件描述语言设计数字电路有什么优势?优势:可进行行为级、RTL级、门级多层面对电路进行描述、可功能仿真时序分析,与工艺无关。

1.8 基于FPGA/CPLD的数字系统设计流程包括哪些步骤?(P8 图1.7)1.9 什么是综合?常用的综合工具有哪些?HDL RTL门级网表的描述转换过程ALTERA:MAX-PLUSII,Quartus, Xilinx:ISE , Lattice: ispLERVER1.10 功能仿真与时序仿真有什么区别?功能仿真不考虑器件延时,而时序分析必须考虑在不同器件中的物理信号的延时1.11 数字逻辑设计描述分哪几个层级,各有什么特点。

1.12、为何任意组合逻辑电路可用通用的与阵列、或阵列组合来实现。

可表示为布尔代数方程,由乘积项的和表示1.13 FPGA与CPLD在实现方式或部结构上的主要区别查表、与或阵列1.14 VerilogHDL与计算机程序设计语言主要区别(描述并行电路行为或结构、描述的串行指令流)1.15 简述“逻辑综合”功能作用。

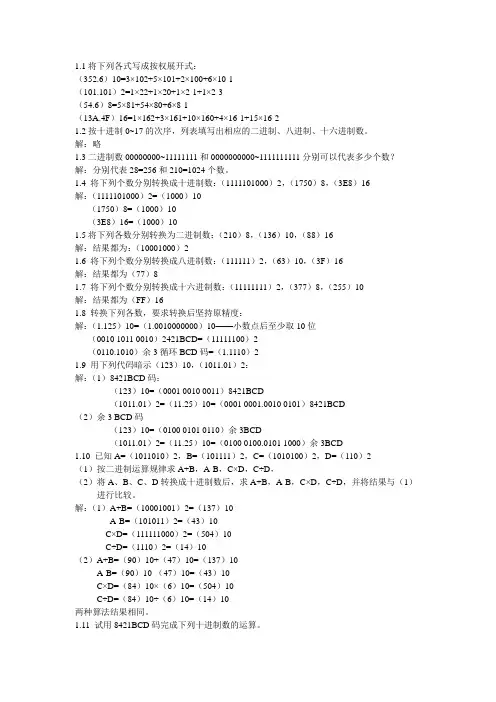

1.1将下列各式写成按权展开式:(352.6)10=3×102+5×101+2×100+6×10-1(101.101)2=1×22+1×20+1×2-1+1×2-3(54.6)8=5×81+54×80+6×8-1(13A.4F)16=1×162+3×161+10×160+4×16-1+15×16-21.2按十进制0~17的次序,列表填写出相应的二进制、八进制、十六进制数。

解:略1.3二进制数00000000~11111111和0000000000~1111111111分别可以代表多少个数?解:分别代表28=256和210=1024个数。

1.4 将下列个数分别转换成十进制数:(1111101000)2,(1750)8,(3E8)16解:(1111101000)2=(1000)10(1750)8=(1000)10(3E8)16=(1000)101.5将下列各数分别转换为二进制数:(210)8,(136)10,(88)16解:结果都为:(10001000)21.6 将下列个数分别转换成八进制数:(111111)2,(63)10,(3F)16解:结果都为(77)81.7 将下列个数分别转换成十六进制数:(11111111)2,(377)8,(255)10解:结果都为(FF)161.8 转换下列各数,要求转换后坚持原精度:解:(1.125)10=(1.0010000000)10——小数点后至少取10位(0010 1011 0010)2421BCD=(11111100)2(0110.1010)余3循环BCD码=(1.1110)21.9 用下列代码暗示(123)10,(1011.01)2:解:(1)8421BCD码:(123)10=(0001 0010 0011)8421BCD(1011.01)2=(11.25)10=(0001 0001.0010 0101)8421BCD(2)余3 BCD码(123)10=(0100 0101 0110)余3BCD(1011.01)2=(11.25)10=(0100 0100.0101 1000)余3BCD1.10 已知A=(1011010)2,B=(101111)2,C=(1010100)2,D=(110)2(1)按二进制运算规律求A+B,A-B,C×D,C÷D,(2)将A、B、C、D转换成十进制数后,求A+B,A-B,C×D,C÷D,并将结果与(1)进行比较。

《数据与系统》作业设计方案(第一课时)一、作业目标本节课的作业旨在帮助学生巩固数据与系统的基本概念,了解数据在系统中的重要性,并培养他们在实际生活中运用数据与系统解决问题的能力。

二、作业内容1. 阅读理解:学生需要阅读一篇关于数据在系统中的重要性的文章,并回答文章后面的问题。

问题涉及数据在系统中的作用、数据如何影响决策、数据驱动的决策如何影响社会等问题。

2. 案例分析:学生需要分析一个实际的数据驱动系统案例,例如一个智能交通管理系统或一个基于大数据的市场预测系统。

学生需要描述该系统的运作方式,数据在其中扮演的角色,以及数据如何影响系统的决策过程。

3. 小组讨论:学生以小组形式讨论数据在现实生活中的其他应用场景,如医疗、教育、金融等,并分享他们的见解和发现。

三、作业要求1. 独立完成:学生需独立完成阅读理解题目,并尽可能自己分析案例和进行讨论。

2. 团队合作:小组讨论应以团队合作的形式进行,每个成员都需要积极参与并贡献自己的观点。

3. 提交作业:每位学生需提交一份作业报告,包括他们的发现、分析过程和结论。

报告应以书面形式提交,并在规定时间内完成。

4. 按时反馈:教师应在作业提交后的一周内给予学生反馈,包括对作业的评价和建议,以便学生能够及时改进。

四、作业评价1. 准确性:评价学生是否准确地理解了数据与系统的重要性,以及他们是否正确地分析了案例。

2. 创新性:评价学生是否能提出新的、有创意的见解,以及他们在讨论中是否能提出新颖的想法。

3. 合作能力:评价学生在团队合作中是否能积极分享、倾听和协商,以及他们是否愿意采纳他人的意见。

4. 表达能力:评价学生的书面报告和讨论中是否能清晰、准确地表达自己的观点和想法。

五、作业反馈教师应在作业评价的基础上,给予学生针对性的反馈和建议。

对于普遍存在的问题,教师可以在课堂上统一讲解;对于个别学生的问题,教师可以单独交流,提供个性化的指导。

通过本次作业,学生将有机会深化对数据与系统的理解,培养解决问题的能力,并提高他们的团队合作和表达能力。

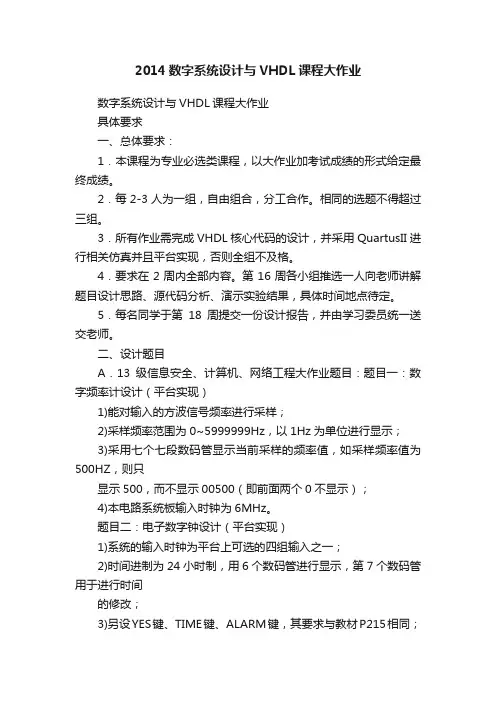

2014数字系统设计与VHDL课程大作业数字系统设计与VHDL课程大作业具体要求一、总体要求:1.本课程为专业必选类课程,以大作业加考试成绩的形式给定最终成绩。

2.每2-3人为一组,自由组合,分工合作。

相同的选题不得超过三组。

3.所有作业需完成VHDL核心代码的设计,并采用QuartusII进行相关仿真并且平台实现,否则全组不及格。

4.要求在2周内全部内容。

第16周各小组推选一人向老师讲解题目设计思路、源代码分析、演示实验结果,具体时间地点待定。

5.每名同学于第18周提交一份设计报告,并由学习委员统一送交老师。

二、设计题目A.13级信息安全、计算机、网络工程大作业题目:题目一:数字频率计设计(平台实现)1)能对输入的方波信号频率进行采样;2)采样频率范围为0~5999999Hz,以1Hz为单位进行显示;3)采用七个七段数码管显示当前采样的频率值,如采样频率值为500HZ,则只显示500,而不显示00500(即前面两个0不显示);4)本电路系统板输入时钟为6MHz。

题目二:电子数字钟设计(平台实现)1)系统的输入时钟为平台上可选的四组输入之一;2)时间进制为24小时制,用6个数码管进行显示,第7个数码管用于进行时间的修改;3)另设YES键、TIME键、ALARM键,其要求与教材P215相同;4)由于系统平台没有扬声器,对时间报警采用一个发光二极管闪烁30秒。

题目三:万年历设计(平台实现)1)能显示年、月、日、星期2)年、月、日均需可调(需要哪些按键自己设计),星期随按万年历,不用设置;3)系统默认时间为2000年01月01日星期6。

格式:00-01-014)数码管不够,默认显示年月日,设计一个切换按钮,切换显示星期,显示在最右一个数码管即可。

题目四:竞赛抢答器设计(平台实现)1)抢答器的输入路数为8路;(8位二进制输入)2)当主持人宣布开始(拨下A7键时为有效),抢答时当某一方先按下按键,其他键则失效;3)用一个数码管显示抢中的路编号,并开始进行60秒倒计时(用两个数码管显示),时间到用一指示灯进行闪烁提示;4)A7键回位后,进行下一轮抢答。

verilog数字系统设计教程习题答案verilog数字系统设计教程习题答案第二章1.Verilog HDL 既是一种行为描述语言,也是一种结构描述语言。

如果按照一定的规则和风格编写代码,就可以将功能行为模块通过工具自动转化为门级互联的结构模块。

这意味着利用Verilog语言所提供的功能,就可以构造一个模块间的清晰结构来描述复杂的大型设计,并对所需的逻辑电路进行严格的设计。

2.模块的基本结构由关键词module和endmodule构成。

3.一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。

其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。

4.Verilog HDL和VHDL作为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的结构和行为、支持逻辑设计中层次与领域的描述、可借用高级语言的精巧结构来简化电路的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、便于文档管理、易于理解和设计重用。

5.不是6.将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

7.综合工具可以把HDL变成门级网表。

这方面Synopsys工具占有较大的优势,它的Design Compile是作为一个综合的工业标准,它还有另外一个产品叫Behavior Compiler,可以提供更高级的综合。

另外最近美国又出了一个软件叫Ambit,据说比Synopsys的软件更有效,可以综合50万门的电路,速度更快。

今年初Ambit被Cadence公司收购,为此Cadence 放弃了它原来的综合软件Synergy。

大工14秋《数字电路与系统》在线作业(共五则)第一篇:大工14秋《数字电路与系统》在线作业大工14秋《数字电路与系统》在线作业1试卷总分:100测试时间:--试卷得分:100单选题多选题判断题包括本科在内的各校各科复习资料,可以联系屏幕右上的“文档贡献者”一、单选题(共 6 道试题,共 30 分。

)得分:30V 1.十六进制数AC转换为二进制数是()。

A.10101100B.10001100C.10011101D.11011001.满分:5 分得分:52.由卡诺图中小格的相邻性得知,相邻小格有()个变量不同。

A.1B.2C.3D.4.满分:5 分得分:53.实现与运算后再进行非运算的复合逻辑门电路称为()。

A.异或门B.同或门C.或非门D.与非门.满分:5 分得分:54.十进制数5等于下列哪项8421B码?()A.0011B.0100C.0101D.1001.满分:5 分得分:55.在数字电路系统中,为了简化运算电路,减法运算用()来实现。

A.反码相加B.补码相加C.加法和移位D.减法和移位.满分:5 分得分:56.1+A=()A.AB./AC.0D.1.满分:5 分得分:5二、多选题(共 6 道试题,共 30 分。

)得分:30V 1.下列关于二进制数的说法正确的是()。

A.0数码对应电路中的低电平状态B.0数码对应电路中的高电平状态C.1数码对应电路中的低电平状态D.1数码对应电路中的高电平状态满分:5 分得分:52.TTL与非门中不用的输入端如何处理?()A.接+5V高电平B.与使用端并联C.接地D.悬空满分:5 分得分:53.一个不带符号的二进制数,如何求其补码?()A.补码等于其二进制数原码B.二进制数原码逐位求反C.二进制数反码最低有效位加1D.二进制数低位(包括小数部分)的第一个“1”右边保持不变(包括此1),左边依次求反满分:5 分得分:54.下列关于数字量的说法正确的是()。

A.在时间上连续B.在数值上连续C.在时间上离散D.在数值上离散满分:5 分得分:55.下列属于逻辑代数的基本运算的是()。

《数字系统设计》实验报告班级_______电信2班_________________ 姓名____潘俊俊_____________________ 学号___1309121091__________________实验1 组合电路的设计实验目的:熟悉ISE的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

实验内容:首先利用ISE完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出仿真波形。

实验程序:ENTITY mux21a ISPORT (a, b, s: IN BIT;Y: OUT BIT);END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINPROCESS (a, b, s)BEGINIF s='0' THEN y<=a; ELSE y<=b;END IF;END PROCESS;END ARCHITECTURE one;实验结果:1、综合电路图2、 仿真时序图实验分析:在0—275ns 内,s=0, 则输出a 波形;在275—685ns 内,s=1,则输出b 波形;在685ns 以后,s=0, 则输出a 波形;仿真结果与实验要求一致,故仿真结果正确。

实验2 时序电路的设计实验目的:熟悉ISE的VHDL文本设计过程,学习简单时序电路的设计、仿真和测试。

实验任务:设计一个带使能输入及同步清0的增1/减1的3位计数器,并仿真。

实验程序:Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity up_down isPort(clk,rst,en,up: in std_logic;Sum: out std_logic_vector(2 downto 0);Cout: out std_logic);End;Architecture a of up_down isSignal count: std_logic_vector(2 downto 0);BeginProcess(clk,rst)BeginIf rst=’0’ thenCount<=(others=>’0’);Elsif rising_edge(clk) thenIf en=’1’ thenCase up isWhen ‘1’ => count<=count+1;When others =>count<=count-1;End case;End if;End if;End process;Sum<=count;Cout <=’1’ when en=’1’ and ((up=’1’ and count=7) or (up=’0’ and count=0)) else ‘0’;End;实验结果:1、综合电路图2、仿真时序图实验分析:当rst=’0’ ,输出被清零;否则(rst=1,en=1)当up=1时,输出count<=count+1,若up=0,输出count<=count-1。

第1章习题1.1 名词解释PROM CPLD FPGA ASICJTAG边界扫描FPGA/CPLD编程与配置逻辑综合PAL EDA GAL IP-CORE ISP ASIC RTL FPGA SOPC CPLDIP-CORE SOC和SOPC EDA/CAD1.2 现代EDA技术的特点有哪些?采用HDL描述、自顶向下、开放标准、具有完备设计库1.3 什么是Top-down设计方式?(P4)1.4 数字系统的实现方式有哪些?各有什么优缺点?74LS系列/4000系列常规逻辑门设计:设计难度大、调试复杂采用CPLD/FPGA等可编程器件来设计:用HDL描述、设计难度小、调试仿真方便,开发费用低,但单位成本较高,适合小批量应用专用集成电路设计:设计掩模成本高,适合大批量应用1.5什么是IP复用技术?IP核对EDA技术的应用和发展有什么意义?(P5)IP可重复使用的一种功能设计,可节省设计时间、缩短开发周期,避免重复劳动为大规模SOC设计提供开发基础、和开发平台。

1.6 用硬件描述语言设计数字电路有什么优势?优势:可进行行为级、RTL级、门级多层面对电路进行描述、可功能仿真时序分析,与工艺无关。

1.8 基于FPGA/CPLD的数字系统设计流程包括哪些步骤?(P8 图1.7)1.9 什么是综合?常用的综合工具有哪些?HDL→RTL→门级→网表的描述转换过程ALTERA:MAX-PLUSII,Quartus, Xilinx:ISE , Lattice: ispLERVER1.10 功能仿真与时序仿真有什么区别?功能仿真不考虑器件延时,而时序分析必须考虑在不同器件中的物理信号的延时1.11 数字逻辑设计描述分哪几个层级,各有什么特点。

1.12、为何任意组合逻辑电路可用通用的与阵列、或阵列组合来实现。

可表示为布尔代数方程,由乘积项的和表示1.13 FPGA与CPLD在实现方式或内部结构上的主要区别查表、与或阵列1.14 VerilogHDL与计算机程序设计语言主要区别(描述并行电路行为或结构、描述的串行指令流)1.15 简述“逻辑综合”功能作用。