两个多位十进制数相加的实验

- 格式:doc

- 大小:109.00 KB

- 文档页数:7

深圳大学实验报告课程名称:微机原理及应用实验实验项目名称:多位十进制数加法器设计学院:物理科学与技术学院专业:应用物理指导教师:报告人:学号:班级:应用物理班实验时间:2015-10-19实验报告提交时间:2015-11-02教务处制五、程序说明(预习)七、实验源程序清单(实验后以电子报告形式存储到指定位置)1.源程序路径及文件名:ADD2.ASM ADD1.ASM2.可执行程序路径及文件名:八、上机调试情况说明EMU8086:一:没有键盘录入1.结果显示如下:2.程序运行时的各段地址:3.两个子程序IP入口:4.改变两个加数数值5.子程序格式及其调用方法和宏汇编区别子程序格式:子程序名称PROC NEAR ; 子程序定义; …子程序内容RET ;子程序返回子程序名称ENDP ;子程序结束调用格式:CALL 子程序名称注意事项:1、子程序不能直接传递参数,需要自行定义变量。

2、注意保护现场和恢复现场。

宏汇编与子程序的区别:1、宏汇编有宏展开,子程序没有2、宏汇编可以传递参数。

二:键盘录入DOS:例如:250+250=500例如:62142+63123=125265九、实验结果与分析结果如下:十、实验总结(必备部分,评分重要依据之一)本次实验实则是对实验二的加强巩固基础上,进行更加友好的人机交互设计;通过本次实验不仅在程序中首先把两个加数固定,在实验二的基础上扩展位数,考虑到最高位进位的情况,并最终得出正确结果;后来又通过键盘录入两个加数,增加了人机交互的设计,如此一来,更加加深了对寄存器的使用,汇编语言宏定义,子程序调用以及DOS功能调用的学习。

同时,通过本次实验的学习,更加熟练了EMU8086工具的使用,也把理论课上学习到的汇编操作指令实际操作,对汇编语言的风格加深认识。

MOV DL,BLINT 21HCRLFJMP BEGINERROR:CRLFMOV AH,09H ;显示输入错误LEA DX,STRING3INT 21HCRLFJMP BEGINEXIT:CRLFMOV AH,09H ;显示成功退出LEA DX,STRING4INT 21HMOV AH,4CHINT 21HCODE ENDSEND START(2)请问你的程序能否处理加数和被加数都介于0~65535范围但计算结果超出该范围的情况?如何改进?可以,如图:主要考虑到最高位是否进位,可以设置一个进位变量加以判断。

微机原理实验报告-两个多位十进制数相加的实验等微机原理实验报告班级:学号:姓名:实验一两个多位十进制数相加的实验一、实验目的学习数据传送和算术运算指令的用法熟悉在PC机上建立、汇编、链接、调试和运行汇编语言程序的过程。

二、实验内容将两个多位十进制数相加,要求被加数和加数均以ASCII码形式各自顺序存放在以DATA1、DATA2为首的5个内存单元中(低位在前),结果送回DATA1处。

三、程序流程图图3-1四、参考程序清单DATA SEGMENTDATA1 DB 33H,39H,31H,37H,34H;被加数DATA1END E QU $-1DATA2 DB 34H,35H,30H,38H,32H;加数DATA2END EQU $-1SUM DB 5 DUP(?)DATA ENDSSTACK SEGMENTSTA DB 20 DUP(?)TOP EQU LENGTH STASTACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATA START: MOV AX,DATAMOV DS,AXMOV AX,STACKMOV SS,AXMOV AX,TOPMOV SP,AXMOV SI,OFFSET DATA1ENDMOV DI,OFFSET DATA2ENDCALL ADDAMOV AX,4C00HINT 21HADDA PROC NEARMOV DX,SIMOV BP,DIMOV BX,05HAD1: SUB BYTE PTR [SI],30HSUB BYTE PTR [DI],30HDEC SIDEC DIDEC BXJNZ AD1MOV SI,DXMOV DI,BPMOV CX,05HCLCAD2: MOV AL,[SI]MOV BL,[DI]ADC AL,BLAAAMOV [SI],ALDEC SIDEC DILOOP AD2MOV SI,DXMOV DI,BPMOV BX,05HAD3: ADD BYTE PTR [SI],30HADD BYTE PTR [DI],30HDEC SIDEC DIDEC BXJNZ A D3RETADDA ENDP CODE ENDSEND S TART五、实验结果分析我们计算的结果是:84256他们结果是一样的。

十进制数的加法与减法在我们日常生活中,十进制数是我们最常用的数制。

无论是购物、计算时间还是进行金融交易,我们都需要使用十进制数进行计算。

而在进行十进制数的加法和减法运算时,我们需要掌握一些基本的方法和技巧。

一、十进制数的加法十进制数的加法是我们最常见的运算之一。

下面,我将介绍一些常用的加法方法。

1. 垂直加法法则垂直加法法则是我们最常用的加法方法。

它的基本原理是将两个数的相同位数的数字对齐,然后从右向左逐位相加。

如果某一位的和大于等于10,就需要进位到更高位。

例如,计算1234 + 5678:```1234+ 5678------```首先,从右向左逐位相加:4 + 8 = 12,需要进位;3 + 7 + 进位 = 11,同样需要进位;2 + 6 + 进位 = 9;1 + 5 + 进位 = 7。

最终的结果是6912。

2. 补数法补数法是一种简化计算的方法。

它的基本原理是将一个数的补数与另一个数相加,然后再减去被加数的补数。

例如,计算47 + 58:首先,找到47的补数,即53。

然后,将53与58相加,得到111。

最后,减去47的补数53,得到58。

所以,47 + 58 = 111 - 53 = 58。

二、十进制数的减法十进制数的减法是加法的逆运算。

下面,我将介绍一些常用的减法方法。

1. 借位减法法则借位减法法则是我们最常用的减法方法。

它的基本原理是将两个数的相同位数的数字对齐,然后从右向左逐位相减。

如果被减数小于减数,就需要向高位借位。

例如,计算9876 - 5432:```9876- 5432------```首先,从右向左逐位相减:6 - 2 = 4;7 - 3 = 4;8 - 4 = 4;9 - 5 = 4。

最终的结果是4444。

2. 补数法补数法也可以用于减法运算。

它的基本原理是将一个数的补数与另一个数相加,然后再减去被减数的补数。

例如,计算98 - 57:首先,找到98的补数,即2。

然后,将2与57相加,得到59。

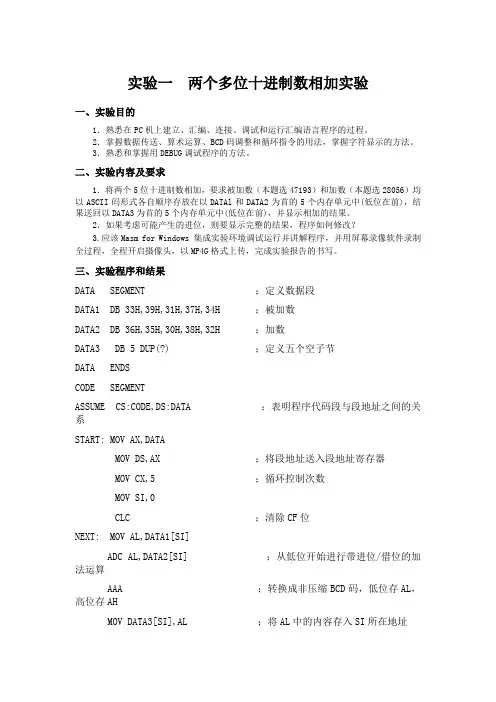

实验一两个多位十进制数相加实验一、实验目的1.熟悉在PC机上建立、汇编、连接、调试和运行汇编语言程序的过程。

2.掌握数据传送、算术运算、BCD码调整和循环指令的用法,掌握字符显示的方法。

3.熟悉和掌握用DEBUG调试程序的方法。

二、实验内容及要求1.将两个5位十进制数相加,要求被加数(本题选47193)和加数(本题选28056)均以ASCII码形式各自顺序存放在以DATAl和DATA2为首的5个内存单元中(低位在前),结果送回以DATA3为首的5个内存单元中(低位在前),并显示相加的结果。

2.如果考虑可能产生的进位,则要显示完整的结果,程序如何修改?3.应该Masm for Windows 集成实验环境调试运行并讲解程序,并用屏幕录像软件录制全过程,全程开启摄像头,以MP4G格式上传,完成实验报告的书写。

三、实验程序和结果DATA SEGMENT ;定义数据段DATA1 DB 33H,39H,31H,37H,34H ;被加数DATA2 DB 36H,35H,30H,38H,32H ;加数DATA3 DB 5 DUP(?) ;定义五个空子节DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA ;表明程序代码段与段地址之间的关系START: MOV AX,DATAMOV DS,AX ;将段地址送入段地址寄存器MOV CX,5 ;循环控制次数MOV SI,0CLC ;清除CF位NEXT: MOV AL,DATA1[SI]ADC AL,DATA2[SI] ;从低位开始进行带进位/借位的加法运算AAA ;转换成非压缩BCD码,低位存AL,高位存AHMOV DATA3[SI],AL ;将AL中的内容存入SI所在地址INC SILOOP NEXTMOV SI,5DISP: ADD DATA3[SI-1],30H ;将16进制数转换为ASCII码表示 MOV DL,DATA3[SI-1]MOV AH,2INT 21HDEC SI ;偏移地址自减JNZ DISPMOV AH,4CHINT 21H ;终断调用CODE ENDS ;结束程序代码段END START(页面不足请附页)四、实验总结和体会通过本次实验我对汇编有了更加具体的认识,也明白了汇编中各个寄存器的作用及寄存器间是怎样联系的,也初步明白了什么是断地址,什么是堆栈,以及汇编的基本结构和循环结构的基本运用,但是我了解的只是初步的,汇编中还有很多我不明白和不了解的地方,最重要的是汇编语句掌握不牢固,不能很快的知道一些专用的汇编语句的意义,这方面还是比较薄弱的,还需要在今后的实验和学习中不断的学习和练习。

十进制数的运算了解十进制数的运算法则十进制数是我们日常生活中最为常见的数,它由0、1、2、3、4、5、6、7、8、9这十个数字组成。

在我们进行十进制数的运算时,需要了解一些基本的运算法则。

本文将介绍十进制数的运算法则,包括加法、减法、乘法和除法。

一、加法运算法则十进制数的加法是最简单的运算之一,我们只需要按照位数对应相加即可。

当两个十进制数相加时,从右往左一位一位相加,并保留进位。

如果最高位有进位,需要在结果的最左侧加上进位的值。

例如,计算76 + 39的结果:```76+39----115```在这个例子中,个位7和9相加得到16,十位7和十位3相加得到10,十位的进位需要加到百位。

因此,最后结果为115。

二、减法运算法则减法是加法的逆运算,同样需要按照位数进行计算。

当两个十进制数相减时,从右向左一位一位相减,并借位。

如果被减数小于减数,则需要向高位借位,被借位的数减去1。

例如,计算96 - 42的结果:```96-42----54```在这个例子中,个位6减去2得到4,十位9减去4得到5。

因为四十位的6小于被减数的2,所以需要向百位借位,并在被借位的6上减去1,变为5。

所以最后结果为54。

三、乘法运算法则十进制数的乘法运算需要使用到乘法表格。

我们需要按照列竖直相乘的方式进行计算,并将每一列的积相加。

例如,计算27 × 36的结果:```27------162 (7×6)+ 810 (7×30)------972```在这个例子中,个位7与个位6相乘得到42,十位7与十位3相乘得到21,然后将这两个积相加得到162。

接下来,个位7与十位3相乘得到21,并将得到的积补0,得到810。

最后,将162与810相加得到最终的结果972。

四、除法运算法则十进制数的除法是比较复杂的运算,需要进行多次计算才能得到商和余数。

我们需要按照竖式除法的方式进行计算。

例如,计算648 ÷ 9的商和余数:```72------9 |648----28```在这个例子中,我们从左向右按位进行计算。

实验三两个多位数十进制数相加的实验一、实验目的学习数据传送和算术运算指令的用法。

熟悉在PC机上建立、汇编、链接、调试和运行8086汇编语言程序的过程。

二、实验内容及程序将两个多位数十进制数相加,要求被加数和加数均以ASCⅡ码形式各自顺序存放在以DATA1和DA TA2为首的5个内存单元中,且低位在前,结果送回DA TA1处。

编程要求与提示:[1] 两个加数均以压缩(组合)十进制数形式存放在ADD1和ADD2为首址的存贮器单元。

[2] 和以压缩十进制数的形式存入SUM以下单元。

[3] 将和送到屏幕显示部分功能的实现采用子程序的形式。

[4] 实验步骤如下:a. 用全屏幕编辑软件建立源程序。

b.用masm.exe汇编程序对源程序进行汇编,形成目标程序。

c. 用link.exe连接程序对目标程序进行连接形成可执行文件。

d. 用DEBUG对连接通过的可执行程序进行调试。

三、参考流程STACK SEGMENT STACK 'STACK'DW 100H DUP(?)STACK ENDSDA TA SEGMENTADD1 DD 12678532H ;加数以组合十进制形式存放在双字单元ADD2 DD 21736543HSUM DD ?DA TA ENDSCODE SEGMENTASSUME CS:CODE,DS:DA TA,ES:DATA,SS:STACKSTART: MOV AX,DA TAMOV DS,AXMOV ES,AXMOV AX,STACKMOV SS,AXLEA SI,ADD1LEA DI,ADD2LEA BX,SUMMOV AL,[SI]ADD AL,[DI] ;最低位的一个字节相加DAA ;加法组合BCD码调整MOV [BX],AL ;结果存放在SUM第一个字节MOV AL,[SI+1] ;第二个字节相加ADC AL,[DI+1]DAAMOV [BX+1],ALMOV AL,[SI+2]ADC AL,[DI+2]DAAMOV [BX+2],ALMOV AL,[SI+3]ADC AL,[DI+3]DAAMOV [BX+3],ALMOV DL,00 ;最高位字节有进位则显示"01"ADC DL,00CALL DISPSUMMOV AH,4CH ;返回DOSINT 21HDISPSUM PROC NEAR ;结果显示子程序PUSH AXPUSH BXPUSH CXPUSH SIMOV SI ,4PUSH DXMOV CX,5LAB:PUSH CXPUSH BXMOV AL,DLMOV BL,DLMOV CL,4 ;显示高位字节SHR AL,CLADD AL,30HMOV AH,02MOV DL,ALINT 21H ;显示一位字符AND BL,0FH ;显示低位字节ADD BL,30HMOV AH,02MOV DL,BLINT 21HPOP BXPOP CXDEC SIMOV DL,[BX][SI] ;结果显示LOOP LABPOP DXPOP SIPOP CXPOP BXPOP AXRETDISPSUM ENDPCODE ENDSEND START。

多位数加法的迁移问题研究

人们用手指计数。

但是手指加起来就只有十个,超过十怎么办呢?

“用脚趾吧”,一个古代人说道。

“呃,脚的话有点臭”,众人表示还是算了吧。

于是他们想出一个办法:

让两个人数数,一个人叫“个个”,另一个人叫“十十”。

个个用手指从1数到10。

就让十十用手指做个1。

个个用手指做个0。

当个个再从1数到10。

就让十十用手指做个2。

个个再用手指做0。

每当个个的10个手指全用满了。

就让十十加上1个手指。

同时个个把手指还原成0。

最终,

十十的10个手指用满了。

这就到了100。

也可以和孩子扩展一下,3个这么做就可以数到1000。

十进制数的计算与运用十进制数是我们日常生活中最常使用的数制,它由0~9共10个数字符号组成。

在这篇文章中,我们将探讨十进制数的计算方法以及它在实际应用中的运用。

一、十进制数的计算方法在十进制数中,每一位的权重都是10的次方。

例如,对于数码732,7代表百位,3代表十位,2代表个位。

那么732可以表示为(7 × 10^2)+ (3 × 10^1) + (2 × 10^0)。

因此,我们可以通过将各位数与对应的权重相乘,然后将结果相加,来计算十进制数。

十进制数的计算方法也包括四则运算:加法、减法、乘法和除法。

每一种运算都可以通过对应的规则进行处理。

1. 加法在十进制数的加法中,我们将两个数按照各位对齐,然后从右往左逐位相加。

如果某一位的结果大于9,则需要向左一位进位。

进位后,继续相加直到最高位。

2. 减法减法是加法的逆运算。

我们将被减数和减数按照各位对齐,从右往左逐位相减。

如果某一位的结果小于0,则需要向左一位借位。

借位后,继续相减直到最高位。

3. 乘法在十进制数的乘法中,我们将两个数按照各位对齐,然后从右往左逐位相乘,并将结果累加。

每一位乘积都需要乘以对应的权重。

4. 除法除法是乘法的逆运算。

我们将被除数和除数按照各位对齐,从左往右逐位进行除法运算。

每一位的结果都需要乘以对应的权重。

二、十进制数的运用十进制数在日常生活中有着广泛的应用。

以下是一些例子:1. 货币和金融我们常用十进制数来计算货币和金融事务。

无论是在购物、理财还是计算利息,十进制数都是必不可少的工具。

2. 计量单位绝大多数计量单位都是以十进制数为基础。

例如,我们用十进制数去计算时间、长度、体积、重量等物理量。

3. 统计和数据分析十进制数在统计和数据分析中扮演着重要的角色。

通过对数据进行收集、整理和分析,我们可以得出许多有关人口、经济、社会等方面的重要结论。

4. 科学和工程在科学和工程领域,十进制数被广泛用于各种计算和测量。

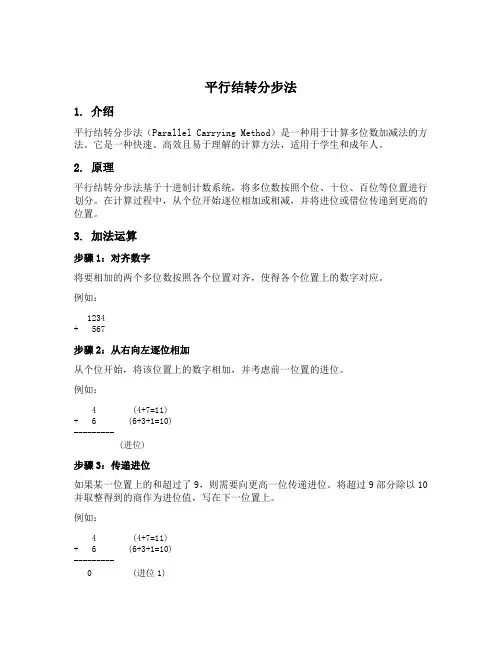

平行结转分步法1. 介绍平行结转分步法(Parallel Carrying Method)是一种用于计算多位数加减法的方法。

它是一种快速、高效且易于理解的计算方法,适用于学生和成年人。

2. 原理平行结转分步法基于十进制计数系统,将多位数按照个位、十位、百位等位置进行划分。

在计算过程中,从个位开始逐位相加或相减,并将进位或借位传递到更高的位置。

3. 加法运算步骤1:对齐数字将要相加的两个多位数按照各个位置对齐,使得各个位置上的数字对应。

例如:1234+ 567步骤2:从右向左逐位相加从个位开始,将该位置上的数字相加,并考虑前一位置的进位。

例如:4 (4+7=11)+ 6 (6+3+1=10)---------(进位)步骤3:传递进位如果某一位置上的和超过了9,则需要向更高一位传递进位。

将超过9部分除以10并取整得到的商作为进位值,写在下一位置上。

例如:4 (4+7=11)+ 6 (6+3+1=10)---------0 (进位1)步骤4:继续相加继续从左到右逐位相加,重复步骤2和步骤3,直到所有位置上的数字都相加完毕。

例如:4 (4+7=11)+ 6 (6+3+1=10)---------0 (进位1)1 (进位1+2=3)步骤5:得到最终结果当所有位置上的数字都相加完毕后,得到的结果即为最终的和。

例如:4 (4+7=11)+ 6 (6+3+1=10)---------0 (进位1)1 (进位1+2=3)3因此,1234 + 567 = 1801。

4. 减法运算减法运算与加法运算类似,只需在第二步中将对应位置上的数字相减即可。

如果被减数小于减数,则需要向更高一位借位,并将借位值写在下一位置上。

以下是平行结转分步法进行减法运算的步骤示例:例如:8 (8-5=3)- 4 (4-2=2)---------0 (借位1)3因此,8 - 4 = 32。

5. 总结平行结转分步法是一种简单而高效的多位数加减法计算方法。

深圳大学实验报告课程名称: _________ 微机原理及应用实验实验项目名称:数据传送及两个多位十进制数相加学院_________________________________专业__________________________________________________指导教师: __________________________________________________报告人:_学号:班级: ________________实验时间: ________________________________________实验报告提交时间: ___________________________________________教务处制、实验名称:数据传送及两个多位十进制数相加二、实验目的(1)学习数据传送和算术运算指令的用法。

(2)熟悉在PC机上建立、汇编、链接、调试和运行 8088汇编语言程序的过程。

三、实验内容将两个多位十进制数相加。

要求被加数均以ASCII码形式各自顺序存放在以DATAI和DATA2为首的5个内存单元中(低位在前),结果送回DATAI处。

四、实验电路及连线(硬件实验)此实验属于软件实验,故无硬件实验的电路及连线。

五、程序说明(预习)包括程序功能,程序框图,算法说明及所用到的寄存器等。

功能:将被加数和加数分别显示,接着运行加法运算,然后将结果显示出来。

算法说明:①定义数据段:定义被加数和加数,且要使其用ASCII码以十六进制之间的转换;②定义堆栈段,并给SP_TO单元赋初值0;③定义代码段,并将源代码放在里面首先,编写主程序;接着,编写显示、回车换行和加法运算的子程序。

④程序结束。

所用到的寄存:AX SS、CS、DS ES、SI、SP、DI六、源程序清单(预习);DATAS SEGMENT ; DATA1 DB 33H,32H,38H,34H,37H DATA2 DB 34H,35H,39H,37H,31H DATAS ENDS数据段;定义DATA1为被加数;定义DATA2为加数STACKS SEGMENT ; 堆栈段STA DB 64 DUP(O) ; 为STA预留64个字节的存储空间SP_TOP DB 0 ; 定义SP_TO单元的数值为0 STACKS ENDSCODES SEGMENT ; 代码段ASSUME CS:CODES,DS:DATAS,ES:DATAS,SS:STACKSSTART:MOV AX,DATASMOV DS,AX ; 设置数据段MOV AX,STACKSMOV SS,AX ; 设置堆栈段LEA SP,SP_TOP ; 设置栈顶指针MOV SI,OFFSET DATA1 ; 把DATA1偏移量地址赋予SIMOV BX,05CALL DISPL ; 显示被加数CALLCRLF ; 回车、换行MOV SI,OFFSET DATA2 ; 把DATA2偏移量地址赋予SIMOV BX,05CALL DISPL ; 显示加数CALLCRLF ; 回车、换行MOV DI,OFFSET DATA1 ; 把DATA1偏移量地址赋予DICALL ADDA ; 调用ADDAF程序,实行加法运算MOV BX,05CALL DISPL ; 显示结果CALLCRLF ; 回车、换行MOV AX,4C00H ;INT 21H ; 调用DOS21H功能,返回CRLF PROC NEAR ; 回车、显示功能过程定义,属性为 NEAR MOV DL,0DH ; 把回车的ASCII码0DH传给DLMOV AH,02H ; 送DOS的中断调用功能号INT 21H ; DOS 的中断调用MOV DL,0AH ; 把换行的ASCII码0AH传给DLMOV AH,02H ;INT 21H ; DOSRET ; CRLF ENDP ;送DOS的中断调用功能号的中断调用返回完成过程定义DISPL PROC NEAR DSL: MOV AH,02 ;MOV DL,[SI+BX-1];INT 21H ; DOSDEC BX ;BXJNZ DSL ;RET ; DISPL ENDP ; 显示功能过程定义,属性为NEAR 送显示功能号显示字符串中一字符的中断调用减1,修改偏移量如果BX未减到零,跳到DSL执行指令返回完成显示功能子程序定义ADDA PROC NEARMOV DX,SIMOV BP,DIMOV BX,05实行加法运算子程序过程定义,属性为TRAN_HEX: SUB BYTE PTR[SI+BX-1],30H ;把 ASCII 码数转化为十六进制SUB BYTE PTR[DI+BX-1],30HDEC BX ;BXJNZ TRAN_HEXMOV SI,DXMOV DI,BPMOV CX,05 ;CLC ;THE_ADD: MOV AL,[SI]MOV BL,[DI]ADC AL,BL ;AAA ;MOV [SI],AL ;INC SI ;SIINC DI ;DILOOP THE_ADD ;MOV SI,DXMOV DI,BPMOV BX,05 减1,修改偏移量;如果BX未减到零,跳到TRAN_HEX执行指令包括进位,共5位进位标志位 CF清零 (clear carry flag )带进位相加,把结果存在AX进行AAA调整,非结合BCD码的加法调整结果送被加数区加1加1 (指向下一位)循环TRAN_ASCI: ADD BYTE PTR[SI+BX-1],30HADD BYT田TR[DI+BX-1],30H ; 使用PTR转换属性并相加,将十六进制数转化为ASCII表示DEC BX ; BX 减1,修改偏移量RET ; 返回ADDA ENDP ;加法子程序定义完成CODES ENDS ; 代码段完成END START七、实验源程序清单(实验后以电子报告形式存储到指定位置)1.源程序路径及文件名:实验三\l3.asm2.可执行程序路径及文件名:实验三\l3.exe;八、上机调试情况说明1.上机调试步骤A .通过dos对pts3.asm文件进行操作。

微机原理实验报告专业:工业工程姓名:刘雷学号:089094082指导老师:陈全目录软件实验一汇编语言程序的调试与运行 (3)一.实验目的 (3)二.实验内容 (3)三.程序框图 (3)四.程序清单 (4)五.调试步骤 (6)六.思考题 (6)软件实验二分支程序设计 (14)一.实验目的 (14)二.实验内容与要求 (14)三.程序框图 (15)四.程序清单: (16)五.思考题 (17)软件实验三循环程序设计 (18)一.实验目的 (18)二.实验内容与要求 (18)三.程序框图 (19)四.程序清单(将程序补充完整) (20)软件实验四子程序结构 (22)一.实验目的 (22)二.实验内容与要求 (22)三.程序框图: (23)四.部分程序清单 (23)五.步骤 (25)六.思考题 (25)软件实验一汇编语言程序的调试与运行一.实验目的1.学习数据传送和算术运算指令的用法2.熟悉在PC机上编辑、汇编、连接、调试和运行汇编语言程序的过程。

二.实验内容将两个多位十进制数相加,要求被加数和加数均以ASCII码形式各自顺序存放在DATA1和DA TA2为首的5个内存单元中,结果送回DATA1处。

三.程序框图图1.1 两个多位十进制相加程序流程图四.程序清单DISP MACRO XMOV DL,X ;要显示的字符送DL寄存器MOV AH,02H ;DOS功能调用号是02HINT 21H ;21H中断程序是DOS功能调用ENDMDATA SEGMENTDATA1 DB '12732'DATA2 DB '06815'N EQU $-DA TA2DATA ENDSSTACK SEGMENT STACKSTA DB 20 DUP (?)TOP EQU $-STASTACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK,ES:DA TA START:MOV AX,DA TAMOV DS,AXMOV AX,STACKMOV SS,AXMOV AX,TOPMOV SP,AXLEA SI,DATA1 ;☆MOV BX,0MOV CX,NCALL DISPL ;显示被加数DISP '+'LEA SI,DATA2MOV BX,0MOV CX,NCALL DISPL ;显示加数DISP '='LEA DI,DA TA1MOV CX,NCALL ADDA ;调用加法子程序LEA SI,DATA1MOV BX,0MOV CX,NCALL DISPL ;显示运算结果DISP 0DHDISP 0AHMOV AX,4C00HINT 21HDISPL PROC ;显示子程序DS1: MOV AH,02HMOV DL,[SI+BX]INT 21HINC BXLOOP DS1RETDISPL ENDPADDA PROC ;加法子程序PUSH CXMOV BX,0AD1: SUB BYTE PTR [SI+BX],30HSUB BYTE PTR [DI+BX],30HINC BXLOOP AD1POP CXPUSH CXMOV BX,N-1 ;☆☆CLCAD2: MOV AL,[SI+BX]ADC AL,[DI+BX]AAAMOV [DI+BX],ALDEC BXLOOP AD2POP CXPUSH CXMOV BX,0 ;☆☆☆AD3: ADD BYTE PTR [DI+BX],30HINC BXLOOP AD3POP CXRET ;☆☆☆☆ADDA ENDPCODE ENDSEND START五.调试步骤1.编辑源程序,建立一个以后缀为.ASM的文件.2.汇编源程序,检查程序有否错误,有错时回到编辑状态,修改程序中错误行。

学生实验报告(2010 —2011 学年第 2 学期)课程名称:微机原理与接口技术开课实验室:205教室 2011年5 月10日一.实验目的1.学习数据传送和算术运算指令的用法。

2..熟悉在PC机上建立、汇编、链接、调试和运行8088汇编语言程序的过程。

二、实验原理及基本技术路线图或实验内容(方框原理图或程序流程图)1、实验内容将两个多位十进制数相加。

要求被加数均以ASCII码形式各自顺序存放在以DA TA1和DATA2为首的5个内存单元中(低位在前),结果送回DATA1处。

三、所用仪器、材料和软件(设备和软件名称、型号、规格等)所用的软件为Masm for windows集成实验环境2009四、实验方法、步骤1、编写程序代码2、运行程序,修改错误代码3、再次运行代码直至运行出正确结果五、源码程序编制及分析注释CRLF MACRO ;宏定义指令(回车执行程序) MOV DL,0DH ;回车MOV AH,02H ; 2号调用,显示回车INT 21HMOV DL,0AH ;换行MOV AH,02H ;2号调用换行INT 21HENDM ;宏指令定义结束DATA SEGMENT ;数据段定义DATA1 DB 33H,39H,31H,37H,34H ;第一个数据(作为加数)47193DATA2 DB 36H,35H,30H,38H,32H ;第二个数据(作为被加数)28056DATA ENDS ;数据段定义结束STACK SEGMENT ;堆栈段定义STA DB 20 DUP(?) ;定义从STA开始20个单元作为堆栈使用TOP EQU LENGTH STA ;TOP等于堆栈单元数STACK ENDSCODE SEGMENT ;代码段定义ASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATASTART: MOV AX,DATAMOV DS,AX ;设置数据段MOV AX,STACKMOV SS,AX ;设置堆栈段MOV AX,TOPMOV SP,AXMOV SI,OFFSET DATA2 ;DATA2的偏移地址送SI MOV BX,05 ;计数次数为5次CALL DISPL ;调用多次显示子程序DISPL (显示28056)CRLF ;回车换行MOV SI,OFFSET DATA1 ;DATA1的偏移地址送SI MOV BX,05 ;计数次数为5次CALL DISPL ;调用多次显示子程序DISPL (显示47193)CRLF ;回车换行MOV DI,OFFSET DATA2CALL ADDA ;使用加法运算程序MOV SI,OFFSET DATA1 ;将和显示在屏幕上MOV BX,05 ;显示结束CALL DISPL ;调用多次显示子程序DISPL CRLF ;执行回车换行程序MOV AX,4C00H ;返回系统提示符INT 21HDISPL PROC NEAR ;多次显示子程序DS1: MOV AH,02 ;显示功能号MOV DL,[SI+BX-1] ;显示字符串中一字符INT 21H ; DOS的中断调用DEC BX ;BX减1,修改偏移量JNZ DS1 ;如果BX未减到零跳到DSL执行指令RET ;返回DISPL ENDP ;完成显示功能子程序定义ADDA PROC NEAR ;实行加法运算子程序定义、属性为NEARMOV DX,SIMOV BP,DIMOV BX,05 ;转换5次AD1: SUB BYTE PTR [SI+BX-1],30H ;把加数的ASCLL 转换为16进制SUB BYTE PTR [DI+BX-1],30H ;把被加数的ASCLL转换为16进制DEC BX ;修改偏移量JNZ AD1MOV SI,DXMOV DI,BPMOV CX,05 ;包括进位,共5位 CLC ;清进位AD2: MOV AL,[SI]MOV BL,[DI]ADC AL,BL ;进行代进位加法AAA ;非组合BCD码的加法调整MOV [SI],AL ;结果送被加数区INC SIINC DI ;指向下一位LOOP AD2 ;循环MOV SI,DXMOV DI,BPMOV BX,05AD3: ADD BYTE PTR [SI+BX-1],30HADD BYTE PTR [DI+BX-1],30HDEC BX ;十六进制的数字串转化 JNZ AD3RETADDA ENDP ;加法程序结束CODE ENDS ;代码段结束END START ;整个程序结束六、实验结果、分析和结论和体会1.实验结果:2.心得体会初学《微机原理》时,感觉摸不着头绪概念及原理性的问题不知道该如何下手。

学生实验报告

(2010 —学年第学期)课程名称:微型计算机原理与接口技术开课实验室:2011年月日年级、专业、班学号姓名成绩实验项目名称两个多位十进制数相加的实验指导教

师

教

师

评语教师签名:

年月日

注:报告内容按实验须知中几点要求进行。

一、实验目的

1、学习数据传送和算术运算指令的用法。

2、熟悉在PC机上建立、汇编、链接、调试和运行8088汇编语言程序的过程。

3、学会PC机得安装

4、认识编程过程

二、实验原理及基本技术路线图或实验内容(方框原理图或程序流程图)

将两个多位十进制数相加。

要求被加数均以ASCII码形式各自顺序存放在以DATA1和DATA2为首的5个内存单元中(低位在前),结果送回DATA1处。

程序框图

三、所用软件

四、实验步骤

整个程序分为4个部分:显示加数、转换、相加、输出结果。

五、源码程序编制及分析注释

CRLF MACRO ;宏定义指令(回车执行程序)

MOV DL,0DH ;回车

MOV AH,02H ;2号调用,显示回车

INT 21H

MOV DL,0AH ;换行

MOV AH,02H ;2号调用换行

INT 21H

ENDM ;宏指令定义结束

DATA SEGMENT ;数据段定义

DATA1 DB 33H,39H,31H,37H,34H ;第一个数据(作为加数)47193

DATA2 DB 36H,35H,30H,38H,32H ;第二个数据(作为被加数)28056

DATA ENDS ;数据段定义结束

STACK SEGMENT ;堆栈段定义

STA DB 20 DUP(?) ;定义从STA开始20个单元作为堆栈使用TOP EQU LENGTH STA ;TOP等于堆栈单元数

STACK ENDS

CODE SEGMENT ;代码段定义

ASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATA

START: MOV AX,DATA

MOV DS,AX ;设置数据段

MOV AX,STACK

MOV SS,AX ;设置堆栈段

MOV AX,TOP

MOV SP,AX

MOV SI,OFFSET DATA2 ;DATA2的偏移地址送SI

MOV BX,05 ;计数次数为5次

CALL DISPL ;调用多次显示子程序DISPL(显示28056)

CRLF ;回车换行

MOV SI,OFFSET DATA1 ;DATA1的偏移地址送SI

MOV BX,05 ;计数次数为5次

CALL DISPL ;调用多次显示子程序DISPL(显示47193)

CRLF ;回车换行

MOV DI,OFFSET DATA2

CALL ADDA ;使用加法运算程序

MOV SI,OFFSET DATA1 ;将和显示在屏幕上

MOV BX,05 ;显示结束

CALL DISPL ;调用多次显示子程序DISPL

CRLF ;执行回车换行程序

MOV AX,4C00H ;返回系统提示符

INT 21H

DISPL PROC NEAR ;多次显示子程序

DS1: MOV AH,02 ;显示功能号

MOV DL,[SI+BX-1] ;显示字符串中一字符

INT 21H ;DOS的中断调用

DEC BX ;BX减1,修改偏移量

JNZ DS1 ;如果BX未减到零跳到DSL执行指令

RET ;返回

DISPL ENDP ;完成显示功能子程序定义

ADDA PROC NEAR ;实行加法运算子程序定义、属性为NEAR MOV DX,SI

MOV BP,DI

MOV BX,05 ;转换5次

AD1: SUB BYTE PTR [SI+BX-1],30H ;把加数的ASCLL转换为16进制SUB BYTE PTR [DI+BX-1],30H ;把被加数的ASCLL转换为16进制

DEC BX ;修改偏移量

JNZ AD1

MOV SI,DX

MOV DI,BP

MOV CX,05 ;包括进位,共5位

CLC ;清进位

AD2: MOV AL,[SI]

MOV BL,[DI]

ADC AL,BL ;进行代进位加法

AAA ;非组合BCD码的加法调整

MOV [SI],AL ;结果送被加数区

INC SI

INC DI ;指向下一位

LOOP AD2 ;循环

MOV SI,DX

MOV DI,BP

MOV BX,05

AD3: ADD BYTE PTR [SI+BX-1],30H

ADD BYTE PTR [DI+BX-1],30H

DEC BX ;十六进制的数字串转化

JNZ AD3

RET

ADDA ENDP ;加法程序结束

CODE ENDS ;代码段结束

END START ;整个程序结束

五、实验结果

六、心得体会

通过这次实验让我对这个软件的编程有了更深的了解、知道如何安装这个软件、怎样运行程序。

让我学到了很多课本是学不到的东西,有一点意外收获的感觉。

Welcome To Download !!!

欢迎您的下载,资料仅供参考!。