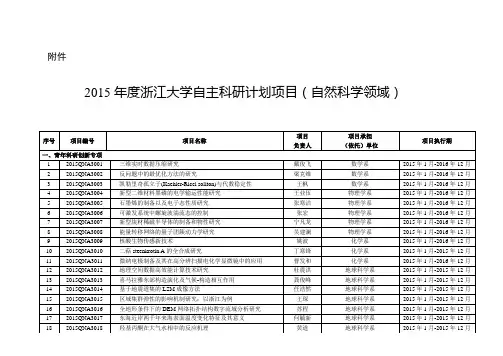

纳米集成电路设计平台-浙江大学

- 格式:doc

- 大小:54.00 KB

- 文档页数:7

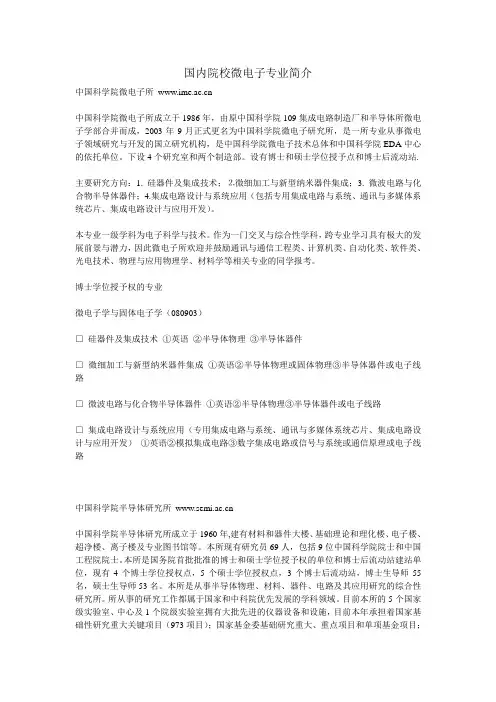

国内院校微电子专业简介中国科学院微电子所中国科学院微电子所成立于1986年,由原中国科学院109集成电路制造厂和半导体所微电子学部合并而成,2003年9月正式更名为中国科学院微电子研究所,是一所专业从事微电子领域研究与开发的国立研究机构,是中国科学院微电子技术总体和中国科学院EDA中心的依托单位。

下设4个研究室和两个制造部。

设有博士和硕士学位授予点和博士后流动站.主要研究方向:1. 硅器件及集成技术;⒉微细加工与新型纳米器件集成;3. 微波电路与化合物半导体器件;4.集成电路设计与系统应用(包括专用集成电路与系统、通讯与多媒体系统芯片、集成电路设计与应用开发)。

本专业一级学科为电子科学与技术。

作为一门交叉与综合性学科,跨专业学习具有极大的发展前景与潜力,因此微电子所欢迎并鼓励通讯与通信工程类、计算机类、自动化类、软件类、光电技术、物理与应用物理学、材料学等相关专业的同学报考。

博士学位授予权的专业微电子学与固体电子学(080903)□硅器件及集成技术①英语②半导体物理③半导体器件□微细加工与新型纳米器件集成①英语②半导体物理或固体物理③半导体器件或电子线路□微波电路与化合物半导体器件①英语②半导体物理③半导体器件或电子线路□集成电路设计与系统应用(专用集成电路与系统、通讯与多媒体系统芯片、集成电路设计与应用开发)①英语②模拟集成电路③数字集成电路或信号与系统或通信原理或电子线路中国科学院半导体研究所中国科学院半导体研究所成立于1960年,建有材料和器件大楼、基础理论和理化楼、电子楼、超净楼、离子楼及专业图书馆等。

本所现有研究员69人,包括9位中国科学院院士和中国工程院院士。

本所是国务院首批批准的博士和硕士学位授予权的单位和博士后流动站建站单位,现有4个博士学位授权点,5个硕士学位授权点,3个博士后流动站,博士生导师55名,硕士生导师53名。

本所是从事半导体物理、材料、器件、电路及其应用研究的综合性研究所。

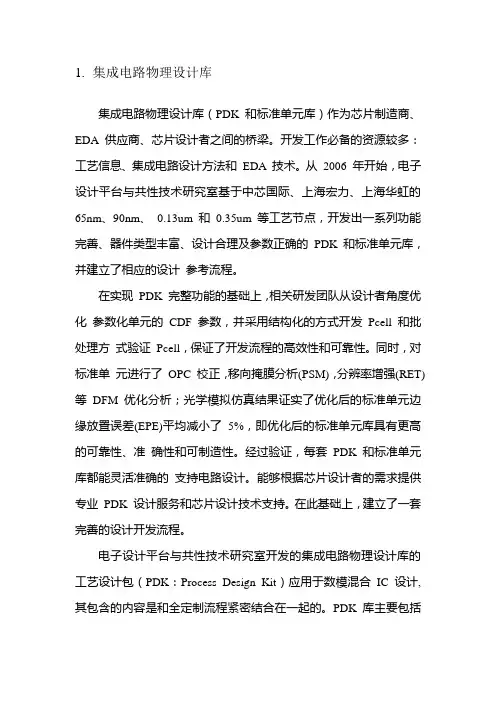

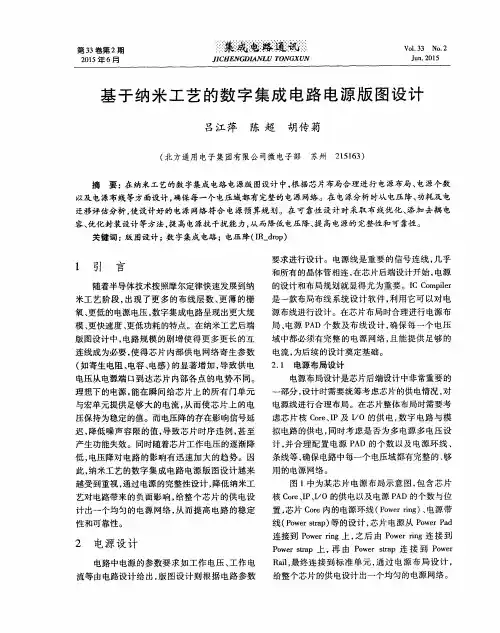

1.集成电路物理设计库集成电路物理设计库(PDK 和标准单元库)作为芯片制造商、EDA供应商、芯片设计者之间的桥梁。

开发工作必备的资源较多:工艺信息、集成电路设计方法和EDA 技术。

从2006 年开始,电子设计平台与共性技术研究室基于中芯国际、上海宏力、上海华虹的65nm、90nm、0.13um 和0.35um 等工艺节点,开发出一系列功能完善、器件类型丰富、设计合理及参数正确的PDK 和标准单元库,并建立了相应的设计参考流程。

在实现PDK 完整功能的基础上,相关研发团队从设计者角度优化参数化单元的CDF 参数,并采用结构化的方式开发Pcell 和批处理方式验证Pcell,保证了开发流程的高效性和可靠性。

同时,对标准单元进行了OPC 校正,移向掩膜分析(PSM),分辨率增强(RET)等DFM 优化分析;光学模拟仿真结果证实了优化后的标准单元边缘放置误差(EPE)平均减小了5%,即优化后的标准单元库具有更高的可靠性、准确性和可制造性。

经过验证,每套PDK 和标准单元库都能灵活准确的支持电路设计。

能够根据芯片设计者的需求提供专业PDK 设计服务和芯片设计技术支持。

在此基础上,建立了一套完善的设计开发流程。

电子设计平台与共性技术研究室开发的集成电路物理设计库的工艺设计包(PDK:Process Design Kit)应用于数模混合IC 设计,其包含的内容是和全定制流程紧密结合在一起的。

PDK 库主要包括以下内容:(1)器件模型(Device Model):由Foundry 提供的仿真模型文件;(2)Symbols & View:用于原理图设计的符号,参数化的设计单元都通过了SPICE 仿真的验证;(3)组件描述格式(CDF:Component Description Format) & Callback:器件的属性描述文件,定义了器件类型、器件名称、器件参数及参数调用关系函数集Callback、器件模型、器件的各种视图格式等;(4)参数化单元(Pcell:Parameterized Cell):它由Cadence 的SKILL 语言编写,其对应的版图通过了DRC 和LVS 验证,方便设计人员进行原理图驱动的版图(SDL:Schematic Driven Layout)设计流程;(5)技术文件(Technology File):用于版图设计和验证的工艺文件,包含GDSII 的设计数据层和工艺层的映射关系定义、设计数据层的属性定义、在线设计规则、电气规则、显示色彩定义和图形格式定义等;(6)物理验证规则文件(PV Rule File):包含版图验证文件集(DRC/LVS/RC)。

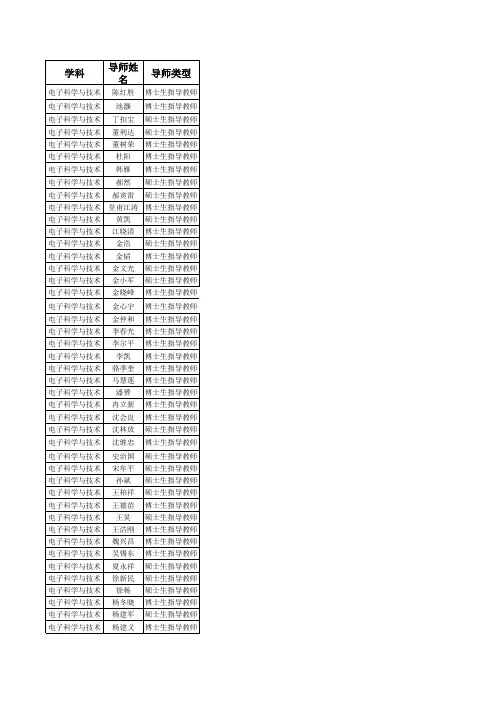

主要研究方向系统级芯片(SOC)设计方法研究用于系统芯片的EDA工具算法研究及实现超大规模集成电路与系统设计深亚微米和微波IC及电网络的理论、分析、计算机仿真电子电力器件及其集成目前正在重点进行以下几个方面研究工作:1、系统级芯片(SOC)设计方法研究进入二十一世纪,微电子工艺技术己进入超深亚微米阶段,目前集成电路的特征线宽已达到0.18um,已完全有能力将信息采集、加工运算、存贮和随动执行这样的超大规模信息系统集成并固化在芯片上,即SOC(System On Chip)。

根据国际微电子技术的发展现状和趋势分析,以超深亚微米(VDSM)和IP复用(Reuse)技术为支撑的微系统芯片(SOC)在世纪之交正在迅速发展,并将在新世纪成为集成电路技术的主流,这是我国集成电路产业发展十分难得的历史机遇。

我们当前急需去实现的是要抓住SOC发展的这一机遇,突出集成电路设计,加强与网络通信、信息安全和关键电子信息产品整机发展相结合,形成掌握自主知识产权的SOC设计能力和相应的高效服务体系,带动并支持我国集成电路行业的跨越式发展。

超大规模集成电路技术及应用研究正是将重点放在自主开发品种较全并有一定数量的可供嵌入的IP核和典型SOC芯片设计研究上;同时着力掌握以软硬件协同设计、IP复用和VDSM关键设计工具为代表的SOC设计技术;还要积极研究未来SOC新工艺、新器件和可靠性等关键支撑技术,实现我国超大规模集成电路技术的跨越发展。

2、EDA工具算法研究及实现目前,我们的工作重点放在后端工具的开发,主要是面向互连的布线方法学研究与实现。

正在从事或申报的课题有:“超深亚微米工艺条件下的关键线网布线技术研究”,“基于光学校正的超深亚微米IC物理设计优化技术研究”,“IC单元电路逻辑参数提取工具”,“单元电路的逻辑同构识别技术研究”等。

3、深亚微米和微波IC及电网络的理论、分析、计算机仿真随着互连线效应影响的越来越显著,这一方向的研究将有重大的意义,我们正在开展三地七校下一代超深亚微米VLSI设计方法学研究课题:“超深亚微米VLSI中电感参数提取”,而“基于网络快速模拟的电子器件建模”是与Transim/Cadence的合作项目。

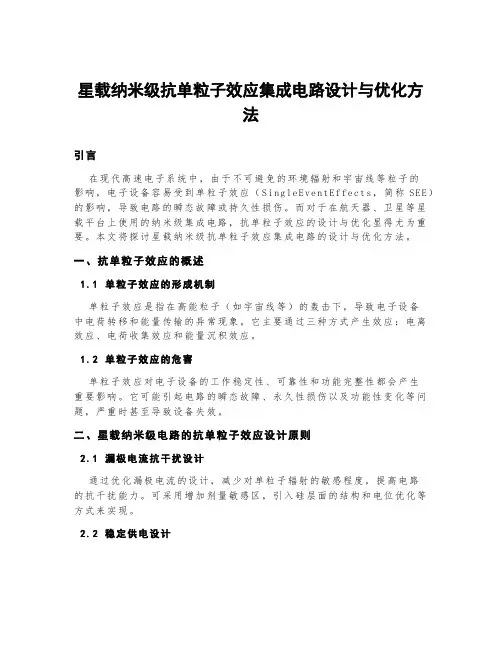

星载纳米级抗单粒子效应集成电路设计与优化方法引言在现代高速电子系统中,由于不可避免的环境辐射和宇宙线等粒子的影响,电子设备容易受到单粒子效应(Si n gl eE ve nt Ef fe cts,简称S EE)的影响,导致电路的瞬态故障或持久性损伤。

而对于在航天器、卫星等星载平台上使用的纳米级集成电路,抗单粒子效应的设计与优化显得尤为重要。

本文将探讨星载纳米级抗单粒子效应集成电路的设计与优化方法。

一、抗单粒子效应的概述1.1单粒子效应的形成机制单粒子效应是指在高能粒子(如宇宙线等)的轰击下,导致电子设备中电荷转移和能量传输的异常现象。

它主要通过三种方式产生效应:电离效应、电荷收集效应和能量沉积效应。

1.2单粒子效应的危害单粒子效应对电子设备的工作稳定性、可靠性和功能完整性都会产生重要影响。

它可能引起电路的瞬态故障、永久性损伤以及功能性变化等问题,严重时甚至导致设备失效。

二、星载纳米级电路的抗单粒子效应设计原则2.1漏极电流抗干扰设计通过优化漏极电流的设计,减少对单粒子辐射的敏感程度,提高电路的抗干扰能力。

可采用增加剂量敏感区,引入硅层面的结构和电位优化等方式来实现。

2.2稳定供电设计充分考虑电源的稳定供应,以减少单粒子效应产生的影响。

采用稳压电源、降噪电源等手段,并结合合理的电源连接布局,确保电路得到稳定供电,降低对供电噪声的敏感度。

2.3记忆元件设计优化对于电路中的记忆元件,如存储器等,要采取特殊的电路设计和工艺优化措施,提高其抗单粒子效应的能力。

比如引入翻转电流和电压势阱技术,设计特殊的电路连接方式等。

三、设计与优化方法实践3.1电路级设计方法电路级设计是保证电路抗单粒子效应的基础。

合理设计电路拓扑结构、减小面积和尺寸、选择低敏感度元器件等是关键步骤。

同时,通过仿真软件进行电路级测试,优化电路元件参数和拓扑结构,提高抗单粒子效应的能力。

3.2层级系统设计方法针对高级集成电路和系统,使用层次化的设计方法,将整个系统分为不同的层次,并针对每个层次进行抗单粒子效应的优化设计。

![小尺寸纳米级集成NMOS器件的可制造性设计[电路与系统专业优秀论文]](https://uimg.taocdn.com/9b47271653ea551810a6f524ccbff121dd36c520.webp)

图1.1s即ta唧sDevi∞进行器件模拟的典型工具流程目前在集成电路虚拟制造技术中,比较流行的半导体器件物理特性模拟软件为synopsys公司的s眈taumsDevice软体。

它采用DD模型,同时提供了HD模型以供用户选择:并通过求解三组基本方程——泊松方程、电流连续性方程及载流子输运方程——获得器件模型的二维电势分布和载流子浓度分布,以此来预测在任何偏置条件下器件的电特性。

(1)泊松方程:半导体器件的电学特性通过求解该方程得到。

胛2矿=1(p—n+崂一K)一风(1.1)其中,F=‘岛为介电常数,岛为真空介电常数,‘为相对介电常数;是本征费米势;P和”分别为空穴和电子浓度;Ⅳ:、.Ⅳ:分别表示电离施主和电离受主浓度;p,为表面电荷密度。

(2)电子,空穴的连续性方程:描述在外加电场作用下,半导体内部载流子的扩散行为。

暑=;寻.z一以=c(%珥∞署=吾寻.z一%=‘(%%纠<1.2)其中,以和u,分别为电子和空穴的复合率;以和.,,分别为电子和空穴的电流密度。

(3)电流密度方程:反映电子及空穴载流子浓度与准费米势间的关系。

(13)J,=qp。

E。

n+qD。

可,JP=q“pEpp—qDp可p其中,脚和脚分别为电子和空穴的迁移率;见和B为电子和空穴的扩散系数。

s∞tallrl】sD“ice通过求解上述3个基木方程来预言器件的行为和性能,也可当玺查耋!i圭耋些篓耋袁4.3拟台后的响应表面多项式系数N0ordersTypeCoeffici∞tTlml0000Co哪t0.442623039090532l000lii摊暂O.335970538109756Xl3OlO0linear一0.251744845223577X240OlOlinearO.0295440547764228X35OOOllinear-0.0458578868902438X.62OOOaxial2·O.0963462309959373x÷702OOaxial2O.0452787690040648x:80020“ial2O.0249159690040657砭90002ax瑚2O.0735896440040644怒10Il00interacnon1.0.150782732164634X1.x21llOlOintct:actionl一0.0261910821646342XlX312IOOIin胁ctionlO.0423243303353658X1.Ⅺ130llOintemctionl一0.003084957t6463415X2.竭14O10lintera融ion1.00120253696646341X2.Ⅺ1500Ilintefaction1.0029694269664634l№.K在完成响应表面建模之后,得到阈值电压和抑制穿通注入、阈值调整注入之问的响应表面如图4.8所示。

集成电路一级学科博士点

以下是部分国内高校中设有集成电路一级学科博士点的列表:

1. 清华大学 - 电子工程系

2. 北京大学 - 电子工程系

3. 上海交通大学 - 电子信息与电气工程学院

4. 浙江大学 - 微电子学院

5. 复旦大学 - 微电子学院

6. 南京大学 - 电子科学与工程学院

7. 中科院上海微系统与信息所 - 微电子学与固体电子学系

8. 南京航空航天大学 - 电子信息工程学院

9. 西安交通大学 - 电子与信息工程学院

10. 东南大学 - 电子科学与工程学院

请注意,该列表仅列举了部分高校中的相应博士点,具体情况可能会有变动,建议您在申请时查阅各高校的官方网站了解最新信息。

考研微电子专业11所热门院校点评清华大学微电子所全国微电子学领域首个重点学科点清华大学微电子学研究所成立于1980年9月,第一任所长由全国著名半导体物理学家、中科院院士李志坚担任。

该所是国家重点支持的北方微电子研究开发基地的主要组成单位,是高素质微纳电子科技人才的培养基地,1988年被定为全国微电子学领域第一个重点学科点。

【硬件环境】两条集成电路工艺加工线清华大学微米/纳米技术研究中心拥有一条4英寸1微米级集成电路工艺线,具有完备的MEMS加工技术与设备,主要用于加工与MEMS器件相关的项目流片。

另外还有一条集成电路开发与工业性试验线,主要进行各类新型SiGe微波功率半导体器件与集成电路以及其他特殊用途的硅集成电路的研究开发,并且可以提供MOSMPW(MOS多项目晶圆)服务。

【师资科研】器件和设计实力最强清华大学微电子所主要分器件、工艺、设计和CAD四个研究方向。

在这四个研究领域中,该所器件和设计实力最强,研究资金丰厚。

器件方向,主要强在理论,其研究方向包括新器件结构与模型、新材料与工艺、新概念与原理,其特点在于新材料和新器件方向结合、LIGA技术与传统IC方向结合、微纳米级器件设计与小尺寸器件模型建立相结合。

微纳器件与系统研究室目前由任天令教授主管,研究方向包括MEMS、新型半导体存储技术、纳电子与自旋电子学和微纳电子技术新材料等。

在MEMS研究方面,器件组是国内惟一重复出当年的静电微马达的科研单位。

工艺方向,包括了研究传统的CMOS工艺技术以及一些新型的工艺技术如数模混合工艺等等。

其中的集成电路开发与工业性试验线由刘志弘教授任主任,该组的主要研究方向是:深亚微米集成电路制造、SiGe技术、非挥发性存储技术、POWER器件及集成电路,以及集成电路生产自动化控制等。

设计方向更偏向于工程。

在各大高校中,清华的电路设计是一流的,与各大公司、研究所以及国内外foundry都有较多的合作,研究课题涉及数字多媒体、神经网络及模糊电路、高层次综合技术(原大唐总裁魏少军在这个方向为北大清华的研究生开有任选课)、IC 测试、多媒体VLSI、加密电路及CPU等等。

忽悠人的,没啥东西,建议不用下载了。

原文内容如下:MEMS公司企业和研究机构列表研究机构:东南大学MEMS教育部重点实验室2, 北京大学微电子学研究院和微米/纳米加工技术国家级重点实验室3, 北京国浩微磁电子智能传感器技术研究所, 北京海淀区, 电子科技集团第13所-国家'863'MEMS专项基地,,河北石家庄新华区合作路, 加速度传感器,陀螺仪,碰撞传感器,倾角传感器,振动传感器,流量传感器,光开关,光衰减器,光反射镜,RF开关,微波移相器,微波带通滤波器5, 中国电子科技集团公司第49所,哈尔滨南岗区一曼街,力/温/湿/气/磁/光6个方面,100多种传感器.20余年MEMS研究,服务国防及重点工程公司企业1. 华润半导体(香港)有限公司,香港,RF MEMS SWITCH,(为美国TERAVICTA代工),硅microphone)2. Memsic-美新半导体(无锡)有限公司,无锡,麦克风3. 楼氏声学公司(Knowles Acoustics),苏州,各类传感器4, 山东歌尔电子有限公司- 歌尔声学股份有限公司,潍坊总部,MEMS部在北京,硅microphone5, 北京青鸟元芯微系统科技有限公司,压力传感器,加速度传感器,湿度传感器6, 博世传感器公司(Bosch Sensortec),医疗(加速度计--药物释放/生物分析,步数计),消费(笔记本坠落感测,振动感测,3D游戏杆),安全工程7, ST-意法半导体8, ADI29, 摩托罗拉10, HP-惠普,喷墨打印机头`11. 英飞凌,TPMS用MEMS传感器,已经与IC完美集成!很厉害!12. 苏州敏芯微电子技术有限公司,硅基MEMS麦克风(07年11月发布,08年批量还有其它的,例如上海巨哥电子科技有限公司,深圳市卡默莱电子科技有限公司,烟台睿创微纳技术有限公司Raytron,上海三鑫科技发展有限公司(Laseno微型激光投影仪)目前,国内MEMS产品门类依然相对较少,主要还是以惯性器件和压力传感器为主,而且多是中低端产品,创新性强的新器件、新系统鲜有出现高校和研究所:北京大学、1000m2 MEMS 洁净室中科院上海微系统与信息技术研究所,1600m2MEMS 洁净室河北半导体研究所(13所)1000m2MEMS 洁净室厦门大学萨本栋微纳米技术研究中心600m2洁净室中国工程物理研究院微系统中心1000 m2洁净室中国科学院微电子研究所中国科学院苏州纳米技术与纳米仿生研究所北京国浩微磁电子智能传感器技术研究所其它的诸如:山东淄博国家高新区MEMS研究院、陕西省微型机械电子系统研究中心、西安212/213所、618所,航天717/704所等等,大连理工王立鼎院士的分析是:研发的分布地区和单位:中国内地MEMS的研发单位主要集中在华北、华东和东北三个地区,还有西南地区的重庆和西北地区的西安等。

53Internet Technology互联网+技术碳基纳米电子器件和集成电路分析摘要:碳基纳米材料以其在光电特性、耐热性、耐辐射性、耐化学药品特性等方面的优越性得到了人们广泛关注,积极探索碳基纳米材料并将其科学、合理应用到各领域中对促进各领域快速发展存在积极影响。

文章则在既有研究成果分析基础上,就碳基纳米电子器件与集成电路研究现状进行了探讨,并对碳基纳米电子器件与集成电路应用表现进行了简要阐述,同时点明其发展过程中存在的技术挑战,包括性能方面的挑战、成本方面的挑战、相关标准方面的挑战等,旨在为碳基纳米技术深入研究提供指导,促进碳基纳米技术优化发展。

关键词:碳基纳米材料;电子器件;集成电路;半导体常超(1994.04-),男,汉族,中国香港,香港城市大学硕士,深圳市万年兄弟集团有限公司总经理,香港仙科电子有限公司总经理,研究方向:微电子与集成电路设计。

一、引言碳基纳米材料是指分散相有一维或多维不超过100nm 的碳材料,如碳纳米管、碳纳米纤维、石墨烯、纳米碳球等。

此类材料所含特性种类多,且多数特性较其他材料更具优势,故研发与应用价值较高。

就碳纳米管为例,多数研究表示其是打破轨硅基集成电路极限,推动集成电路创新化、持续化发展的重要材料之一,是较为理想的电子输送材料,在电子学领域、能源分析领域等具有广阔发展前景。

本研究则以碳基纳米电子器件与集成电路为研究对象,就其研究现状、应用表现以及技术挑战进行了简要分析,具体如下。

二、碳基纳米电子器件的研究现状分析碳基纳米电子器件是碳基纳米材料在电子学领域应用的重要表现,为深入挖掘、了解、彰显碳基纳米材料在电学方面所具有的优势,关于碳基纳米电子器件研究形成了较为丰厚的成果。

例如,基于碳纳米管的研究利用,研制出一种互补金属氧化物半导体器件,该器件由P 型晶体管与N 型晶体管构成,分别由Pd 接触与Sc 接触实现(图1)。

其中在栅长1μm,偏压0.1V 情况下,P 型晶体管与N 型晶体管均可达到2个量级开关比,亚阈值摆幅可达到90~100mV/dec,跨导放大器可达到14~17μS,门级延时约为2×10-11。

集成电路技术十年发展2012-11-27 17:06:17清华大学教授、微电子学研究所所长魏少军一、总体情况集成电路产业是关系国民经济和社会发展全局的基础性、先导性和战略性产业,是电子信息产业的核心,是关系到国家经济社会安全、国防建设极其重要的基础产业。

集成电路产业的竞争力已经成为衡量国家间经济和信息产业可持续发展水平的重要标志,是世界各先进技术国抢占经济科技制高点、提升综合国力的重要领域。

新世纪以来,我国的集成电路科技与产业在国务院国发2000(18号)文件和各级地方政府的持续支持下,获得了长足进步,取得了一系列重要成果:(一)集成电路产业链格局日渐完善中国集成电路产业结构逐步由小而全的综合制造模式逐步走向设计、制造、封装测试三业并举,各自相对独立发展的格局。

目前,中国集成电路产业已经形成了集成电路设计、芯片制造、封装测试及支撑配套业共同发展的较为完善的产业链格局。

(二)集成电路设计产业群聚效应日益凸现以上海为中心的长江三角洲地区、以北京为中心的环渤海地区以及以深圳为中心的珠江三角洲地区已经成为国内集成电路产业集中分布的区域。

全国集成电路设计、制造和封装产业90%以上的销售收入集中于以上三个地区。

其中,包括上海、江苏和浙江的长江三角洲地区是国内最主要的集成电路制造基地,在国内集成电路产业中占有重要地位(三)集成电路设计技术水平显着提高国内集成电路设计企业的技术开发实力也有显着的提高,已经取得多项掌握核心技术的研发成果。

2000年以来,“申威”高性能CPU、“龙芯”和“众志”桌面计算机用CPU、苏州国芯C*Core和杭州中天CK-Core嵌入式CPUIP核、智能卡集成电路芯片、第二代居民身份证专用芯片、自主高清电视(HDTV)标准和自主音视频标准AVS 芯片、华为网络通讯交换装备核心系统芯片、大唐电信COMIPTM和展讯移动通信终端SoC、超大规模集成电路制造工艺、智能卡芯片专用工艺及高压特色工艺等技术和产品都取得了重要成果,大部分成果取得了产品化和产业化的重大进展,并获得国家科技进步奖励。

浸没式光刻技术摘要:光刻工艺直接决定了大规模集成电路的特征尺寸,是大规模集成电路制造的关键工艺。

作为光刻工艺中最重要设备之一,光刻机一次次革命性的突破,使大模集成电路制造技术飞速向前发展。

因此,了解光刻技术的基本原理,了解提高光刻机性能的关键技术以及了解下一代光刻技术的发展情况是十分重要的。

本文就以上几点进行了简要的介绍。

沉浸式光刻技术是在传统的光刻技术中,其镜头与光刻胶之间的介质是空气,而所谓浸入式技术是将空气介质换成液体。

实际上,浸入式技术利用光通过液体介质后光源波长缩短来提高分辨率,其缩短的倍率即为液体介质的折射率。

沉浸式光刻技术是在传统的光刻技术中,其镜头与光刻胶之间的介质是空气,而所谓浸入式技术是将空气介质换成液体。

实际上,浸入式技术利用光通过液体介质后光源波长缩短来提高分辨率,其缩短的倍率即为液体介质的折射率。

关键词:沉浸式光刻、大规模集成电路、折射率目录浸没式光刻技术 (1)目录 (2)第一章背景 (3)1.1 概论 (3)第二章光刻技术 (4)2.1 193nm浸没式光刻技术 (4)2.1.1浸没液体(积淀、气泡、光吸收) (5)2.1.2液体浸没方式(局部浸没法) (5)2.1.3大数值孔径投影物镜的设计(折反式投影物镜) (7)2.1.4 偏振光照明(无损偏振光照明系统) (8)2.1.5液体温度变化带来的影响(热量累积效应) (9)2.1.6气泡的消除(曝光缺陷) (9)2.1.7光刻胶与污染(污染沉积) (9)2.2 浸没式光刻机浸液控制技术研究 (9)2.2.1 浸液控制关键技术研究 (9)2.2.2 浸液控制系统的研制 (11)2.3 控制总结 (13)第三章展望 (14)参考文献 (15)第一章背景1.1 概论沉浸式光刻技术是在传统的光刻技术中,其镜头与光刻胶之间的介质是空气,而所谓浸入式技术是将空气介质换成液体。

实际上,浸入式技术利用光通过液体介质后光源波长缩短来提高分辨率,其缩短的倍率即为液体介质的折射率。

浙江省科学技术厅关于下达2007年第三批重大科技专项和优先主题项目计划的通知浙科发计〔2007〕305号各市、县(市、区)科技局,省级有关部门,有关高等学校、科研院所,各有关项目承担单位,杭州高新技术产业开发区,各省级高新技术产业园区:为了深入贯彻实施《浙江省科技强省建设与“十一五”科学技术发展规划纲要》,根据《浙江省重大科技专项计划管理办法(试行)》规定,我厅会同省级有关部门,在组织实施第一批、第二批项目的基础上,经实地调研和专家评审、论证,提出了161项重点项目,作为今年第三批重大科技专项和优先主题计划项目。

经省政府批准同意,现将第三批重大科技专项和优先主题计划项目下达给你们。

请各有关项目承担单位按规定要求抓紧签定科技计划项目合同书,认真做好项目的组织实施工作。

附件:2007年第三批重大科技专项和优先主题计划项目表二○○七年十二月五日2007年第三批重大科技专项和优先主题项目计划编制说明一、项目构成本批重点项目共161项,涉及25个重大科技专项和11个优先主题。

其中:重大科技专项项目128项,优先主题项目33项。

涉及领域工业项目85项,农业项目35项,社会发展项目41项。

二、经费支持方式本批项目中,重点项目实行分期补助61项,事后补助100项。

三、实施要求1.请项目承担单位抓紧与我厅有关业务处联系,签定科技计划项目合同书。

2.请各市、县(市、区)科技部门、省有关项目管理责任部门督促做好项目的组织实施工作。

3.由市、县(市、区)推荐的项目,以上三种支持方式均要求市县财政给予经费配套。

本批计划中有9项招标或择优委托项目,项目承担单位经招投标程序和择优委托程序确定。

2007年度第三批重大科技专项和优先主题计划项目表。