基于LFSR和组合猫映射的伪随机序列生成方法

- 格式:pdf

- 大小:593.56 KB

- 文档页数:5

fpga用lfsr伪随机序列生成信道的高斯白噪声FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它具有逻辑门、寄存器和片内存储器等基本电路,通过可编程的逻辑门和寄存器来实现复杂的功能。

而LFSR(Linear Feedback Shift Register)是一种线性反馈移位寄存器,可以生成伪随机序列。

在无线通信中,信道往往存在噪声,如高斯白噪声。

高斯白噪声是一种具有均值为0,方差为常数的随机噪声,其功率谱密度在所有频率上都是常数。

为了模拟信道中的噪声,可以使用LFSR生成伪随机序列,进而通过合适的变换生成高斯白噪声。

LFSR通过反馈位的线性组合,实现对当前状态位的更新。

当LFSR的状态位为1时,反馈位称为“1”,否则为“0”。

每个时钟周期,LFSR的状态位根据反馈位做一个循环右移,并根据反馈位的线性组合更新当前状态位。

由于状态位的变化具有一定的随机性,LFSR可以产生一个很长的伪随机序列。

FPGA中可以利用LFSR的特性生成伪随机序列来模拟信道中的噪声。

下面是一种使用LFSR生成高斯白噪声的方法:1.配置FPGA中的LFSR模块。

将LFSR的位数和反馈位的线性组合系数进行设置,以确保生成的伪随机序列具有良好的统计特性。

2.通过FPGA的时钟信号,逐个时钟周期更新LFSR的状态位。

LFSR会生成一个不断变化的伪随机序列。

3.将LFSR输出的伪随机序列通过合适的变换得到高斯白噪声。

常见的变换方法包括映射到高斯分布、尺度变换和偏移等。

4.将生成的高斯白噪声添加到信道中。

通过将信号与高斯白噪声相加,可以模拟信道中存在的噪声。

使用FPGA生成高斯白噪声的好处在于,可以根据具体场景和需求调整LFSR的位数和反馈位的线性组合系数,从而获得期望的噪声特性。

此外,由于FPGA的并行计算能力,可以实现高速生成噪声的功能。

在无线通信系统的性能测试、算法验证等方面,使用FPGA生成高斯白噪声是很常见的方法。

伪随机序列的研究与仿真伪随机序列(pseudo-random sequence)是指通过算法生成的具有随机性质的序列,但实际上是以确定性的方式生成的序列。

伪随机序列被广泛应用于密码学、模拟仿真、通信系统等领域。

本文将研究伪随机序列的生成方法、性质分析和仿真实验。

首先,伪随机序列的生成方法有多种,常见的有线性反馈移位寄存器(LFSR)、梅森旋转算法等。

其中,LFSR是一种最常用的伪随机序列生成器。

它是由若干个触发器和异或门组成的移位寄存器,通过不断向寄存器输入新的比特,并根据寄存器中的比特进行异或运算,生成新的伪随机序列。

梅森旋转算法是一种基于迭代运算的随机数生成方法,通过矩阵运算和循环左移操作,不断更新种子值,生成伪随机序列。

其次,伪随机序列的性质分析是研究伪随机序列是否具有随机性质的重要方法。

在伪随机序列的性质分析中,常用的指标包括自相关函数、互相关函数和周期。

自相关函数可以用于判断伪随机序列是否具有统计无关性,互相关函数可以用于判断两个伪随机序列之间是否相关。

周期是指伪随机序列重复出现的最小周期,周期越长表示伪随机序列更随机。

最后,通过仿真实验可以验证伪随机序列的性质。

在仿真实验中,可以通过计算自相关函数、互相关函数和周期等指标来验证伪随机序列的性质。

此外,还可以通过模拟随机事件的发生概率来验证伪随机序列的随机性。

例如,在模拟掷硬币事件时,可以通过比较生成的伪随机序列中正面出现的次数和反面出现的次数来验证伪随机序列的随机性。

综上所述,伪随机序列的研究与仿真是一个复杂而有挑战性的任务。

通过研究伪随机序列的生成方法和性质分析,可以更好地理解伪随机序列的随机性质。

通过仿真实验,可以验证伪随机序列的性质,并为伪随机序列在密码学、通信系统等领域的应用提供依据。

伪随机二进制序列伪随机二进制序列(PRBS)是一种在通信领域广泛应用的序列性质,并被用于数据传输、信号处理、密码学等方面。

它以一种看似无规律的方式产生二进制序列,但实际上具有一定的统计特性和周期性。

本文将为您介绍伪随机二进制序列的定义、生成方法、应用领域以及研究前景。

首先,让我们了解一下伪随机二进制序列的定义。

伪随机二进制序列是由计算机或电子器件生成的一串二进制数字。

虽然它们看起来像是随机的,但经过统计分析后,我们可以发现它们具有一定的规律和周期性。

这是因为这些序列是通过特定的算法生成的,而不是真正的随机数。

那么,如何生成这种伪随机二进制序列呢?在通信领域中,最常用的生成方法是使用线性反馈移位寄存器(LFSR)。

LFSR是一种能够产生伪随机序列的电子电路,它通过位移寄存器和异或门的组合来实现。

通过适当选择寄存器的位数和反馈多项式,我们可以生成具有不同周期和特性的伪随机二进制序列。

除了LFSR,还有其他一些生成伪随机二进制序列的方法,如非线性动力系统、混沌系统等。

这些方法利用了复杂且不可预测的数学模型来生成序列,具有更高的随机性和安全性。

伪随机二进制序列在通信和密码学等领域有着广泛的应用。

在数据传输中,它们被用于编码和调制,以提高信号传输的可靠性和效率。

在信号处理中,它们可以用于频谱分析、噪声测试、通道估计等方面。

在密码学中,伪随机二进制序列被用作密钥生成和加密算法中的扰动源,用于保护数据的安全性。

此外,伪随机二进制序列还有着广阔的研究前景。

随着通信和信息技术的快速发展,人们对于高效、安全的数据传输和处理需求不断增加。

因此,如何生成更长周期、更高随机性的伪随机二进制序列成为了当前研究的热点之一。

同时,研究者还探索了将混沌系统、量子随机性等引入到伪随机序列的生成中,以提升其性能和应用范围。

总而言之,伪随机二进制序列是一种在通信和密码学领域中重要的序列性质。

它们通过特定的算法生成,具有一定的统计特性和周期性。

m序列原理m序列是一种特殊的伪随机序列,具有良好的随机性质和周期性,广泛应用于通信、密码学、雷达、遥感等领域。

m序列的原理是基于线性反馈移位寄存器(LFSR)的工作原理,通过适当的初值和反馈多项式,可以生成具有良好随机性质的序列。

m序列的生成原理是基于LFSR的工作原理。

LFSR是一种线性反馈移位寄存器,它由若干个存储单元和适当的反馈电路组成。

在LFSR中,存储单元中的数据按照时钟信号不断移位,同时根据反馈电路的控制,将某些位上的数据进行异或运算,得到新的输入数据,从而实现序列的生成。

通过适当选择LFSR的初值和反馈多项式,可以得到不同长度的m序列。

m序列具有良好的随机性质和周期性。

由于m序列的生成原理是基于LFSR的移位和异或运算,使得序列中的数据呈现出随机分布的特性。

同时,由于LFSR的结构和反馈多项式的选择,m序列具有很长的周期,甚至可以达到最大周期2^n-1,其中n为LFSR的位数。

这使得m序列在伪随机序列中具有较好的性能。

m序列在通信、密码学、雷达、遥感等领域有着广泛的应用。

在通信系统中,m序列可以作为扩频序列,用于码分多址(CDMA)通信系统中的信道编码和解码,提高通信系统的抗干扰能力和安全性。

在密码学中,m序列可以作为密钥序列,用于数据加密和解密,保障通信的安全性。

在雷达和遥感领域,m序列可以作为调制序列,用于信号的调制和解调,提高信号的分辨率和抗干扰能力。

总之,m序列作为一种特殊的伪随机序列,具有良好的随机性质和周期性,在通信、密码学、雷达、遥感等领域有着广泛的应用前景。

通过深入理解m序列的生成原理和特性,可以更好地应用于实际系统中,提高系统的性能和安全性。

摘要:通过分析各种伪随机序列生成方法,提出了一种基于M 序列的连续抽样方法,可以生成满足自适应光学系统SPGD 控制算法要求的多路、相互独立以及服从伯努利分布的伪随机序列。

该方法适合于用FPGA等超大规模集成电路实现,且具有占用硬件资源较少,实现方便等优点。

用FPGA 实现了用于61 单元自适应光学系统SPGD 控制算法的伪随机序列,并将此方法应用于基于SPGD 控制算法的自适应光学系统实验中,实验表明,该方法能够满足自适应光学系统SPGD 算法的需求,系统实现成功闭环。

1 引言随机序列是一组满足特定统计学规律的数据,在信号理论分析中应用非常普遍。

由于精确的随机序列生成方法较为复杂,产生的随机序列不具有可重复性等特点,在很多应用场合使用伪随机序列。

伪随机序列在扩频通信、信息加密和系统测试等诸多领域中都有着广泛的应用。

在自适应光学SPGD 算法中,伪随机序列亦有相当重要的作用。

Vorontsov 等人在1997 年将SPGD 算法引入到自适应光学领域[2]。

国内在近几年开始了对 SPGD 算法在自适应光学系统应用的研究,并且在计算机上用软件编程实现了算法,进行了自适应光学的系统实验[3]。

自适应光学SPGD 控制算法的研究趋势是使用专用的信号处理硬件电路作为算法的实现平台,以获得更高的迭代速度和更好的收敛效果。

Cauwenberghs等人设计了专用的模拟超大规模集成电路实现SPGD 控制算法,并且在一些应用领域进行了实验[5]。

目前自适应光学系统的规模普遍达到几十上百单元。

针对多单元自适应光学系统SPGD 控制算法的特殊要求,本文提出了一种适合于用FPGA 硬件电路产生满足算法要求的多路伪随机序列的生成方法,完成了FPGA 电路的硬件实现,并将其用于实现61 单元自适应光学SPGD控制算法,同时进行自适应光学的闭环实验。

2 自适应光学 SPGD 控制算法对伪随机序列的要求SPGD(the Stochastic Parallel Gradient Descent algorithm)算法通过对多路的控制参数加入随机并行的扰动,使用性能指标测量值的变化量与控制参数的变化量进行控制参数的梯度估计,以迭代方式在梯度下降方向上进行控制参数的搜索。

geffe序列生成器例题Geffe序列生成器是一种线性反馈移位寄存器(Linear Feedback Shift Register, LFSR)序列生成器,由Geffe提出。

它通过三个LFSR组合运算来生成伪随机序列。

Geffe序列生成器的原理和实现比较简单,因此很适合用来实现轻量级的加密算法或伪随机数生成。

以下是一个使用Geffe序列生成器的例题:假设我们需要生成一个长度为N的伪随机序列,其中N为正整数。

我们可以通过以下步骤来实现:1. 初始化三个长度分别为L1,L2和L3的LFSR,初始向量可以任意选择。

LFSR的长度L1,L2和L3可以根据需要进行选择,一般情况下,L1 < L2 < L3。

2. 从L1中取出第一个比特值x1,从L2中取出第二个比特值x2,从L3中取出第三个比特值x3。

3. 计算输出比特y = (x1 & x2) ⊕ (¬x1 & x3),其中&表示按位与操作,⊕表示按位异或操作,¬表示按位取反操作。

4. 将x1、x2和x3依次向左移动一个比特。

5. 将y作为输出,并重复步骤2-5直到生成N个比特为止。

Geffe序列生成器的安全性和随机性依赖于LFSR的选择和初始向量的选择。

较小的LFSR长度和可预测的初始向量可能导致序列的周期性和可预测性,从而降低生成的伪随机序列的安全性。

因此,为了提高安全性,可以选择较大的LFSR长度,并且使用随机或由真随机数生成器生成的初始向量。

此外,Geffe序列生成器还可以通过修改计算输出比特的逻辑表达式来增加非线性。

例如,可以使用非线性函数来替代简单的逻辑门操作,以增加序列的复杂性和随机性。

需要注意的是,Geffe序列生成器是一种伪随机序列生成器,生成的序列并不具备真正的随机特性。

因此,在一些安全性较高的应用中,如密码学等,需要使用更强大的真随机数生成器来生成随机序列。

总结起来,Geffe序列生成器是一种简单而有效的伪随机序列生成器,通过组合多个LFSR的运算来生成序列。

基于混沌系统的伪随机序列生成方法张雪锋;范九伦【摘要】给出了一种循环迭代结构的伪随机序列生成方法.选择函数根据LFSR的计算结果进行取值,确定当前迭代计算使用的混沌系统,通过迭代计算产生相应的混沌序列,然后将生成的混沌序列进行相应的数制转换,将得到的二进制值序列作为产生的伪随机序列输出,同时将其作为反馈值与LFSR的反馈值进行相应的运算,运算结果作为LFSR的最终反馈值,实现对LFSR生成序列的随机扰动.通过实验对生成的伪随机序列进行了分析,结果表明,产生的序列具有良好的随机性和安全性.【期刊名称】《计算机工程与应用》【年(卷),期】2010(046)029【总页数】4页(P80-82,130)【关键词】线性反馈移位寄存器(LFSR);混沌系统;伪随机序列;随机性【作者】张雪锋;范九伦【作者单位】西安邮电学院,通信与信息工程学院,西安,710061;西安电子科技大学,电子工程学院,西安,710071;西安邮电学院,通信与信息工程学院,西安,710061【正文语种】中文【中图分类】TN9181 引言随着信息技术的飞速发展和普及,人们对信息安全问题日益关注。

密码技术是实现信息保密的核心技术,随着密码领域中流密码技术的广泛应用,高质量的伪随机数发生器(Pseudo-Random Number Generator,PRNG)被广泛应用于信息加密、分布式计算、CDMA系统等领域,设计性能良好的密钥流序列成为流密码研究领域的一个研究热点[1-3]。

目前在流密码领域中被广泛应用的线性反馈移位寄存器(Linear Feedback Shift Register,LFSR)由于采用逻辑运算,具有实现简单、计算速度块、便于硬件化等优点,成为目前构造密钥流生成器的最重要部件之一。

基于LFSR的伪随机序列生成技术主要分为两类:一类是LFSR和非线性布尔函数相结合产生伪随机序列,如非线性组合流密码、前馈流密码等方法[4-5];另一类是用一个LFSR去控制另一个LFSR,如钟控型生成器和缩减型生成器等[6-7]。

伪随机序列的构造及其性质分析伪随机序列的构造及其性质分析随机序列在现代密码学和计算机科学中有着广泛的应用。

伪随机序列(Pseudo-Random Sequence,简称PRBS)是一种通过确定性算法构造出的近似随机序列。

本文将探讨伪随机序列的构造方法,以及分析其性质。

一、伪随机序列的构造方法:1. 线性反馈移位寄存器(Linear Feedback Shift Register,简称LFSR):LFSR是最常见的构造伪随机序列的方法之一。

它是一个位寄存器,其中的每一个比特都是由寄存器中之前的多个位的线性组合得到的。

通过不同的初始状态和反馈多项式,可以构造出不同长度和周期的伪随机序列。

2. 循环冗余校验码(Cyclic Redundancy Check,简称CRC):在数据传输和存储过程中,CRC常用于错误检查和校正。

CRC算法利用多项式除法的原理,将输入数据与一个预设的除数进行除法运算,生成校验码。

将输入数据与校验码连接起来,就得到了伪随机序列。

二、伪随机序列的性质分析:1. 均匀性:伪随机序列应当具有均匀分布的特性,即每个元素出现的概率相等。

通过统计分析伪随机序列的频率分布,可以验证其均匀性。

2. 独立性:在伪随机序列中,相邻的元素应当是独立的,即前一个元素不能推断出下一个元素的值。

通过计算伪随机序列的自相关函数和互相关函数,可以评估序列中元素的独立性。

3. 周期性:伪随机序列应当具有较长的周期,周期越长,序列的重复性就越低。

通过寻找伪随机序列中的重复模式,并计算出其周期,可以评估序列的周期性。

4. 伪随机性:伪随机序列应当具有足够的伪随机性,即难以被预测。

通过应用统计学方法,如Chi-square检验和Kolmogorov-Smirnov检验,可以验证伪随机序列的随机性。

三、总结:伪随机序列的构造方法多种多样,常用的方法包括LFSR和CRC。

对于生成的伪随机序列,我们可以通过分析其均匀性、独立性、周期性和伪随机性来评估其质量和安全性。

序列伪随机码产生及应用仿真matlab一、概述随机序列是一种具有随机性质的数字序列,可用于信息传输、通信系统、密码学、雷达等领域。

伪随机序列是一种经过数学算法产生的序列,其具有类似与随机序列的统计特性,但实际上是确定性的。

在通信系统中,伪随机序列广泛应用于码分多址技术、扩频通信、混沌通信等领域。

本文将介绍伪随机码的产生原理,并使用matlab进行仿真实现,以加深对该技术的理解。

二、伪随机码的产生原理伪随机码的产生主要包括线性反馈移位寄存器(LFSR)、加法(XOR)运算和乘法(AND)运算等步骤。

下面以LFSR为例,介绍伪随机码的产生原理。

1. LFSR原理LFSR是一种利用移位寄存器和反馈逻辑电路构成的伪随机码产生器。

在LFSR中,存在一个移位寄存器和一个反馈逻辑电路。

移位寄存器中存储了若干比特的信息,经过时钟信号的控制完成信息的移位操作。

而反馈逻辑电路则根据寄存器中的信息产生反馈信号,从而实现伪随机序列的产生。

2. 伪随机码的产生过程(1)初始化LFSR。

将移位寄存器中的初始状态设置为一个非零的值。

(2)循环移位寄存器。

根据时钟信号的控制,移位寄存器中的信息进行移位操作。

(3)根据反馈逻辑电路的输出,生成伪随机序列。

通过反馈逻辑电路生成的反馈信号,即为伪随机序列的一部分。

三、matlab仿真实现matlab是一种功能强大的科学计算软件,具有丰富的绘图和仿真功能。

下面将使用matlab进行伪随机码的产生和仿真实现。

1. 产生伪随机码在matlab中,可以使用shiftregister函数实现LFSR的移位寄存器功能。

结合matlab的位运算功能,可以方便地实现伪随机码的产生。

以下是一个简单的matlab代码示例:```matlab定义LFSR的初始状态state = [1 0 1 0 1];定义LFSR的反馈多项式polynomial = [5 2];产生伪随机码for i = 1:10获取LFSR的输出output = state(end);计算新的状态new_state = mod(sum(state(polynomial)), 2);更新状态state = [new_state, state(1:end-1)];显示输出disp(output);end```上述代码中,通过定义LFSR的初始状态和反馈多项式,使用循环产生了10个伪随机码的输出。

FPGA产生基于LFSR的伪随机数1.概念通过一定的算法对事先选定的随机种子(seed)做一定的运算可以得到一组人工生成的周期序列,在这组序列中以相同的概率选取其中一个数字,该数字称作伪随机数,由于所选数字并不具有完全的随机性,但是从实用的角度而言,其随机程度已足够了。

这里的“伪”的含义是,由于该随机数是按照一定算法模拟产生的,其结果是确定的,是可见的,因此并不是真正的随机数。

伪随机数的选择是从随机种子开始的,所以为了保证每次得到的伪随机数都足够地“随机”,随机种子的选择就显得非常重要,如果随机种子一样,那么同一个随机数发生器产生的随机数也会一样。

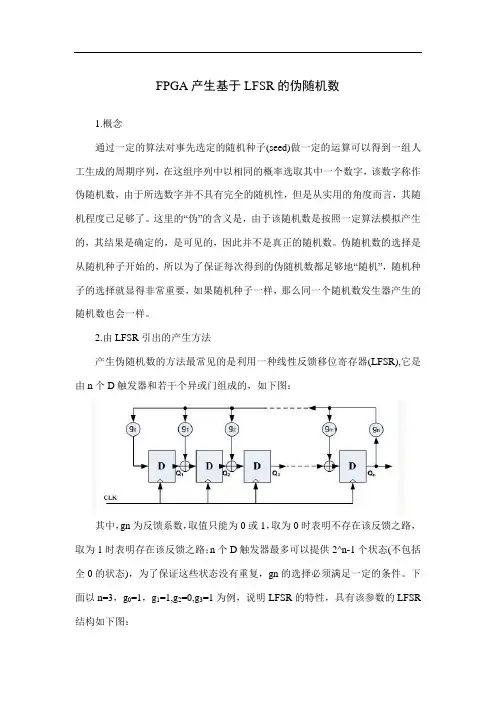

2.由LFSR引出的产生方法产生伪随机数的方法最常见的是利用一种线性反馈移位寄存器(LFSR),它是由n个D触发器和若干个异或门组成的,如下图:其中,gn为反馈系数,取值只能为0或1,取为0时表明不存在该反馈之路,取为1时表明存在该反馈之路;n个D触发器最多可以提供2^n-1个状态(不包括全0的状态),为了保证这些状态没有重复,gn的选择必须满足一定的条件。

下面以n=3,g0=1,g1=1,g2=0,g3=1为例,说明LFSR的特性,具有该参数的LFSR 结构如下图:假设在开始时,D2D1D0=111(seed),那么,当时钟到来时,有:D2=D1_OUT=1;D1=D0_OUT^D2_OUT=0;D0=D2_OUT=1;即D2D1D0=101;同理,又一个时钟到来时,可得D2D1D0=001. ………………画出状态转移图如下:从图可以看出,正好有2^3-1=7个状态,不包括全0;如果您理解了上图,至少可以得到三条结论:1)初始状态是由SEED提供的;2)当反馈系数不同时,得到的状态转移图也不同;必须保证g n===1,否则哪来的反馈?3)D触发器的个数越多,产生的状态就越多,也就越“随机”;3.verilog实现基于以上原理,下面用verilog产生一个n=8,反馈系数为g0g1g2g3g4g5g6g7g8=101110001的伪随机数发生器,它共有2^8=255个状态,该LFSR的结构如下:verilog源代码如下:module RanGen(input rst_n, /*rst_n is necessary to prevet locking up*/input clk, /*clock signal*/input load, /*load seed to rand_num,active high */input [7:0] seed,output reg [7:0] rand_num /*random number output*/ );always@(posedge clk or negedge rst_n)beginif(!rst_n)rand_num <=8'b0;else if(load)rand_num <=seed; /*load the initial value when load is active*/ elsebeginrand_num[0] <= rand_num[7];rand_num[1] <= rand_num[0];rand_num[2] <= rand_num[1];rand_num[3] <= rand_num[2];rand_num[4] <= rand_num[3]^rand_num[7];rand_num[5] <= rand_num[4]^rand_num[7];rand_num[6] <= rand_num[5]^rand_num[7];rand_num[7] <= rand_num[6];endendendmodule以1111 1111为种子,load信号置位后,开始在255个状态中循环,可将输出值255、143、111……作为伪随机数。

verilog可综合伪随机数生成算法Verilog可综合伪随机数生成算法引言:在数字电路设计中,经常需要使用伪随机数生成算法来产生随机的测试向量或者模拟随机事件。

Verilog是一种硬件描述语言,可以用于数字电路设计和验证。

本文将介绍一种基于Verilog的可综合伪随机数生成算法。

一、伪随机数生成算法概述伪随机数生成算法是一种通过确定性方法产生看似随机的数列的算法。

在数字电路设计中,常用的伪随机数生成算法有线性反馈移位寄存器(LFSR)和伪随机数发生器(PRG)等。

二、基于Verilog的LFSR算法实现LFSR是一种简单且高效的伪随机数生成算法,其原理是通过移位寄存器和异或门组成的反馈回路来产生伪随机数序列。

以下是一个基于Verilog的LFSR算法实现的示例代码:```verilogmodule lfsr (input wire clk,input wire reset,output wire [7:0] rand_out);reg [7:0] state;always @(posedge clk or posedge reset) beginif (reset)state <= 8'b00000000;else beginstate <= {state[6:0], state[7] ^ state[5]};endendassign rand_out = state;endmodule```在该示例代码中,使用了一个8位的移位寄存器state来存储当前的状态。

每个时钟周期,state的值向左移动一位,并将最高位与第6位异或得到的结果作为新的最低位。

当reset信号为高电平时,将state初始化为全零。

通过输出rand_out信号,我们可以获取到产生的伪随机数。

三、基于Verilog的伪随机数发生器算法实现伪随机数发生器是一种更加复杂的随机数生成算法,它使用了更多的逻辑门和状态变量来实现。

基于LFSR具有并行与串行结果一致的随机数生成算法

王超;张秋艳;张姗;王龙

【期刊名称】《微型机与应用》

【年(卷),期】2018(037)010

【摘要】随着信息技术的快速发展,随机数的应用越来越广泛,快速产生海量随机数的需求日益增长.针对这一问题,在基于线性反馈移位寄存器产生伪随机数的理论基础上,利用采样定理提出了一种适用于多核处理器的新伪随机数生成算法.新算法在并行运行时与经典串行算法产生一致的随机数,不仅提高了效率,而且保持了通用性.通过理论分析和实验验证,证明了该新算法具有较好的加速比,具有重要的理论和工程实际意义.

【总页数】5页(P15-18,45)

【作者】王超;张秋艳;张姗;王龙

【作者单位】中国电子信息产业集团有限公司第六研究所,北京100083;中国电子信息产业集团有限公司第六研究所,北京100083;中国电子信息产业集团有限公司第六研究所,北京100083;中国电子信息产业集团有限公司第六研究所,北京100083

【正文语种】中文

【中图分类】TN918.1

【相关文献】

1.基于FPGA的CRC算法的串行和并行实现 [J], 肖艳艳;何晓雄

2.基于并行模板的手写体汉字串行细化算法 [J], 宋莹;王展青;陈彧

3.基于VHDL的并行到串行转换器算法模型 [J], 曾技

4.一种基于基因表达式编程的串行聚类算法并行化研究 [J], 蔡宏果;元昌安

5.基于LFSR具有并行与串行结果一致的随机数生成算法 [J], 王超; 张秋艳; 张姗; 王龙

因版权原因,仅展示原文概要,查看原文内容请购买。