第6章 伪随机序列生成器

- 格式:ppt

- 大小:141.00 KB

- 文档页数:12

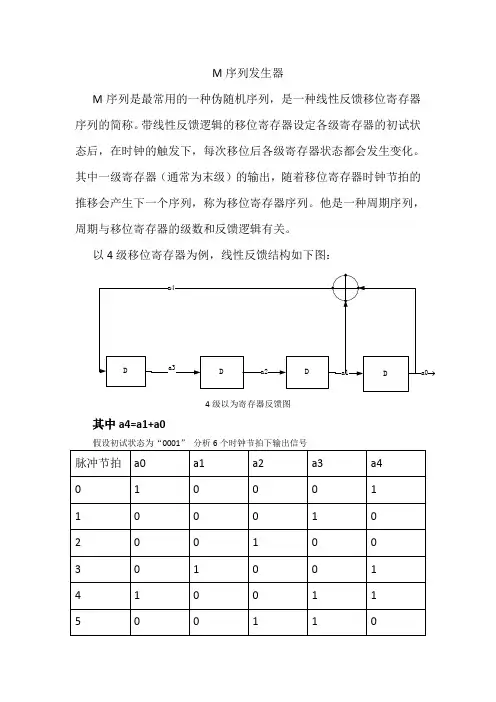

M序列发生器M序列是最常用的一种伪随机序列,是一种线性反馈移位寄存器序列的简称。

带线性反馈逻辑的移位寄存器设定各级寄存器的初试状态后,在时钟的触发下,每次移位后各级寄存器状态都会发生变化。

其中一级寄存器(通常为末级)的输出,随着移位寄存器时钟节拍的推移会产生下一个序列,称为移位寄存器序列。

他是一种周期序列,周期与移位寄存器的级数和反馈逻辑有关。

以4级移位寄存器为例,线性反馈结构如下图:4级以为寄存器反馈图其中a4=a1+a0信号a4:a0禁止出现全0,否则将会出现全0,序列不变化。

实验仿真Code:library IEEE;use IEEE.STD_LOGIC_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--use IEEE.NUMERIC_STD.ALL;-- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity random_4 isPort ( clk : in STD_LOGIC;reset : in STD_LOGIC;din : in STD_LOGIC_VECTOR (3 downto 0);dout : out STD_LOGIC_VECTOR (3 downto 0);load : in STD_LOGIC);end random_4;architecture Behavioral of random_4 issignal rfsr :std_logic_vector(3 downto 0);--signal temp:std_logic;beginprocess(clk,reset,load,din)beginif (reset ='1') thenrfsr <=(others =>'0');elsif (clk' event and clk='1') thenif(load ='1') then ----load =1rfsr<= din;elserfsr(3) <= rfsr(0) xor rfsr(1);rfsr(2 downto 0) <= rfsr(3 downto 1);end if;end if;end process;------signal rename----dout <= rfsr;end Behavioral;testbench:LIBRARY ieee;USE ieee.std_logic_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--USE ieee.numeric_std.ALL;ENTITY random_testbench ISEND random_testbench;ARCHITECTURE behavior OF random_testbench IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT random_4PORT(clk : IN std_logic;reset : IN std_logic;din : IN std_logic_vector(3 downto 0);dout : OUT std_logic_vector(3 downto 0);load : IN std_logic);END COMPONENT;--Inputssignal clk : std_logic := '0';signal reset : std_logic := '0';signal din : std_logic_vector(3 downto 0) := (others => '0'); signal load : std_logic := '0';--Outputssignal dout : std_logic_vector(3 downto 0);-- Clock period definitionsconstant clk_period : time := 10 ns;---variablesignal cnt: integer :=0;BEGIN-- Instantiate the Unit Under Test (UUT)uut: random_4 PORT MAP (clk => clk,reset => reset,din => din,dout => dout,load => load);-- Clock process definitionsclk_process :processbeginclk <= '0';wait for clk_period/2;clk <= '1';wait for clk_period/2;end process;-- Stimulus processstim_proc: process(clk)begin-- hold reset state for 100 ns. if(cnt = 0) then--initializationreset <= '1' after 100 ps;load <= '1' after 100 ps;din <="0001";cnt <= cnt +1;---elsif(cnt =1) thenreset <= '0' after 100 ps;load <= '1' after 100 ps;din <="0001";cnt <= cnt +1;elsif(clk' event and clk ='1') then reset <= '0' after 100 ps;load <= '0' after 100 ps;din <="0001";---executuecnt <= cnt +1;if(cnt = 100) thencnt <= 2;end if;end if;end process;END;。

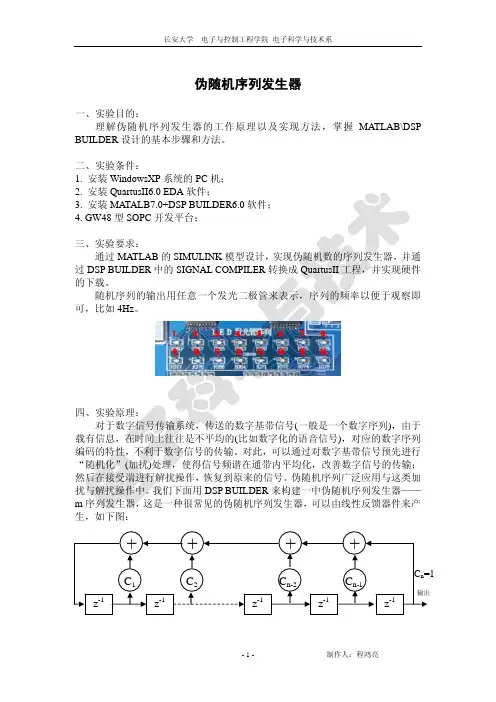

伪随机序列发生器一、实验目的:理解伪随机序列发生器的工作原理以及实现方法,掌握MATLAB\DSP BUILDER设计的基本步骤和方法。

二、实验条件:1. 安装WindowsXP系统的PC机;2. 安装QuartusII6.0 EDA软件;的序列发生器,并通⒈ ⒉ ⒊⒋⒌⒍⒎⒏⒐ ⒑ ⒒⒓⒔⒕⒖⒗四、实验原理:对于数字信号传输系统,传送的数字基带信号(一般是一个数字序列),由于载有信息,在时间上往往是不平均的(比如数字化的语音信号),对应的数字序列编码的特性,不利于数字信号的传输。

对此,可以通过对数字基带信号预先进行“随机化”(加扰)处理,使得信号频谱在通带内平均化,改善数字信号的传输;然后在接受端进行解扰操作,恢复到原来的信号。

伪随机序列广泛应用与这类加扰与解扰操作中。

我们下面用DSP BUILDER来构建一中伪随机序列发生器——m序列发生器,这是一种很常见的伪随机序列发生器,可以由线性反馈器件来产生,如下图:其特征多项式为:()∑==ni i i x C x F 0注:其中的乘法和加法运算都是模二运算,即逻辑与和逻辑或。

可以证明,对于一个n 次多项式,与其对应的随机序列的周期为。

12−n 接下来我们以为例,利用DSP BUILDER 构建这样一个伪随机序列发生器。

125++x x开Simulink 浏览器。

Simulink我们可以看到在Simulink 工作库中所安装的Altera DSP Builder 库。

2. 点击Simulink 的菜单File\New\Model 菜单项,新建一个空的模型文件。

3. 按照下图在Model编辑器的工作区中放置如下的模型:其中Logical Bit Operator模块在Gate & Control库中,把它拖到工作区中后双击打开参数设置对话框,设置成2输入异或门。

为了能够在Matlab中获得仿真结果,可以给输出再添加一个示波器Scope,这个模型在Simulink标准库的Sources库中。

2.4 m序列产生器的设计原理m序列是最长线性反馈移位寄存器序列,其产生方法比较简单,可以通过移位寄存器的级联实现任意m序列,本文是结合FPGA芯片的结构特点,以Altera 的QuartusⅡ软件为开发平台,设计出了m序列产生器。

通过FPGA平台,我们可以采用硬件描述语言VHDL语言来实现m序列产生器,也可以通过输入原理图来实现m序列产生器,也可以通过两者的结合来实现m序列产生器。

由于m 序列产生器的实现方法已经能够成熟,本文采用输入原理图的方法实现m 序列产生器的仿真设计。

利用n级移位寄存器可以产生长度为2n-1的m序列。

m序列的设计主要解决的问题是寻求系统的特征多项式为本原多项式的过程,部分本原多项式可以通过查表方法很方便的得到。

本文通过设计一个码长为L=31的m序列,来说明任意m序列产生器如何进行仿真设计。

由码长为31可知道所需的移位寄存器的数目为5,特征多项式的系数通过查表可以选择为100101,110111,111101三个反馈系数,可以从中选择100101来构成m序列产生器。

则特征多项式系数取值为C 5=C2=C=1,C4=C3=C1=0.根据特征多项式就可以构造出该m序列,图5就是L=31的m序列产生器的原理图。

图5 L=31的m序列产生器图5利用D触发器级联的方式完成移位寄存器的功能, CLRN是清零信号,低电平有效。

在系统初始时,CLRN置低电平使系统清零,D触发器的输出状态均为低电平,当CLRN置高时新非零值被置入。

CLK为外界时钟脉冲信号,当CLK 上升沿来临时实现移位功能。

通过异或门将反馈接入系统的输入端,反馈系数根据特征多项式的系数来断定是否接入反馈,在模2加后面加入一个非门,避免了m序列产生器输出静止的状态,如不加非门直接接入反馈到输入端,系统无法自动运动起来,造成输出序列进入了全“1”的静止状态,这样就无法产生m序列。

图中的Q1-Q5是五个D触发器的输出,这些点均可得到同宗序列,只序列的初始相位不同而已。

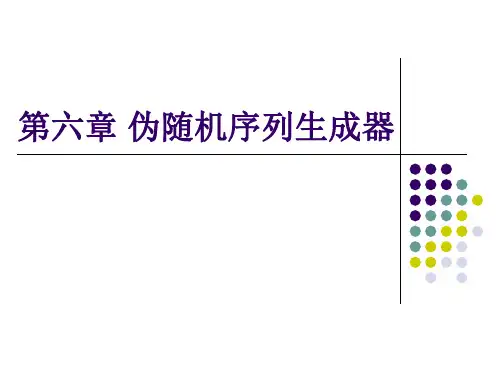

实验七伪随机序列发生器设计一、实验目的1.掌握伪随机序列(m序列)发生器的基本原理和设计方法;2.深入理解VHDL中signal和variable的不同及其应用;二、设计描述及方法1.伪随机序列概述在扩展频谱通信系统中,伪随机序列起着十分关键的作用。

在直接序列扩频系统得发射端,伪随机序列将信息序列的频谱扩展,在接收端,伪随机序列将扩频信号恢复为窄带信号,进而完成信息的接收。

m序列又称为最长线形反馈移位寄存器序列,该序列具有很好的相关性能。

m序列发生器的基本结构为:其中(C r,C r-1,…,C0)为反馈系数,也是特征多项式系数。

这些系数的取值为“1”或“0”,“1”表示该反馈支路连通,“0”表示该反馈支路断开。

下图为实际m序列发生器的电路图:图中利用D触发器级联的方式完成移位寄存器的功能。

在系统清零后,D触发器输出状态均为低电平,为了避免m序列发生器输出全“0”信号,图中在“模二加”运算后添加了一个“非门”。

从图中A、B、C、D四个节点均可得到同一m序列,只是序列的初始相位不同。

特征多项式系数决定了一个m序列的特征多项式,同时也决定了一个m序列。

下表给出了部分m 序列的反馈系数(表中的反馈系数采用八进制表示)2.电路设计基本方法本实验要设计一个寄存器级数为5的m序列发生器,从m序列发生器反馈系数表可知,有三个反馈系数可选,即可以产生三种不同的m序列;在以下设计的接口描述中choice(1 downto0)为m序列选择输入信号,clk为时钟输入信号,reset为复位信号,psout为m序列输出信号。

三、程序代码library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mps isport (clk,reset : in std_logic;choice : in std_logic_vector(1 downto 0);psout: out std_logic );end mps;architecture behave of mps issignal a :std_logic_vector(4 downto 0);signal k:std_logic;beginprocess(clk,reset,choice,a)begincase choice iswhen "00"=> k<=not(a(3) xor a(2));when "01"=> k<=not(a(4) xor a(3)xor a(2)xor a(0));when "10"=> k<=not(a(4) xor a(2)xor a(1)xor a(0));when others =>k<='X';end case;if clk'event and clk='1' thena(0)<=k;for i in 1 to 4 loopa(i)<=a(i-1);end loop;end if;if(reset='1') thena<="00000";end if;end process;psout<=a(4);end behave;四、功能仿真五、RTL级电路。

8位伪随机数列发生器天津工业大学理学院XXXXXXXXXX2011年12月09日背景如果一个序列,一方面它是可以预先确定的,并且是可以重复地生产和复制的;一方面它又具有某种随机序列的随机特性(即统计特性),我们便称这种序列为伪随机序列。

因此可以说,伪随机序列是具有某种随机特性的确定的序列。

它们是由移位寄存器产生确定序列,然而他们却具有某种随机序列的随机特性。

因为同样具有随机特性,无法从一个已经产生的序列的特性中判断是真随机序列还是伪随机序列,只能根据序列的产生办法来判断。

伪随机序列系列具有良好的随机性和接近于白噪声的相关函数,并且有预先的可确定性和可重复性。

这些特性使得伪随机序列得到了广泛的应用,特别是在CDMA系统中作为扩频码已成为CDMA技术中的关键问题。

伪随机序列的特性对系统的性能有重要的影响,因此有必要了解和掌握伪随机序列的的概念和特性。

原理伪随机数列的概念与特性伪随机数列也称作PN码。

它具有近似随机数列(噪声)的性质,它的相关函数接近白噪声的相关函数 (Δ函数 ),即有窄的高峰或宽的功率谱密度 ,使它易于从其他信号或干扰中分离出来。

而又能按一定的规律(周期)产生和复制的序列。

因为随机数列是只能产生而不能复制的,所以称其为“伪”随机数列。

广泛应用于通信、雷达、导航等重要的技术领域。

近年来 ,在自动控制、计算机、声学、光学测量、数字式跟踪和测距系统 ,以及数字网络系统的故障分析检测也得到广泛的应用。

伪随机数列具有这样的特点:(1)每个周期中,“1”码出现2n-1次,“0”码出现2n-1次,即0、1出现概率几乎相等。

(2)序列中连1的数目是n,连0的数目是n-1。

(3)分布无规律,具有与白噪声相似的伪随机特性。

M序列m序列码发生器是一种反馈移位型结构的电路,它由n位移位寄存器加异或反馈网络组成,其序列长度M=2n-1,只有一个多余状态即全0状态,所以称为最大线性序列码发生器。

由于其结构已定型,且反馈函数和连接形式都有一定的规律,因此利用查表的方式就设计出m序列码。

伪随机数生成器系统熵什么是伪随机数生成器?伪随机数生成器(Pseudo Random Number Generator, PRNG)是一种算法或设备,通过一系列的计算步骤生成看似随机的数值序列。

与真随机数生成器(True Random Number Generator, TRNG)不同,伪随机数生成器是基于确定性的算法生成的,因此所获得的随机数实际上是可以重复的(在给定相同种子的情况下)。

尽管伪随机数生成器的输出序列在实际应用中足够随机,但它们并不是真正的“随机”。

伪随机数生成器的原理伪随机数生成器通常基于数学算法,如线性同余法或补码运算等。

这些算法利用初始种子(seed)作为输入,然后通过一系列复杂的计算步骤,生成随机的数字序列。

这个序列可以作为随机数在各种应用中使用,例如模拟实验、加密、统计分析等。

伪随机数生成器的关键问题是如何在存在确定性算法的情况下,生成看似随机的数字序列。

为了达到这个目标,伪随机数生成器通常使用一个大的周期(Period),即在输出序列中循环重复的次数非常大。

这样,在给定初始种子的情况下,每次使用伪随机数生成器所生成的数值序列都会是看似随机的,从而满足实际应用的需求。

然而,由于伪随机数生成器是基于确定性算法,它们的输出序列实际上是可以被预测的。

只要知道生成算法和初始种子,就可以重复生成相同的随机数序列。

因此,在一些应用中,特别是需要高度安全性和随机性的领域(如密码学),伪随机数生成器并不适用。

系统熵与伪随机数生成器在伪随机数生成器中,系统熵(Entropy)是一个重要概念。

系统熵可以看作是伪随机数生成器输出序列的随机性度量,即衡量其接近真随机序列的程度。

系统熵通常用比特(bit)表示,即一个序列可以有多少位被称为“真随机”。

系统熵的计算是通过考察输出序列中的统计特征来实现的。

比如,伪随机数生成器生成的随机序列在理想情况下应具有均匀的分布、独立性和长周期性。

如果输出序列具备这些特征,那么它越接近真随机序列,系统熵就越高。

伪随机序列发生器设计伪随机序列发生器(PRNG)是一种通过算法生成的看似随机的数字序列。

与真随机序列不同,伪随机序列是在一定条件下按照确定性算法生成的。

在计算机系统中,PRNG具有广泛的应用,包括密码学、模拟、游戏等领域。

本文将讨论如何设计一个伪随机序列发生器。

1.随机性的度量:在设计PRNG之前,我们需要了解随机性的度量。

一个好的伪随机序列发生器应该具有高周期性(周期长度大),均匀性(数字出现的频率相似)和不相关性(序列中的数字之间没有明显的关联)。

周期指的是序列重复之前所产生的数字数量。

均匀性可以通过观察数字出现的频率和统计分析来评估。

不相关性指的是序列中的任意两个数字之间没有明显的关联。

2.线性反馈移位寄存器(LFSR):LFSR是一种常见的PRNG设计方法。

它由一个位寄存器和一些异或门组成。

位寄存器中的每个位都线性地与寄存器中的其他位进行异或运算,并且每次循环位寄存器向右移位。

输入位是通过将一些位与1或0常量进行异或来确定的。

3.LFSR的优化:为了改善LFSR的性能,在设计中可以考虑一些优化措施。

一种常见的优化措施是增加反馈函数的复杂性。

通过使用非线性函数,可以在相同的位数下获得更长的周期。

另一个优化措施是根据需要选取适当的位数。

位数越大,周期越长,但计算成本也增加。

4.添加非线性元素:为了进一步提高伪随机序列的质量,我们可以添加一些非线性元素。

一种方法是使用置换函数。

置换函数将输入映射到不同的输出,从而增加了数字之间的不相关性。

另一种方法是使用哈希函数。

哈希函数将输入的随机性扩展到更大的空间中,并通过混淆输入来减少数字之间的关联。

5.分析和测试:设计一个PRNG后,我们需要对其进行分析和测试。

常用的测试方法包括统计测试、重复序列测试和关联测试。

统计测试可以用于检查输出数字的频率。

重复序列测试可以用于验证序列中是否存在重复数字。

关联测试则是用于检查序列中数字之间的关联性。

总结:设计一个高质量的伪随机序列发生器需要考虑随机性度量、LFSR和优化、非线性元素的添加以及分析和测试的步骤。

伪随机序列发生器设计

伪随机序列发生器(PRNG)是生成伪随机数字序列的算法,用于实现

一种统计分布的结果。

它与真正随机序列发生器(TRNG)有所不同,它会

生成完全随机的序列。

伪随机序列发生器(PRNG)一般用于实现加密算法、在游戏中实现随机数据,以及在模拟环境中实现随机事件等多种用途。

1)伪随机序列发生器的硬件部分:目前伪随机序列发生器均采用数

字电路来实现,一般是采用静态只读存储器(SRAM)实现,可以提供高速、稳定和可靠的性能。

2)伪随机序列发生器的算法:伪随机序列发生器需要一个有效的算

法来生成伪随机数字。

比较常用的算法有线性同余法、梅森旋转法、高斯

随机数法等。

3)伪随机序列发生器的参数:伪随机序列发生器需要选择适当的参

数来实现随机序列的变化,可以选择常数、Seed值、基量值等。

4)伪随机序列发生器的测试:需要对伪随机序列发生器进行充分的

测试,以确保它的算法是有效的,能够生成随机数字,而且经过测试不会

有规律性。

总而言之,伪随机序列发生器的设计需要考虑硬件部分、算法、参数

以及测试等多个要素,以确保它能够有效地生成伪随机数字,而且不会有

规律性。

伪随机生成器的构造1. 什么是伪随机生成器?伪随机生成器是一种算法或者程序,用于生成看似随机但实际上是按照某种规律生成的数字序列。

这些数字序列在统计特性上表现得很像真正的随机数序列,但却是可重复的。

2. 伪随机生成器的应用伪随机生成器在计算机科学和应用领域有广泛的应用,例如密码学、模拟实验、游戏开发等。

它们能够为这些应用提供一组看似随机但又可控的数字序列,满足不同应用的需求。

3. 伪随机生成器的构造原理伪随机生成器的构造需要考虑以下几个重要的原理:3.1 初始种子伪随机生成器需要一个初始种子作为生成随机数的起点。

种子可以是一个任意的数字或者一组数字,它们需要具备足够的随机性才能保证生成的随机序列具有良好的统计特性。

3.2 状态转移函数伪随机生成器通过一个状态转移函数将当前的状态转换为下一个状态。

这个函数通常会涉及到一些数学运算,例如乘法、加法、取模等。

状态转移函数的设计需要保证生成的随机序列能够尽可能接近真正的随机数序列。

3.3 周期长度伪随机生成器生成的随机序列通常会有一个周期,即在某个时刻开始,经过若干次状态转移后又回到了相同的状态。

周期的长度决定了伪随机序列的重复周期。

较长的周期长度意味着生成的随机序列更不容易被预测和猜测。

伪随机生成器需要经过一系列的随机性测试来验证生成的随机序列是否满足要求。

常见的测试方法有频数统计、跨度测试、相关性测试等。

通过这些测试,可以评估伪随机生成器的质量和性能。

4. 常见的伪随机生成器算法现实中有许多常见的伪随机生成器算法,其中一些被广泛应用于各个领域。

以下是几种常见的算法:4.1 线性同余法线性同余法是最简单也是最常见的伪随机生成器算法之一。

它基于一个线性递推方程,将当前的状态转换为下一个状态。

该算法的周期长度依赖于所选的参数,需要合理选择参数以获取较长的周期。

4.2 梅森旋转算法梅森旋转算法是一类基于矩阵运算和位操作的伪随机生成器算法。

因其较高的性能和周期长度,被广泛应用于科学计算和密码学领域。