2007年C题 数字存储示波器_全国大学生竞赛山东赛区组委会

- 格式:doc

- 大小:1005.11 KB

- 文档页数:12

2007年全国电子设计大赛C题数字存储示波器题目任务:设计一简易数字存储示波器1.总体框架图:2.题目要求指标(1) 信号频率范围: 10Hz~10MHz;要求输入电阻: Ri>100kΩ;(2) 垂直点数:32级/div;水平点数:20点/div;(3) 垂直灵敏度:0.01V/div ,0.1V/div,1V/div,误差≤5% ;(4) 水平扫瞄速度: 0.2s/div,0.2ms/div,20μs/div,误差≤5%;(5) 触发功能要求:单次触发、扩展、内触发、上升沿、电平可调;(6) 显示波形无明显失真;(7) 产生100kHz,0.3V的校准方波;报告主要内容:1.对赛题要求的分析2.具体实现方案讨论及器件参数计算3.模拟部分电路设计及数字控制部分软件编写4.安装调试及所遇到的问题5.测试结果分析6.总结1. 对赛题要求的分析(1) 工作流程:A/D采集、双口RAM存储、D/A显示。

需要器件:A/D、单片机、D/A、FPGA等主要器件;(2) 内触发上升沿、触发电平可调;扫描速度 0.2s/div,0.2ms/div,20 μ s/div;垂直灵敏度0.1V/div, 1V/div,0.01V/div移动扩展。

要具有控制功能:1.控制器 2. 人机接口2. 具体方案讨论2.1 采样方式的选择实时采样和等效时间采样:实时采样即按照AD的采样速率对波形进行满足奈奎斯特采样速率的采样;等效采样是在周期信号频率过高,AD速率无法满足奈奎斯特采样速率时,间隔整数倍周期T+最小采样间隔时间对信号进行采样。

具体示意图见下:题中要求输入信号频率范围:10Hz~10MHz,样点直接恢复方式为至少20点/周期, A/D 转换速率应小于1Ms/s。

故对于高频信号(大于500KHz),应采用等效采样方式,低频信号采用实时采样方式。

2.2 控制器件的选择1.对控制器件的要求* AD采集速率:高达1000kHz(1 μ s),低至 20ms;(决定于扫描速度)* 样点恢复速率:DA时钟为10MHz,绝对满足输出波形要求。

大学生电子设计竞赛题目方向1)仪器仪表方向:音频信号分析仪:2021年a题数字取样示波器:2021年c题简易频谱分析仪:2021年c题简易逻辑分析仪:2021年d题低频相位测量仪:2021年c题数字存储示波器:2001年b题频率特性测量仪:1999年c题数字工频多用表:1999年b题简易数字频率计:1997年b题轻便rlc测量仪:1995年d题仪器仪表方向训练重点:内容:包含信号产生、采集、存储、分析、处理、显示、控制等信号处理环节中的大部分或全部。

类型:分成时域分析处置和频域分析处置两大类。

难点:强调速度、处理能力、显示性能等。

需要通过构建新技术硬件平台及运用信号处理算法来实现。

系统中的部分任务需要在训练阶段完成。

训练:dds任一信号产生、高速/宽带演示电路、滤波器、高速adc/dac取样与录像、高速数据存储(fifo)、算法(fft、卷积、有关、数字滤波等)、表明技术(lcd、绘图、实时曲线等)、弱实时性mammalian多任务软件设计、fpga/cpld与单片机的USB、仪器仪表原理、各类电参数测量、等内容。

2)电路系统方向:宽带直流放大器:2021年c题轻便程控滤波器:2021年d题正弦信号发生器:2021年a题宽带放大器:2021年b题压往下压l/c振荡器:2021年a题任一波形发生器:2001年a题轻便测量放大器:1999年a题录音与录像系统:1999年e题新颖信号源制作:1995年b题电路系统方向训练重点:内容:偏重概念和指标。

涉及到各类经典单元模块电路,及其基本概念、基本原理和新实现方法、性能指标测试方法等。

类型:分成功能型(轻在新方法)和指标型(轻在崭新设计思路)两大类。

难点:特别强调指标,通常经典设计、通用型ic就是难以完成的。

训练:(程控)放大器、(程控)滤波器、振荡器、dds任一信号产生、基本演示调理电路、电性能指标测试(电阻、增益、频宽…)、拓展设计思路等。

3)功率电子方向:光伏发电演示装置:2021年a题电能搜集充电器:2021年e题开关型稳压电源:2021年e题数控恒流源:2021年f题三相正弦变频电源:2021年g题高效d类放大器:2001年d题直流稳定电源:1997年a题实用音频放大器:1995年a 题功率电子方向训练重点:内容:小电流、大功率、三相电、斩波、dc-ac低电压、dc-dc开关电源、变频驱动、class-d功放、光伏发电、并网、mppt算法,等电力电子领域的新技术。

2015年全国大学生电子设计竞赛题目【本科组】双向DC-DC变换器(A题)风力摆控制系统(B题)多旋翼自主飞行器(C题)增益可控射频放大器(D题)80MHz-100MHz频谱分析仪(E题)数字频率计(F题)短距视频信号无线通信网络(G题)第一届(1994年)第一届(1994年)全国大学生电子设计竞赛A.简易数控直流电源B.多路数据采集系统第二届(1995年)第二届(1995年)全国大学生电子设计竞赛A.实用低频功率放大器B.实用信号源的设计和制作C.简易无线电遥控系统D.简易电阻、电容和电感测试仪第三届(1997年)第三届(1997年)全国大学生电子设计竞赛A.直流稳定电源B.简易数字频率计C.水温控制系统D.调幅广播收音机第四届(1999年)第四届(1999年)全国大学生电子设计竞赛A.测量放大器B.数字式工频有效值多用表C.频率特性测试仪D.短波调频接收机E.数字化语音存储与回放系统第五届(2001年)第五届(2001年)全国大学生电子设计竞赛A.波形发生器B.简易数字存储示波器C.自动往返电动小汽车D.高效率音频功率放大器E.数据采集与传输系统F.调频收音机第六届(2003年)第六届(2003年)全国大学生电子设计竞赛A.电压控制LC振荡器B.宽带放大器C.低频数字式相位测量仪D.简易逻辑分析仪E.简易智能电动车F.液体点滴速度监控装置第七届(2005年)第七届(2005年)全国大学生电子设计竞赛A.正弦信号发生器B.集成运放测试仪C.简易频谱分析仪D.单工无线呼叫系统E.悬挂运动控制系统F.数控恒流源G.三相正弦波变频电源第八届(2007年)第八届(2007年)全国大学生电子设计竞赛A.音频信号分析仪B.无线识别C.数字示波器D.程控滤波器E.开关稳压电源F.电动车跷跷板G.积分式直流数字电压表H.信号发生器I.可控放大器J.电动车跷跷板第九届(2009年)第九届(2009年)全国大学生电子设计竞赛A.光伏并网发电模拟装置B.声音导引系统C.宽带直流放大器D.无线环境监测模拟装置E.电能收集充电器F.数字幅频均衡功率放大器G.低频功率放大器H.LED点阵书写显示屏I.模拟路灯控制系统第十届(2011年)A.开关电源模块并联供电系统B.基于自由摆的平板控制系统C.智能小车D. LC 谐振放大器E.简易数字信号传输性能分析仪F.帆板控制系统G.简易自动电阻测试仪H.波形采集、存储与回放系统第十一届(2013年)A.单相AC-DC变换电路B.四旋翼自主飞行器C.简易旋转倒立摆及控制装置D.射频宽带放大器E.简易频率特性测试仪F.红外光通信装置G.手写绘图板J.电磁控制运动装置K.简易照明线路探测仪L.直流稳压电源及漏电保护装置第十二届(2015年)【本科组】双向DC-DC变换器(A题)风力摆控制系统(B题)多旋翼自主飞行器(C题)增益可控射频放大器(D题)80MHz-100MHz频谱分析仪(E题)数字频率计(F题)短距视频信号无线通信网络(G题)【高职高专组】LED闪光灯电源(H题)风板控制装置(I题)小球滚动控制系统(J题)获奖状况。

2013年东南大学大学生电子设计竞赛题

C题:波形采集、存储与回放系统

一、任务

设计并制作一个波形采集、存储与回放系统,示意图如图所示。

该系统能采集周期信号波形,要求系统断电恢复后,能连续回放已采集的信号。

二、要求

1.基本要求

(1)能完成对输入信号的采集、存储并在示波器上回放波形。

输入信号幅度为50mV~4V范围可变(信号在采集期间不变),频率约1kHz。

要求系统

回放的波形质量尽量好。

(2)采集、回放时能测量并显示信号的最大值、最小值和信号的周期。

回放信号无明显失真,原信号与回放信号电平之差的绝对值≤20%,周期之差

的绝对值≤5%。

(3)系统内不允许使用电池。

2. 发挥部分

(1)可以存储两次采集的信号,回放时用按键或开关选择显示指定信号波形。

(2)制作一套波形显示装置,能显示信号波形和采集回放信号波形。

(3)自由发挥。

三、说明

1.本系统处理的正弦波信号频率范围限定在10Hz~10kHz,三角波信号频率范围限定在10Hz ~2kHz,方波信号频率范围限定在10Hz ~1kHz。

2.采集、回放时显示的周期和幅度应是信号的实际测量值,规定采用十进制数字显示,周期以“ms”为单位,幅度以“mV”为单位。

四、评分标准。

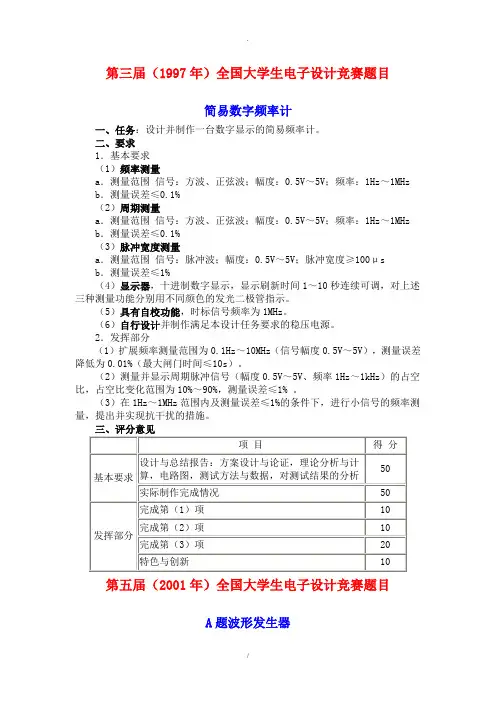

第三届(1997年)全国大学生电子设计竞赛题目简易数字频率计一、任务:设计并制作一台数字显示的简易频率计。

二、要求1.基本要求(1)频率测量a.测量范围信号:方波、正弦波;幅度:0.5V~5V;频率:1Hz~1MHz b.测量误差≤0.1%(2)周期测量a.测量范围信号:方波、正弦波;幅度:0.5V~5V;频率:1Hz~1MHz b.测量误差≤0.1%(3)脉冲宽度测量a.测量范围信号:脉冲波;幅度:0.5V~5V;脉冲宽度≥100μsb.测量误差≤1%(4)显示器,十进制数字显示,显示刷新时间1~10秒连续可调,对上述三种测量功能分别用不同颜色的发光二极管指示。

(5)具有自校功能,时标信号频率为1MHz。

(6)自行设计并制作满足本设计任务要求的稳压电源。

2.发挥部分(1)扩展频率测量范围为0.1Hz~10MHz(信号幅度0.5V~5V),测量误差降低为0.01%(最大闸门时间≤10s)。

(2)测量并显示周期脉冲信号(幅度0.5V~5V、频率1Hz~1kHz)的占空比,占空比变化范围为10%~90%,测量误差≤1% 。

(3)在1Hz~1MHz范围内及测量误差≤1%的条件下,进行小信号的频率测量,提出并实现抗干扰的措施。

第五届(2001年)全国大学生电子设计竞赛题目A题波形发生器一、任务设计制作一个波形发生器,该波形发生器能产生正弦波、方波、三角波和由用户编辑的特定形状波形。

示意图如下:二、要求1.基本要求(1)具有产生正弦波、方波、三角波三种周期性波形的功能。

(2)用键盘输入编辑生成上述三种波形(同周期)的线性组合波形,以及由基波及其谐波(5次以下)线性组合的波形。

(3)具有波形存储功能。

(4)输出波形的频率范围为100Hz~20kHz(非正弦波频率按10次谐波计算);重复频率可调,频率步进间隔≤100Hz。

(5)输出波形幅度范围0~5V(峰-峰值),可按步进0.1V(峰-峰值)调整。

(6)具有显示输出波形的类型、重复频率(周期)和幅度的功能。

简易多功能计数器(F题)参赛学生:宗露林荣逸吕彦锋信息科学与工程学院参赛学校:哈尔滨工业大学(威海)指导老师:毛兴鹏摘要随着科学技术的发展,频率和时间测量的意义已日益显著,不仅与人们日常生活息息相关,而且在当代高科技中更是显得重要。

可编程逻辑器件和EDA计数给今天的硬件系统设计者实现了强而有力的工具,使得电子系统设计方法发生了质的变化。

本文论述了电子计数式简易多功能计数器的原理、设计、应用及误差特性。

本计数器以ATmega128单片机为控制核心,由FPGA模块、键盘输入模块、液晶显示模块、温度测量模块等功能模块组成,实现了周期、频率、时间间隔的测量等功能。

在设计方法上,由传统的“电路设计—硬件搭试—焊机”的传统方式到“功能设计—软件模拟—下载”的电子自动化模式,以软件设计为主,硬件设计为辅的指导思想,将复杂硬件软件化,从而大大提高了系统设计的灵活性和稳定性。

关键字:电子计数式,测量精度,可编程逻辑器件,AVR单片机,门控信号Multi-function CounterABSTRACTThe FPGA(Field Programmable Gate Array) provides a fast, accurate and flexible solution for digital system design. This paper discusses the design flow, scheme selection, and error control and analysis of a multi-function counter. Based on ATmega128 as the microcontroller, it consists of the FPGA module, keyboard modules, liquid crystal display (LCD) modules, temperature measurement module etc. This system can be applied in the period, frequency, interval measurements. As for the design methods, the "functional design - software simulation - Download" electronic automatic mode takes the place of the traditional "circuit design - hardware test ride - welder" methods. It mainly depends on the EDA Tools, supplemented by the hardware design and in this way it simplifies the hardware design, greatly improving the flexibility and stability of the system.Key words: Frequency Meter, Period Meter, Counter, Measurement Accuracy, FPGA, AVR目录正文1.1 设计要求1.1基本设计要求--------------------------------------------------------11.1.2 发挥设计要-------------------------------------------------------11.2 测量原理1.2.1频率测量原理------------------------------------------------------11.2.2 时间间隔----------------------------------------------------------11.2.3 系统测量原--------------------------------------------------------21.3 系统总体方案1.3.1 系统总体方案的比较与---------------------------------------------21.3.2 系统总框图-------------------------------------------------------31.4 各模块硬件电路实现1.4.1 FPGA模块---------------------------------------------------------31.4.1.1 频率测量-------------------------------------------------------31.4.1.2时间间隔测量---------------------------------------------------41.4.1.3 其他-----------------------------------------------------------51.4.2信号预处理--------------------------------------------------------61.4.3 AD采样测幅值-----------------------------------------------------71.4.4 温度测量模块------------------------------------------------------71.4.5 键盘输入模块------------------------------------------------------71.4.6 液晶显示模块------------------------------------------------------71.4.7 语音报时模块------------------------------------------------------71.4.8 自制电源----------------------------------------------------------71.4.9浮点数除法运算----------------------------------------------------81.5 系统软件设计2.5.1 主程序流程图 -----------------------------------------------------82.5.2 界面设计 ---------------------------------------------------------91.6 测试与结果分析2.6.1 参数测量结果-----------------------------------------------------102.6.2 误差与结果分析---------------------------------------------------111.7设计总结------------------------------------------------------------121.8参考资料------------------------------------------------------------12附录1.1元件清单------------------------------------------------------------131.2电路设计原理图及相关仿真结构----------------------------------------131.3源程序代码---------------------------------------------------------13正文1.1设计要求1.1.1 基本设计要求(1)具有测量周期、频率、时间间隔的功能;(2)可以用键盘选择上述三种功能;(3)周期、时间间隔测量:0.1mS~1S,误差≦0.1%;频率测量:1Hz~200KHz,误差0.1%;(4)能够显示至少六位数码,并自制计数器电源1.1.2 发挥设计要求(1)周期、时间间隔测量:1µS~10S,误差≦0.1%;频率测量:0.01Hz~10MHz,误差≤0.1%;(2)可以记忆10个历史测量数据,且能够随时查看;(3)实现语音报数功能,并且显示被测信号的峰值;(4)其他(如温度、时间等功能)。

8.2 赛前题目分析和准备8.2.1赛前公布的基本仪器和主要元器件清单全国大学生电子设计竞赛组委会专家组在电子设计竞赛开始的前一周都会在网上公布本次全国大学生电子设计竞赛需要的基本仪器和主要元器件清单,以便参赛学校做好准备。

通过对所公布的基本仪器和主要元器件清单进行分析,可以得到一些竞赛题目的信息。

(以下是“2003年全国大学生电子设计竞赛基本仪器和主要元器件清单”)2003年全国大学生电子设计竞赛基本仪器和主要元器件清单一、基本仪器清单20MHz普通示波器(双通道,外触发输入,有X轴输入,可选带Z轴输入)60MHz双通道数字示波器低频信号发生器(1Hz~200kHz)信号发生器(1kHz~15MHz)高频信号发生器(1MHz~35MHz)频率特性测量仪(可选)数字相位计(可选)低频毫伏表高频毫伏表普通频率计3位半数字万用表电感、电容测试仪(或Q表)秒表单片机开发系统及EDA开发系统二、主要元器件清单单片机最小系统板(仅含单片机芯片、键盘与显示装置、存储器)可编程逻辑器件下载板(仅含可编程芯片、下载电路、配置存储器)A/D、D/A变换器运算放大器、电压比较器可编程逻辑器件显示器件电动玩具车(外形尺寸:长≤35cm;宽≤15cm)小型电动机开关二极管高频变容二极管小型继电器模拟开关高频磁芯传感器(光电传感器、超声传感器、金属探测传感器、红外传感器等)全国大学生电子设计竞赛组委会专家组2003年9月8日公布8.2.2赛前题目分析1. 分析方法分析方法可以采用基本要素组合法,一是分析所需要的仪器仪表,二是分析所需要的元器件,将两者结合进行综合分析。

以2003年公布的全国大学生电子设计竞赛基本仪器和主要元器件清单为例:从信号发生器和示波器的频率范围可见,信号频率范围不会超过35MHz,最高也不会超过60MHz。

信号波形有正弦波和方波等。

使用双踪示波器,表示作品制作时需要同时观测两路信号。

使用数字示波器,表示作品制作时需要直接读取一些数据。

历届全国大学生电子设计竞赛试题第一届(1994年)全国大学生电子设计竞赛题目(1)简易数控直流电源(A题)(2)多路数据采集系统(B题)第二届(1995年)全国大学生电子设计竞赛题目(1)实用低频功率放大器(A题)(2)实用信号源的设计和制作(B题)(3)简易无线电遥控系统(C题)(4)简易电阻、电容和电感测试仪(D题)第三届(1997年)全国大学生电子设计竞赛题目(1)直流稳压电源(A题)(2)简易数字频率计(B题)(3)水温控制系统(C题)(4)调幅扩播收音机(D题)第四届(1999年)全国大学生电子设计竞赛题目(1)测量放大器设计(A题)(2)数字式工频有效值多用表(B题)(3)频率特性测量仪设计(C题)(4)短波调频接收机设计(D题)(5)数字化语音存储与回放系统(E题)第五届(2001年)全国大学生电子设计竞赛题目(1)波形发生器(A题)(2)简易数字存储示波器(B题)(3)自动往返电动小汽车(C题)(4)高效率音频功率放大器(D题)(5)数据采集与传输系统(E题)(6)调频收音机(F题)第六届(2003年)全国大学生电子设计竞赛题目(1)电压控制LC振荡器(A题)(2)宽带放大器(B题)(3)低频数字式相位测量仪(C题)(4)简易逻辑分析仪(D题)(5)简易智能电动车(E题)(6)液体点滴速度监控装置(F题)第七届(2005年)全国大学生电子设计竞赛题目(1)正弦信号发生器(A题)(2)集成运放测试仪(B题)(3)简易频谱分析仪(C题)(4)单工无线呼叫系统(D题)(5)悬挂运动控制系统(E题)(6)数控恒流源(F题)(7)三相正弦波变频电源(G题)第八届(2007年)全国大学生电子设计竞赛题目(1)音频信号分析仪(八)【本科组】(2)无线识别(B)【本科组】(3)数字示波器(C)【本科组】(4)程控滤波器(D)【本科组】(5)开关稳压电源(E)【本科组】(6)电动车跷跷板(F)【本科组】(7)积分式直流数字电压表(G)【高职高专组】(8)信号发生器(三)【高职高专组】(9)可控放大器(D【高职高专组】(10)电动车跷跷板(J)【高职高专组】第九届(2009年)全国大学生电子设计竞赛题目(1)光伏并网发电模拟装置(A题)【本科组】(2)声音导引系统(B题)【本科组】(3)宽带直流放大器(C题)【本科组】(4)无线环境监测模拟装置(D题)【本科组】(5)电能收集充电㈱(E题)【本科组】(6)数字幅频均衡的功率放大器(F题)【本科组】(7)低频功率放大器(G题【高职高专组D(8)LED点阵书写显示屏(H题【高职高专组D (9)模拟路灯控制系统Q题【高职高专组】)。

2007年全国大学生电子设计竞赛试题参赛注意事项(1)2007年9月3日8:00竞赛正式开始。

本科组参赛队只能A、B、C、D、E、F题目中任选一题;高职高专组参赛队原则上在G、H、I、J题中任选一题,也可以选择其他题目。

(2)参赛队认真填写《登记表》内容,填写好的《登记表》交赛场巡视员暂时保存。

(3)参赛者必须是有正式学籍的全日制在校本、专科学生,应出示能够证明参赛者学生身份的有效证件(如学生证)随时备查。

(4)每队严格限制3人,开赛后不得中途更换队员。

(5)竞赛期间,可使用各种图书资料和网络资源,但不得在学校指定竞赛场地外进行设计制作,不得以任何方式与他人交流,包括教师在内的非参赛队员必须迴避,对违纪参赛队取消评审资格。

(6)2007年9月6日20:00竞赛结束,上交设计报告、制作实物及《登记表》,由专人封存。

音频信号分析仪(A题)【本科组】一、任务设计、制作一个可分析音频信号频率成分,并可测量正弦信号失真度的仪器。

二、要求1.基本要求(1)输入阻抗:50Ω(2)输入信号电压范围(峰-峰值):100mV~5V(3)输入信号包含的频率成分范围:200Hz~10kHz(4)频率分辨力:100Hz(可正确测量被测信号中,频差不小于100Hz的频率分量的功率值。

)(5)检测输入信号的总功率和各频率分量的频率和功率,检测出的各频率分量的功率之和不小于总功率值的95%;各频率分量功率测量的相对误差的绝对值小于10%,总功率测量的相对误差的绝对值小于5%。

(6)分析时间:5秒。

应以5秒周期刷新分析数据,信号各频率分量应按功率大小依次存储并可回放显示,同时实时显示信号总功率和至少前两个频率分量的频率值和功率值,并设暂停键保持显示的数据。

2.发挥部分(1)扩大输入信号动态范围,提高灵敏度。

(2)输入信号包含的频率成分范围:20Hz~10kHz。

(3)增加频率分辨力20Hz档。

(4)判断输入信号的周期性,并测量其周期。

历年全国电子设计大赛试题[1]历年全国电子设计大赛试题总汇楼主打印第1 页共57 页历年全国电子设计大赛试题总汇第一届(1994 年)全国大学生电子设计竞赛题目 (3)题目一简易数控直流电源 (3)题目二多路数据采集系统 (4)第二届(1995 年)全国大学生电子设计竞赛题目 (5)题目一实用低频功率放大器 (5)题目二实用信号源的设计和制作 (6)题目三简易无线电遥控系统 (7)题目四简易电阻、电容和电感测试仪 (8)第三届(1997 年)全国大学生电子设计竞赛题目 (9)A 题直流稳定电源 (9)B 题简易数字频率计 (10)C 题水温控制系统 (11)D 题调幅广播收音机* (12)第四届(1999 年)全国大学生电子设计竞赛题目 (13)A 题测量放大器 (13)B 题数字式工频有效值多用表 (14)C 题频率特性测试仪 (16)D 题短波调频接收机 (17)E 题数字化语音存储与回放系统 (18)第五届(2001 年)全国大学生电子设计竞赛题目 (19)A 题波形发生器 (19)B 题简易数字存储示波器 (20)C 题自动往返电动小汽车 (21)D 题高效率音频功率放大器 (22)E 题数据采集与传输系统 (23)F 题调频收音机 (25)第六届(2003 年)全国大学生电子设计竞赛题目 (26)电压控制LC 振荡器(A 题) (26)宽带放大器(B 题) (27)低频数字式相位测量仪(C 题) (28)简易逻辑分析仪(D 题) (30)第2 页共57 页简易智能电动车(E 题) (31)液体点滴速度监控装置(F 题) (33)第七届(2005 年)全国大学生电子设计竞赛题目 (34)正弦信号发生器(A 题) (34)集成运放参数测试仪(B 题) (34)简易频谱分析仪(C 题) (37)单工无线呼叫系统(D 题) (38)悬挂运动控制系统(E 题) (39)数控直流电流源(F 题) (41)三相正弦波变频电源(G 题) (42)第八届(2007 年)全国大学生电子设计竞赛题目 (43)音频信号分析仪(A 题)【本科组】 (43)无线识别装置(B 题)【本科组】 (44)数字示波器(C 题)【本科组】 (46)程控滤波器(D 题)【本科组】 (47)开关稳压电源(E 题)【本科组】 (49)电动车跷跷板(F 题)【本科组】 (50)积分式直流数字电压表(G 题)【高职高专组】 (53)信号发生器(H 题)【高职高专组】 (54)可控放大器(I 题)【高职高专组】 (55)电动车跷跷板(J 题)【高职高专组】 (56)第3 页共57 页第一届(1994 年)全国大学生电子设计竞赛题目题目一简易数控直流电源一、设计任务设计出有一定输出电压范围和功能的数控电源。

数字存储示波器海军航空工程学院(烟台)史继炎何高健刘恒涛摘要本题设计一个数字存储示波器,以Xilinx公司20万门FPGA芯片为核心,辅以必要的外围电路(包括信号调理、采样保持、内部触发、A/D转换、D/A转换和I/O模块),利用VHDL语言编程,实现了任意波形的单次触发、连续触发和存储回放功能,并按要求进行了垂直灵敏度和扫描速度的挡位设置。

信号采集时,将外部输入信号经信号调理模块调节到A/D电路输入范围,经A/D转换后送入FPGA内部的双口RAM进行高速缓存,并将结果通过D/A转换送给通用示波器进行显示,完成了对中、低频信号的实时采样和高频信号的等效采样和数据存储回放。

经测试,系统整体指标良好,垂直灵敏度和扫描速度等各项指标均达到设计要求。

关键词:FPGA 实时采样等效采样一、方案选择与论证数字存储示波器系统由信号调理电路、采样保持电路、触发电路、A/D、D/A、X输出电路、Y 输出电路、控制处理器等组成。

方案一:采用80C51单片机为控制核心,其系统框图如图1。

对输入信号进行放大或衰减后,用外接触发电路产生触发信号,通过A/D转换将模拟信号转换成数字信号,再通过单片机将数据锁存至外部RAM,然后由单片机控制将数据送至D/A输出。

图1 方案一系统框图这种方案结构较为简洁,但在满足题目的实时采样频率的要求下,A/D的最高采样速度达1MHz,由普通单片机直接处理这样速率的数据难以胜任,采用高档单片机甚至采用DSP芯片,将大大增加开发的难度。

而且目前常用的外接RAM芯片时钟周期一般为40MHz~50MHz,难以达到高速数据存储的要求。

方案二:用FPGA可编程逻辑器件作为控制及数据处理的核心,外接触发电路实现触发功能,利用FPGA的层次化存储器系统结构,使用FPGA内部集成的基本逻辑功能块配置成双端口同步RAM 对采集信号进行存储,完成设计指标。

其系统框图如图2。

图2 方案二系统框图由于FPGA可在线编程,因此大大加快了开发速度。

电路中的大部分逻辑控制功能都由单片FPGA 完成,多个功能模块如采样频率控制模块、数据存储模块都集中在单个芯片上,大大简化了外围硬件电路设计,增加了系统的稳定性和可靠性。

FPGA的高速性能比其他控制芯片更适合于高速数据采集和处理,而且使用FPGA内部存储模块完成输入信号的量化存储,在存储速度上有着外接RAM 无法比拟的优势。

综上所述比较可知,方案二既可满足题设基本要求又能充分发挥扩展部分,电路简单,易于控制,所以采用该方案。

二、理论分析与计算1、采样方式的选择设计要求示波器输入频率范围较宽,并且实时采样频率只有1MHz,因此要采用等效采样和实时采样两种采样方式。

实时采样是利用A/D时钟对信号直接采样,按照采样定理,采样速率必须高于信号中最高频率的两倍。

等效采样是指对多个信号周期连续采样来复现一个信号波形,采样系统能以扩展的方式复现频率大大超过实时采样频率的信号波形。

题目要求最高实时采样速率小于等1MSa/s,实时采样通常采取每周期采20个点的方法以保证取到一个完整的信号波形。

本设计采用50KHz作为两种采样方式的分界频率,信号频率低于50KHz时采用实时采样方式,当信号频率50KHz 和10MHz之间时采用等效采样方式。

题目要求等效采样速率不小于200 MSa/s,而被测周期信号的最大频率为10MHz,采一个点所需间隔的周期数=等效采样速率/被测周期信号频率,则等效采样时至少需要每20个信号周期采样一个点才能实现等效采样数率大于等于200MHz。

2、垂直灵敏度分析设计要求垂直灵敏度分为1V/div、0.1V/div、2mV/div三档,垂直刻度为8 div。

A/D转换器的输入信号电压幅度为0~4V,当示波器满刻度显示时,被测信号的幅度将分别为:VI1=1V/div×8div=8V,VI2=0.1V/div×8div=0.8,VI3=2mv/div×8div=16mV。

A/D转换器的满刻度输入值为VMAX =4V,程控放大器电路的增益AN=VMAX/ VIN,其中N=1、2、3,对应于3挡不同垂直灵敏度的增益分别为:A1=4/8=0.5;A2=4/0.8=5;A3=4/0.016=250。

从5倍增益到250倍增益所跨越的增益范围非常大,大跨度增益自动调节是程控增益放大电路设计的一个难点,本系统通过软件编程实现增益的步进,很好的解决了这个问题,具体分析见软件详细设计部分。

3、扫描速率分析A/D的转换速率取决于被测信号的频率范围,或DSO对扫描速度的要求,设计要求扫描速度含20ms/div、2μs /div、100 ns/div三挡,并且水平显示分辨率大于等于20点/div,因此对应的采样速率是1ms/点、0.1μs /点、5 ns/点,即要求A/D的等效采样的最高转换速率高于200MSa/s,题目要求A/D的最高转换速率不高于1MSa/s,设计中采用等效采样的方法来实现100 ns/div 、2μs /div两挡的扫描。

三、硬件电路设计系统硬件连接图如图3所示。

图3 系统硬件连接图1、FPGA最小系统板设计FPGA最小系统板采用的是Xilinx公司SpartanII系列的XC2S200-PQ208型20万门芯片,其配置芯片为Xilinx公司的专用配置PROM芯片XCF02S,以实现加电自动配置。

核心板采用5V输入,板上有两块LM317电源芯片分别输出3.3V和2.5V电压。

板上采用100MHz有源晶振,通过内部倍频系统工作时钟可高达200MHz,满足高速设计要求。

核心板140只I/O口全部引出,非常便于与外围器件的连接及系统的扩展。

FPGA最小系统框图如附录1所示。

2、信号调理电路设计AD转换电路对输入模拟信号的幅度范围有一定的要求,因此被测信号输入A/D前需要进行信号调理。

信号调理电路组成框图如图4所示。

图4 信号调理电路组成框图(1)衰减电路设计信号衰减幅度由FPGA通过功率驱动芯片ULN2803来控制。

ULN2803控制继电器的通断,决定了电阻分压网络的衰减倍数,衰减网络电路原理图如附录2所示。

设计任务要求数字示波器的输入阻抗大于1MΩ,在此电路中设计输入电阻R1+R2=1MΩ,衰减10倍则有:R1 =100KΩ,R2=900KΩ。

电容C1,C2在衰减器中起补偿作用,以改善频率响应,避免自激。

设计采用ADI公司的高性能FET输入单电压反馈运算放大器AD8065构成电压跟随电路实现阻抗变换,提高衰减电路输出阻抗。

同时,为了防止过载时器件的损坏,系统中设计了由四个限幅稳压二极管和电阻构成的过载保护电路,将输入信号电压值限制在±2V的范围之间,限幅稳压电路图见附录3所示。

(2)放大电路设计程控增益宽带放大电路由增益变化范围线性连续可调的可控增益放大器AD603组成。

通过FPGA 结合8位D/A转换芯片CA3338E对两片AD603引脚端1的电压进行控制,可获得-20~+60dB范围的增益,远远大于题目250倍的放大要求,两级输出最大电压在4V左右。

两片AD603构成的程控增益控制放大电路如附录4所示。

3、触发电路设计数字存储示波器中触发电路的作用是:在满足触发条件时开始对采集的数据按规定的起点地址进行存储和显示。

触发电路如附录5所示。

高速比较器选用响应时间为20ns的高速低功率快速采样保持放大器LM360。

电阻R2、R3用于调节或选择触发电平,分别为3KΩ和2KΩ,后者为可调电位器,可以在0~2V范围内任意选择触发电平。

4、取样保持电路取样保持芯片选用AD公司生产的快速采样保持放大器AD781。

AD781的快速采样时间为700ns,满足题目对实时采样速率小于等于1MSa/s的要求,采用自校舍正结构,具有极小的保持模式误差,保持误差仅为0.01μV/μs。

同时该芯片无需外接元件与外部调整,具有很好的线性和优良的直流和动态性能,十分适用于高速AD转换器的前端电路。

AD781的输入信号幅度范围为-12V~+12V,采用±12V直流稳压电源供电,内部功能和引脚图如附录6所示。

5、A/D转换电路设计中采用ADI公司生产的快速A/D转换芯片AD9224。

AD9224为28脚SOIC和SSOP封装的模/数转换器;内部采用闪烁式AD及多级流水线式结构,因而不失码,使用方便、准确度高;在单一+5V电源下,它的功耗仅有376mW,信噪比与失真度为±0.7dB,完全满足设计要求。

设计中的参考电压使用内部参考电压,将SENSE与REFCOM引脚短接,此时电压范围为0~4V。

AD9224应用电路如附录7所示。

为减少A/D转换结果的二次谐波,提高信噪比(SNR),A/D芯片前端采用AD8138组成信号调理电路将单端信号转换成差分信号输入。

该放大器的输入阻抗高达6MΩ,可以直接与输入信号相连从而省略隔离放大器,因而可大大精简了电路结构。

AD8138应用电路如附录8所示。

6、D/A转换电路D/A部分由一片14位高速高精度模数转换芯片AD9764和两片8位D/A转换芯片CA3338E组成。

AD9764用作D/AY,将存储的数字信号转换为模拟信号,从而恢复被测信号。

电路设计中的参考电源配置使用内部参考电源,存在于VOUTA 和VOUTB之间的差分电压VDIFF通过一个运算放大器AD8009转换成单端电压输出,电压输出范围为:-3.84V~3.84V。

AD9764应用电路如附录9所示。

设计中一片CA3338E对FPGA输出的程控放大信号进行数模转换,用于对AD603相关引脚的控制,完成程控增益调节功能。

另一片CA3338E作为D/AX用于产生相应扫速和幅度的锯齿波扫描电压使被测信号按照设置的时间关系进行显示,为方便设计和安装调试两片CA3338E选择相同的设计电路。

同时该片芯片完成产生100kHz方波校准信号的功能,功能切换通过拨码开关控制。

CA3338E 应用电路图如附录10所示。

7、直流稳压电源直流稳压电源部分通过开关电源分别获得±12V和+5V的电压。

其中主控模块FPGA 3.3V和2.5V的供电,采用两块三端可调稳压器LM317得到。

LM317应用电路输出电压VO = 1.25(1 + R2/R 1),式中1.25是集成稳压块输出端与调整端之间的固有参考电压VREF,电阻R1常取值120Ω~240Ω,此处选R1为200Ω,经计算,提供3.3V和2.5V电压时R2分别为330Ω和200Ω。

取样保持电路所需±12V供电由外接直流稳压电源提供,A/D和D/A电路的+5V、-5V电压分别由电源稳压芯片MC78M05和MC79M05提供。

稳压电源电路原理图如附录11、附录12所示。