FPGA在数字存储示波器时基电路中的应用

- 格式:pdf

- 大小:75.58 KB

- 文档页数:3

基于FPGA和单片机的数字存储示波器摘要:随着时代的发展,示波器作为电子行业中一种常用的测试工具,在电子技术工作中起着不可替代的作用。

目前新的技术应用越来越多,用户的测试需求不断变化,然而市面上的数字存储示波器大多价格昂贵、体型庞大,很难携带或者安放,对于一些只进行简单测量不太实用。

数字存储示波器是20世纪70年代,发展起来的一种新型示波器。

今后市场的发展让示波器需要面对更多的应用,数字示波器功能集成趋势明显,与此同时,除了追求强大的功能以外,外观精美、款式小巧,便于携带也成为一个发展趋势。

本次设计利用单片机、FPGA和AD设计一款大众化的数字滤波器,成本低、体积小、便于携带、使用方便,能够完成基本的测试,如:存储并显示波形,测量信号的频率、幅度等。

1 方案论证与比较1.1 方案一:DSP+FPGA开发起来比较灵活,升级也较为容易,通用性较强。

同时利用了DSP运算速度来提高整个系统的算法效率;同时采用这种架构开发起来相对比较简单,因为它结合了FPGA 和DSP两者的优点。

所以它适合于实时信号处理。

在实时信号处理的过程中,对DSP的速度要求高,这样能同时使得整个系统既有其高速的处理速度,同时也不失其灵活性。

但是DSP在和与外围电路接口的时候,比如说LCD显示器和键盘电路进行通信的时候,因为DSP速度非常快。

而LCD和键盘的速度都很慢,DSP的优势没有得到利用。

1.2 方案二:利用超大规模可编程器件FPGA来控制高速A/D转换器和RAM实现高速数据采集,并且用它来进行数据的存储与处理。

由于超大规模可编程器件是全硬件的,所以速度快,稳定性好,利用较少的外围器件就可以实现复杂的逻辑和时序控制功能,是较为理想的方案。

这种方案实际上是一种片上系统(System On Chip),即用单个芯片完成所有的控制与数据处理,并且还是全硬件的。

但是该方案实现起来非常困难,并且成本非常高,所以没有采用这种方案。

1.3 方案三:该方案采用FPGA和MSP430单片机来实现。

关于FPGA多处理器的数字存储示波器研究1.引言随着电力电子和通信技术等行业的高速发展,示波器作为产品设计和调试中不可或缺的一个仪器得到了广泛的应用。

由于工程师对示波器的要求也越来越高,数字存储示波器以其强大的分析计算功能逐渐取代了模拟示波器。

实时采样率、实时带宽是衡量数字存储示波器的两个重要指标,然而工程师往往忽略了另一个重要指标——波形捕获率[1]。

波形捕获率是指示波器的采样时间占总测量时间的比例。

波形捕获率小就会漏掉许多待测波形,就很难观察到波形中的偶发事件。

波形捕获率取决于整个示波器的采样、处理、存储和显示模块的结构。

如图1,这是传统数字存储示波器的整体架构,待测信号经过放大器,由A/D 进行采样,采样的数据由处理器控制存入内存,处理器经过分析、计算参数等再将波形显示到显示器。

处理器在进行数据存储和处理的这段时间是不能进行采样的,那么这段时间就是所谓的“死区时间”,一般示波器的采样时间只占总测量时间的1%,因此大多数的信号信息丢失,这就大大降低了产品调试的效率[2]。

本文提出一种多处理器并行处理的数字存储示波器,有效的提高了整体的测量效率,不仅减少了“死区时间”,还提高了波形捕获率,对电路中的故障调试的速度也得到提高。

2.系统结构本文提出一种基于FPGA 的多处理器的数字存储示波器的架构,提高示波器的波形捕获率。

传统示波器之所以波形捕获率低下主要是因为单个处理器既要控制采集数据又要完成后期的处理和显示,这种串行结构导致浪费了很多的时间。

所以本文针对这种串行结构提出一种高效的并行处理结构的示波器,其基本结构所示。

处理器的数字存储示波器主要分为以下五个部分:信号调理及触发模块、并行波形采集模块、波形协处理模块、核心处理器及显示模块。

3.各模块设计3.1 乒乓采集模块本示波器的前端信号处理模块与传统示波器一样,使信号满足A/D 采样的要求。

传统示波器使用单个处理器对A/D 采样进行控制,这样当一次采样完成后就不能继续采样了,因为处理器要将采样存储器中的数据转移到内部存储器中进行处理。

第九届电子设计竞赛论文所在院系:电控学院题目:基于FPGA嵌入式的双通道数字存储示波器作者:朱俊兰方威夏俊伟指导老师:柴钰二○一一年五月基于FPGA嵌入式的双通道数字存储示波器摘要:本设计是以FPGA为核心,结合衰减电路、程控放大电路、ADC采样、整形测频电路以及VGA显示模块实现了双通道数字存储示波器的设计。

用户可以获取当前输入波形的峰峰值、频率等信息,另外用户可以对波形实现存储和回显功能。

双通道的设计使得用户可以同时观察和对比两路波形,设计时充分利用了FPGA的高速数据处理能力,嵌入了诸多IP 软核组成SOPC系统,尤其是NiosII软核的嵌入,使得在一块FPGA上完成了数据采集、存储、处理、显示等所有功能,使得系统更为简洁、稳定。

关键词:FPGA NiosII SOPC VGA ADS830E1、引言数字存储示波器(Digital Storage Oscilloscopes,简称DSO)是随着数字模拟电路技术和数字处理技术(尤其是微型计算机的发展)的发展而日益强大的一种具有存储波形功能的示波器。

和传统示波器相比,数字示波器具有体积轻巧功耗低、使用方便且波形可存储,对波形可以进行复杂数学分析等优点。

在诸多领域中,数字示波器已经完全取代模拟示波器,但是在国内,数字示波器的市场一直为外国厂商(安捷伦、泰克等)虽占据,而且价格不菲,这样,对于像我们学生这样的消费者根本无法支付,那么,本文就基于此,研究探讨了一种基于FPGA的DIY示波器的方案。

经过我们的不断测试,在低端场合,这样一款数字示波器完全合乎需求。

2、方案设计2.1总体方案描述系统的组成框图如图2.1所示,包括输入信号耦合选择、双路程控衰减放大、数据采集存储、数据处理、数据显示等部分。

信号分别从通道1、通道2输入,送入程控放大(衰减)电路进行放大(衰减),再对被放大(衰减)的信号进行电平调整后,送入高速ADC 对信号进行采样,FPGA则用于完成系统高速采样信号的存储及分频,并将波形显示在显示模块上。

基于FPGA的数字存储示波器设计耿新力;王中训【期刊名称】《电视技术》【年(卷),期】2013(37)9【摘要】An optimized method of data collection is proposed to complete the digital storage oscilloscope,which is supported by FPGA as its controller platform and the necessary peripheral circuits.The system uses FPGA high-speed digital signal processing and embedded of many modular circuits and soft-core characteristics,reducing the cost and difficulty of development.The combination of the basic principles of digital storage oscilloscope and signal source with new data acquisition and processing method and the optimization at analog signal preprocessing,data multi-faceted storage,trigger mode,and equal precision frequency measurement.After testing,the system has excellent performance,and all this provides new ideas for the development of new simple digital storage oscilloscope.%提出一个经过优化的数据采集方法,辅以FPGA(Field-Programmable Gate Array)主控制器和必备的外围电路完成了基于FPGA的数字存储示波器的设计.系统最大限度地利用了FPGA的高速数字信号处理能力以及众多硬核和软核内嵌的特性,降低了成本和开发难度.将数字存储示波器及信号源的基本原理和经过优化的数据采集方法相结合,分别在模拟信号预处理、数据多方位存储、触发方式、等精度测频等环节进行创新性优化,经测试,系统性能良好,各项指标均能较好满足要求,为新型简易数字存储示波器的发展提出了新思路.【总页数】4页(P218-221)【作者】耿新力;王中训【作者单位】烟台大学光电信息科学技术学院,山东烟台264005;烟台大学光电信息科学技术学院,山东烟台264005【正文语种】中文【中图分类】TN948【相关文献】1.基于FPGA和单片机的简易数字存储示波器设计 [J], 谭本军2.基于 FPGA 的数字存储示波器对外围芯片的控制设计 [J], 林盛鑫;钟惠球;黄丁香3.基于FPGA的虚拟简易数字存储示波器设计 [J], 雷贵;胡福云4.基于FPGA的手持式数字存储示波器显示驱动设计 [J], 石明江;张禾;河道清5.基于FPGA的数字存储示波器设计 [J], 苏建加;廖聪裕;鲁锦涛因版权原因,仅展示原文概要,查看原文内容请购买。

论文题目:基于FPGA的数字示波器1.摘要 (3)2.原理 (3)3.系统方案对比及分析 (4)3.1.以FPGA来实现整个系统 (4)3.2.采用DSP与FPGA来实现整个系统 (4)3.3.采用FPGA与单片机来实现整个系统 (4)4.系统设计方案 (4)5.系统框图 (5)6.系统技术指标 (6)7.AD模块简介 (6)8.频率测量模块及方案比较 (6)8.1.测周期法 (6)8.2.测频率法 (7)8.3.方法选择及使用 (7)8.4.Verilog设计结构 (8)9.数据处理模块 (9)10.FIFO存储模块 (9)10.1.FIFO_1 (9)10.2.FIFO_2 (9)11.Nios II软核模块 (10)12.VGA显示 (10)13.系统软件构架设计 (11)13. Nios II软件实现 (13)14.1.DMA传输 (13)14.2.1.PIO中断 (14)14.系统的测试和分析 (15)15.总结 (22)16.参考文献 (23)1.摘要随着信息技术的发展,对信号的测量技术要求越来越高,示波器的使用越来越广泛。

数字示波器是模拟示波器技术、数字化测量技术、计算机技术的综合产物,他主要以微处理器、数字存储器、A/D转换器和D/A转换器为核心,输入信号首先经A/D转换器转换成数字信号,然后存储在RAM中,需要时再将RAM中的内容读出,经D/A转换器恢复为模拟信号显示在示波器上,或者通过接口与计算机相连对存储的信号作进一步处理,这样可大大改进显示特性,增强功能,便于控制和智能化。

这种数字示波器中看到的波形是由采集到的数据经过重构后得到的波形,而不是加到输入端上信号的波形。

设计提出一个经过优化的数据采集方法,辅以FPGA为主控制器和必备的外围电路完成了基于FPGA的数字存储示波器的设计。

系统最大限度地利用了FPGA的高速数字信号处理能力以及众多硬核和软核内嵌的特性,降低了成本和开发难度,且性能优良。

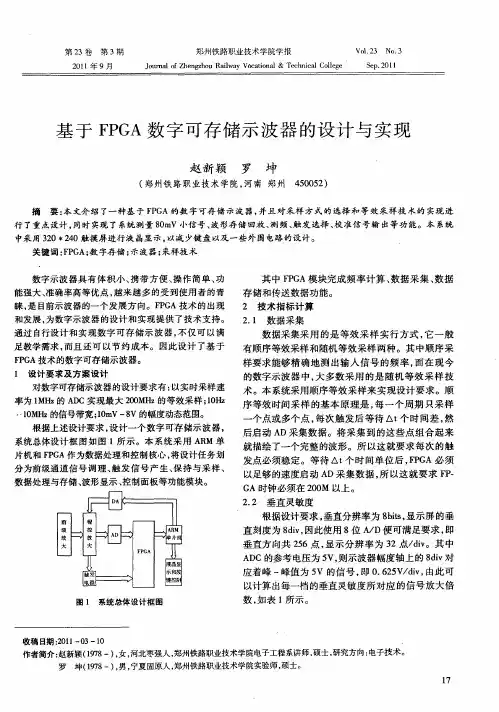

基于FPGA 的数字存储示波器周金刚1,左 超2,崔长生2(1.华中科技大学电气学院,湖北省武汉市430074;2.华中科技大学电子系,湖北省武汉市430074)摘 要:数字示波器由程控放大电路、采样保持电路、高速数据采集、示波显示调理4个模块组成。

系统以FPGA (现场可编程门阵列)为控制核心,FPGA 内嵌RAM 存储波形数据,终端采用X 、Y 轴方式显示,低频段实现了106次采样/s 实时采样,高频段实现了200MH z 等效采样,等效采样时钟由FPGA 内置锁相环时钟分频得到,分频算法经优化具有极高的精度,被测波形频谱覆盖了20H z~10MH z ,波形显示无明显失真。

关键词:数字存储示波器;FPGA;等效采样中图分类号:TM 935.32收稿日期:2007-10-08;修回日期:2007-11-30。

0 引 言按照对测量信号的处理方式,示波器可分为模拟式和数字式两种类型;按照示波器能够同时显示的信号的数目,示波器可分为单踪(通道)和双踪(通道)两种类型。

模拟和数字示波器各有不同的特点,原理相同。

数字示波器采用数字技术和计算机技术,功能强大,已经成为时域、频域、复频域的未知信号波形及参数测量的重要工具。

现在的数字示波器基本都具有了波形观察、数字测量、模拟测量、脉冲测试,双时基观测、只读测量与比较测量、自动测量等多种测量技术和方法。

1 总体方案比较与选择方案1:阶梯波比较触发。

根据被测信号频率产生M 分频锯齿波信号,用于同被测信号比较,产生脉冲序列,顺序提取部分脉冲作为信号采样保持以及A /D 转换时钟,达到对原始信号进行恢复的目的。

如图1所示,顺序产生步进延迟。

图1 阶梯波比较采样方案2:DDS(直接数字频率合成器)芯片高精度相位控制。

利用DDS 芯片AD9851高精度频率控制字,可产生频率不高、但步进延迟精度很高的采样信号。

设采样频率为f ou t =1/T +n t ,当所取T 值大于1 s 时,f ou t 便低于1MH z 。

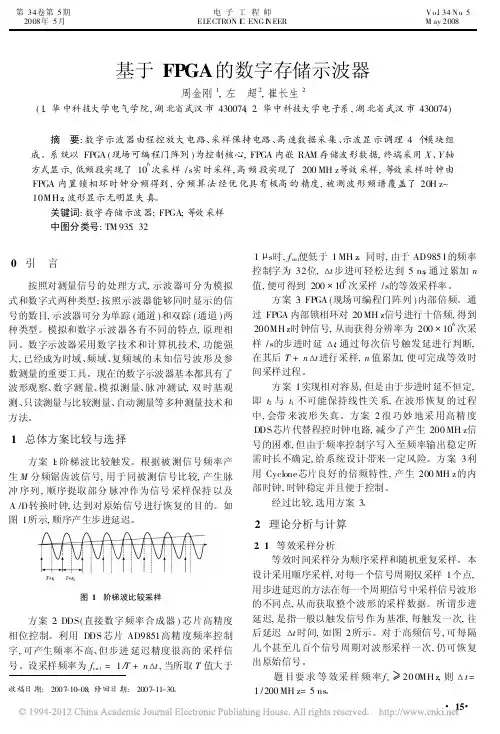

基于FPGA的双通道简易可存储示波器设计摘要:本文介绍了一种基于FPGA的采样速度60Mbit/s的双通道简易数字示波器设计,能够实现量程和采样频率的自动调整、数据缓存、显示以及与计算机之间的数据传输。

关键词:数据采集;数字示波器;FPGA引言传统的示波器虽然功能齐全,但是体积大、重量重、成本高、等一系列问题使应用受到了限制。

有鉴于此,便携式数字存储采集器就应运而生,它采用了LCD显示、高速A/D采集与转换、ASIC芯片等新技术,具有很强的实用性和巨大的市场潜力,也代表了当代电子测量仪器的一种发展趋势,即向功能多、体积小、重量轻、使用方便的掌上型仪器发展。

系统组成结构及工作原理系统的硬件部分为一块高速的数据采集电路板。

它能够实现双通道数据输入,每路采样频率可达到60Mbit/s。

从功能上可以将硬件系统分为:信号前端放大及调理模块、高速模数转换模块、FPGA逻辑控制模块、单片机控制模块、USB数据传输模块、液晶显示和键盘控制等几部分,其结构形式如图1所示。

图1系统原理结构图输入信号经前置放大及增益可调电路转换后,成为符合A/D转换器要求的输入电压,经A/D转换后的数字信号,由FPGA内的FIFO缓存,再经USB接口传输到计算机中,供后续数据处理,或直接由单片机控制将采集到的信号显示在液晶屏幕上。

高速数据采集模块本系统可实现双通道同步数据采集,而且每通道的采集速度要达到60Mbit/s,考虑到两路数据采集应保持同步并行,因此在设计中采用每通道都有独自的采样保持器和A/D转换器。

选用MAXIM公司MAX1197型A/D转换器,它是一款双通道、3.3V 供电、每通道60Mbit/s采样频率的模数转换器芯片。

它内部集成双路差分宽带采样保持器和A/D转换器,可以输出锁存,具有低功耗、小尺寸、高动态性能的特点。

本系统的测量电压的范围可达到±300V,采用示波器探头和电路板上分压的方法将输入信号先进行1:1或10:1或100:1衰减,然后再通过后续电路处理以满足A/D 转换器的输入电压范围要求。

可编程逻辑器件(FPGA)在集成电路中的应用可编程逻辑器件(FPGA)是一种集成电路(IC)的设计工具,具有可重构和可编程的特性。

它可以在硬件级别上重新配置其内部逻辑功能,使其能够执行特定任务。

FPGA在集成电路设计和应用中扮演着重要的角色,广泛应用于各个领域。

一、FPGA的基本结构与工作原理FPGA由大量的逻辑门、寄存器、RAM和其他数字电路组成。

其核心部分是可编程逻辑单元(PLU),它由可编程逻辑阵列(CLA)组成,每个逻辑单元都包含一个查找表(LUT),用于实现逻辑功能。

通过配置寄存器和LU以及将内部信号路由到特定的输入/输出引脚,可以将FPGA定制为特定的电路。

FPGA利用静态随机存取存储器(SRAM)来保存逻辑配置信息。

在每次启动时,FPGA首先将配置信息从外部存储器加载到内部SRAM中,然后根据配置信息将内部逻辑电路重新组织和重连。

该重组过程称为配置。

一旦FPGA被配置完成,它就开始执行特定的任务。

二、FPGA的应用领域1. 数字信号处理(DSP):FPGA在DSP领域中的应用十分广泛。

它可以执行数字滤波、图像处理、高速数据转换和算法加速等任务。

由于其可以快速重配置的特性,FPGA在需要快速响应和高度并行处理的应用中具有很大的优势。

2. 通信与网络:FPGA在通信与网络领域中有着重要的作用。

它可以实现各种通信协议的编解码、信号调制与解调、协议转换以及高速数据处理等功能。

在网络设备中,FPGA通常被用于数据包处理、流量控制和数据路由等任务。

3. 图像与视频处理:FPGA在图像与视频处理中也发挥着重要的作用。

它可以实现图像和视频的实时处理、编解码、图像增强、视频合成和视频传输等功能。

在高清视频和虚拟现实应用中,FPGA被广泛应用于图像和视频数据的高效处理。

4. 工业控制与自动化:FPGA在工业控制与自动化领域中的应用十分广泛。

它可以实现实时数据采集、传感器信号处理、运动控制和逻辑控制等任务。

基于FPGA的数字存储示波器的设计的开题报告一、选题背景随着科技的不断进步和发展,数字化技术已成为当今各个领域的主流趋势,数字存储示波器便是其中之一。

数字存储示波器的优点在于数字化处理数据,能够有效地处理和分析信号,同时具有高速、高精度、高灵敏度等优点,因此被广泛用于电子工程、通信工程、机械工程等领域。

而基于FPGA的数字存储示波器则是电子工程领域内的一项重要技术,在满足科技迅速发展的同时,有着快速响应时间、高速数据处理等优点。

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有灵活的可编程性和快速的实时数据处理能力,被广泛应用于数字系统中。

基于FPGA的数字存储示波器则是将数字存储示波器技术与FPGA技术相结合,使得数字存储示波器具有更高的性能和功能。

二、研究目的本次课题旨在研究设计一种基于FPGA的数字存储示波器,并实现以下功能:1. 采样率高:采用高速ADC转换器,并使用FPGA进行数字信号处理,实现高速的采样和存储。

2. 示波器屏幕显示:采用液晶显示屏或者其他显示屏,显示采集到的波形数据。

3. 波形记录和回放功能:实现对采集的波形数据的记录和回放,方便工程师进行数据分析和处理。

三、研究内容1. FPGA开发环境的搭建:使用Vivado或Quartus等软件工具,完成FPGA开发环境的搭建。

2. 高速ADC转换器的选择和接口设计:选择合适的高速ADC转换器,并设计其与FPGA的接口电路。

3. 数据存储与处理的实现:使用FPGA对采集的数据进行存储和处理,实现数字存储示波器的基本功能。

4. 示波器屏幕的显示:设计示波器屏幕的驱动电路,并实现波形数据的实时显示。

5. 波形记录和回放功能的实现:对采集到的波形数据进行存储和压缩,实现波形记录和回放功能。

四、技术路线技术路线如下:1. 硬件方面:采购合适的高速ADC转换器,设计合适的FPGA接口电路,并选择合适的显示屏或者液晶显示屏。

毕业设计(毕业论文)系别:电子与电气工程学院专业:电子信息工程技术班级:学生姓名:学生学号:设计(论文)题目:基于FPGA技术的数字存储示波器设计指导教师:设计地点:起迄日期:毕业设计(论文)任务书专业电子信息班级姓名一、课题名称:基于FPGA技术的数字存储示波器设计二、主要技术指标:(1)带宽:100MHz (2)垂直灵敏度:10mv—5v/div (3)水平灵敏度:2.5ns—5s/div (4)输入阻抗:1MΩ(5)存储深度:4KB (6)显示:LED(7)通道:单通道等三、工作内容和要求:本设计的数据采集采用高速模/数转换器ADl674(A/D),直接用FPGA准确定时控制ADC的采样速率,实现整个频段的全速采样。

数据的存储采用双口RAM(UT62-256)存储采样量化后的波形数据,同样用FPGA控制RAM的地址线。

整个系统采用单通道的方式,信号进来首先经过前端的调理电路把信号电压调整到AD的输入电压范围之内,这里调节电路主要是由信号衰减电路和信号放大电路所组成。

调节后的信号再送到AD变换电路里面完成信号的数字化。

然后把AD转换后的数据送到FPGA中,并把数据保存到FPGA中的FIFO中,FPGA中的电路主要包括有FIFO、触发系统、峰值检测、时基电路等。

四、主要参考文献:[1]杨刚、龙海燕.现代电子技术一VHDL与数字系统设计[M].北京:电子工业出版社.2004.[2]侯伯亨、顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:两安电子科技人学.1999.[3]潘松下、国栋帅.L实用教程[M].成都:成都电子科技大学出版社.2000.[4]潘松下、黄继业.EDA技术实用教程[M]北京:科学出版社.2002.[5]王振红.VHDL数字电路设计与应用实践教程[M].北京机械工业出版社.2003.学生(签名)2010年5月7日指导教师(签名)2010年5月10日教研室主任(签名)2010年5月10日系主任(签名)2010年5月12日毕业设计(论文)开题报告目录摘要Abstract第1章前言 (1)1.1 数字存储示波器的发展概况 (1)1.2 本文所做的研究工作 (1)第2章示波器的工作原理 (3)2.1 模拟示波器的基本工作原理 (3)2.2 数字存储示波器的工作原理 (4)第3章 D S P处理器和F P G A的开发过程简介 (5)3.1 DSP处理器的开发过程和应用 (5)3.2 FPGA的开发过程与应用 (6)第4章整体设计方案 (8)4.1 系统整体设计流程图 (8)4.2 整个系统的性能指标 (9)4.3 系统的实现方案 (9)4.4 元器件的选择 (11)第5章整个系统硬件设计 (12)5.1 前端数据采集部分硬件电路设计 (12)5.2 FPGA外围电路的设计和内部逻辑电路设计 (17)5.3 DSP部分的硬件设计 (24)第6章系统软件设计 (29)6.1系统初始化 (29)6.2数据处理的相关算法 (33)6.3波形显示程序 (35)第7章结束语 (37)答谢辞参考文献摘要数字存储示波器在仪器仪表领域中占有重要的地位,应用范围相当广泛,所以对示波器的研制有重要的理论和实际意义。

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种灵活的、可编程的数字集成电路技术,它在数字专用集成电路(ASIC)设计中扮演着非常重要的角色。

本文将介绍FPGA在ASIC设计中的应用,并探讨其优势和挑战。

一、FPGA的原理和特点FPGA是一种可编程逻辑器件,其内部由大量的可编程逻辑单元和存储单元组成。

通过编程工具(如Verilog或VHDL),用户可以灵活地定义FPGA的逻辑功能和内部连接,从而实现各种数字电路的设计。

与ASIC相比,FPGA具有灵活性高、设计周期短和适应性强的特点,这使得它在数字电路设计领域得到了广泛应用。

二、FPGA在数字专用集成电路设计中的应用1. 逻辑设计FPGA可以被用来实现各种逻辑功能,如门电路、触发器、计数器等。

通过编程工具,工程师可以轻松地定义这些逻辑功能,并在FPGA内部实现它们。

这种灵活性使得FPGA成为逻辑设计的理想选择。

2. 信号处理FPGA在数字信号处理(DSP)领域有着广泛的应用。

通过设计适当的算法和逻辑电路,FPGA可以实现各种信号处理功能,如滤波、变换、解调等。

这使得FPGA在通信系统、雷达系统等领域发挥着重要作用。

3. 接口控制FPGA可以被用来实现各种接口控制功能,如UART、SPI、I2C等。

通过定义适当的协议和接口电路,FPGA可以实现与外部设备的通信和控制功能。

这为各种嵌入式系统的设计提供了便利。

4. 硬件加速FPGA可以被用来实现各种硬件加速功能,如密码学加速、图像处理加速等。

通过设计专门的硬件电路,FPGA可以显著提高这些功能的运算速度和效率。

5. 系统集成FPGA还可以被用来实现系统集成功能,如中央控制器、数据总线、内存控制等。

通过设计适当的系统架构和逻辑电路,FPGA可以实现各种系统集成功能,从而简化整个系统的设计和布局。

三、FPGA在ASIC设计中的优势1. 灵活性高FPGA具有很高的灵活性,可以根据实际需求动态调整其逻辑功能和内部连接。