专业实验类:伪随机信号发生器

- 格式:pdf

- 大小:250.57 KB

- 文档页数:5

伪随机码发生器的研究与设计Pseudo-random code generator Research and Design摘要伪随机序列产生技术是集数学、计算机科学、电子与通信等诸多学科于一身的技术,其产生技术自上世纪末至今一直是国内外的研究热点并取得了不少的成果。

伪随机码越来越受到人们的重视,被广泛应用于导弹、卫星、飞船轨道测量和跟踪、雷达、导航、移动通信、保密通信和通信系统性能的测量以及数字信息处理系统中。

目前国内外均有项目研究提高伪随机序列发生器可靠性、状态利用率等问题。

本课题介绍了伪随机码的应用和研究概况,研究了伪随机码的产生方式和产生原理,并以此为基础阐述了一种基于移位寄存器的m序列伪随机码发生器的设计与实现的方法。

最终在使用集成电路的前提下,先分析由移位寄存器电路构成的伪随机序列发生器的设计方法,分步设计了移位寄存器电路和同步复位信号发生电路;再通过一系列的误差和可靠性调整设计,最终用小规模集成电路和外加时钟信号设计实现了线性反馈移位寄存器产生周期P=15的m序列,并且给出了完整的实现电路和时序分析结果。

关键词:伪随机码,绕码,m序列,移位寄存器ABSTRACTPseudo-random sequence generation technique is a mathematics, computer science, electronics and communication, and many other subjects in one of the technology, its production technology since the end of the century has been the research focus at home and abroad and made a lot of results.Pseudo-random code more and more attention, is widely used in missiles, satellites, spacecraft orbit measurement and tracking, radar, navigation, mobile communications, secure communications and communication system performance measurement and digital information processing system. Research projects at home and abroad are pseudo-random sequence generator to improve reliability, availability status and other issues.This topic describes the application of pseudo-random code and research overview of the pseudo-random code generation means and generating principle, and described as the basis for an m-sequence shift register based pseudo-random code generator of the design and implementation Approach. Final premise in the use of integrated circuits, the first shift register circuits of the pseudo-random sequence generator design, step by step design of the shift register circuit and the synchronous reset signal circuit; then through a series of errors and reliable Adjustment design, end-users and small-scale integrated circuit design of the clock signal applied to achieve a linear feedback shift register generating cycle P = 15 m-sequence and provides a complete implementation of the circuit and timing analysis. Key words:Pseudo-random code,Around the code, m sequence,Shift register目录摘要 (Ⅰ)ABSTRACT (Ⅱ)目录 (Ⅲ)1 绪论 (1)1.1 伪随机序列的研究概况 (1)1.2 伪随机序列的应用领域及其意义 (1)1.3 课题研究内容与难点 (2)2 伪随机序列发生器 (3)2.1 伪随机序列的定义及其特点 (3)2.2 伪随机序列的产生 (3)2.3 伪随机序列反馈函数 (4)3伪随机码发生器电路设计 (7)3.1 移位寄存器电路设计 (7)3.2置数功能电路设计 (7)3.3可靠性附加电路设计 (8)3.4元器件选型 (10)3.5整体电路图 (10)4电路时序分析 (12)4.1移位寄存器电路时序分析 (12)4.2完整电路时序分析 (12)结束语 (14)参考文献 (15)附录芯片逻辑引脚图及各型号性能对比 (16)致谢 (17)1 绪论1.1 伪随机码的研究概况伪随机码又称伪随机序列或伪噪声序列。

实验八伪随机码产生器实验一、实验实训目的1.了解扩频通信的原理2.掌握伪随机序列——m序列产生器的结构二、实验原理与说明信号的频带宽度与其脉冲宽度近似成反比。

很窄的脉冲序列的带宽很宽,因此如果用很窄的脉冲序列对所传信息进行调制,则可产生很宽频带的信号。

CDMA 蜂窝网移动通信系统就是采用这种方式获得扩频信号的。

所用的这种很窄的脉冲码序列称为扩频码序列。

用很窄的脉冲序列对所传信息进行调制的一种方式就是直接序列扩频。

直接序列扩频系统采用的很窄的脉冲序列——伪随机码在发端对要发送的信息码进行频谱展宽——扩频,在收端用相同的伪随机码序列进行解扩,然后将展宽的扩频信号还原成原始信息。

作为扩频码的伪随机码具有类似白噪声的特性,可以用一种周期性的脉冲信号来近似随机噪声的性能,称之为伪随机码或PN码。

用于扩频码的伪随机码常用的m序列。

m序列容易产生、规律性强等优良特性,目前的CDMA系统就是采用这种PN 序列---m序列来进行扩频通信的。

m序列是最长线性移位寄存器的简称,m序列具有与伪随机噪声类似的尖锐自相关特性,但它不是真正随机的,而是按照一定规律周期性变化,它的周期P=2n-1。

n称之为m序列的阶数,也是构成m序列产程器所用移位寄存器的级数。

可以用硬件电路来实现一个m序列。

以最简单的n=3的三级移位寄存器构成的m序列发生器如图1所示。

移位寄存器是D触发器(如74163),在时钟脉冲CP上升沿到来时,输出Q等于输入D。

中间第二、三级移位寄存器的输出Q2和Q3经模2加(异或)电路后反馈到第一级移位寄存器的输入D1端,构成反馈电路。

当初始状态Q1Q2Q3为111时,在时钟脉冲的控制下,各输出端的输出数据如表1所示,得到输出周期为P=23-1=7的码序列1110010。

在输出一个周期的序列后,Q1Q2Q3又回到111状态。

在时钟的控制下,输出序列做周期性的重复。

1110010就是一个周期是7的m序列。

产生周期为P=2n-1的m序列的方法类似。

成都电子机械高等专科学校毕业设计论文作者姚世刚学号2009111733系部电子与电气工程系专业电子测量技术与仪器题目基于VHDL的m序列伪随机信号发生器的设计指导教师赵茂林评阅教师完成时间:2012年4 月30日毕业设计(论文)中文摘要题目:基于VHDL的m序列发生器的设计摘要:VHDL/CPLD即复杂可编程逻辑器件作为一种大规模集成电路,可根据用户的需要自行构造逻辑功能,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产之中。

几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。

本文介绍了基于CPLD的m序列发生器的设计方法。

关键词:CPLD;MAX+PLUS II;伪随机码;m序列发生器毕业设计(论文)外文摘要Title : M—sequence Generator Based CPLDAbstract: VHDL/CPLD Complex Programmable Logic Device that is, as a large scale integrated circuits can be constructed according to the needs of users on their own logic, enabling large-scale circuit design, it is widely used in product design and prototype production into. Almost all applications of small and medium general-purpose digital integrated circuits may be applied CPLD devices occasions. This article describes the m-sequence generator based on CPLD design method.Key words: CPLD;MAX+PLUS II;Pseudorandom Code;m sequence code Generator目录前言 (6)1课题介绍 (7)1.1为什么研究此课题 (7)1.2伪随机序列的应用与意义 (7)1.3伪随机序列的研究现状 (8)1.4研究内容 (8)2设计中使用芯片及VHDL语言介绍 (9)2.1 CPLD芯片介绍 (9)2.1.1概述 (9)2.1.2 MAX7000特点 (9)2.1.3 EPM7128LC84-7 (11)3 伪随机序列介绍 (12)3.1 伪随机序列理论的发展史 (13)3.2 伪随机序列的构造方法 (13)4 序列信号发生器原理 (14)4.1序列信号发生器的设计 (15)4.1.1反馈移位型序列信号发生器 (15)4.1.2计数型序列码发生器 (18)5 移位寄存器 (20)5.1移位寄存器 (20)5.1.1 寄存器 (20)5.1.2移位寄存器 (21)5.2 线性反馈移位寄存器结构 (22)5.2.1 D触发器 (22)5.2.1.1 D触发器工作原理 (22)5.2.1.2 D触发器真值表 (23)5.2.1.3 特征方程 (23)5.2.1.4 状态转移图 (23)5.2.1.5时序图 (24)5.2.1.6 脉冲特性 (24)5.2.2异或门 (25)5.2.2.1 基本原理 (25)5.2.2.2 异或门逻辑符号 (25)5.2.2.3 逻辑表达式 (25)5.2.2.4 真值表 (25)5.3 线性反馈移位寄存器 (26)5.3.1 什么是反馈移位寄存器 (26)5.3.2 线性反馈移位寄存器 (26)5.3.3 性质 (26)6 伪随机信号 (27)6.1 伪随机信号 (27)6.2 m序列码发生器 (30)7 m序列性质 (33)7.1 均衡性 (33)7.2游程特性 (33)7.3 移位相加性 (33)7.4 相关特性 (33)7.5 伪随机特性 (34)8 序列信号发生器的设计和仿真实现 (35)8.1 m序列生成单元的电路设计 (35)8.1.1 系统组成 (35)8.1.2 程序方框图 (36)8.2 m序列发生器 (36)8.3 VHDL语言实现 (37)8.4 仿真数据及结论 (39)结论 (42)致谢 (43)参考文献 (43)前言CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

伪随机序列发生器一、实验目的:理解伪随机序列发生器的工作原理以及实现方法,掌握MATLAB\DSP BUILDER设计的基本步骤和方法。

二、实验条件:1. 安装WindowsXP系统的PC机;2. 安装QuartusII6.0 EDA软件;的序列发生器,并通⒈ ⒉ ⒊⒋⒌⒍⒎⒏⒐ ⒑ ⒒⒓⒔⒕⒖⒗四、实验原理:对于数字信号传输系统,传送的数字基带信号(一般是一个数字序列),由于载有信息,在时间上往往是不平均的(比如数字化的语音信号),对应的数字序列编码的特性,不利于数字信号的传输。

对此,可以通过对数字基带信号预先进行“随机化”(加扰)处理,使得信号频谱在通带内平均化,改善数字信号的传输;然后在接受端进行解扰操作,恢复到原来的信号。

伪随机序列广泛应用与这类加扰与解扰操作中。

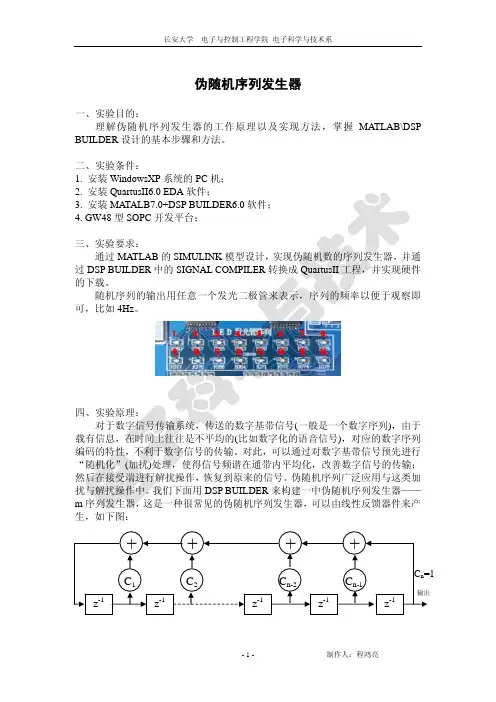

我们下面用DSP BUILDER来构建一中伪随机序列发生器——m序列发生器,这是一种很常见的伪随机序列发生器,可以由线性反馈器件来产生,如下图:其特征多项式为:()∑==ni i i x C x F 0注:其中的乘法和加法运算都是模二运算,即逻辑与和逻辑或。

可以证明,对于一个n 次多项式,与其对应的随机序列的周期为。

12−n 接下来我们以为例,利用DSP BUILDER 构建这样一个伪随机序列发生器。

125++x x开Simulink 浏览器。

Simulink我们可以看到在Simulink 工作库中所安装的Altera DSP Builder 库。

2. 点击Simulink 的菜单File\New\Model 菜单项,新建一个空的模型文件。

3. 按照下图在Model编辑器的工作区中放置如下的模型:其中Logical Bit Operator模块在Gate & Control库中,把它拖到工作区中后双击打开参数设置对话框,设置成2输入异或门。

为了能够在Matlab中获得仿真结果,可以给输出再添加一个示波器Scope,这个模型在Simulink标准库的Sources库中。

信号发生器实验报告信号发生器实验报告引言信号发生器是电子实验室中常见的一种仪器,用于产生各种类型的电信号。

本次实验旨在探究信号发生器的原理和应用,以及对其进行一系列的测试和测量。

一、信号发生器的原理信号发生器是一种能够产生不同频率、幅度和波形的电信号的设备。

其主要由振荡电路、放大电路和输出电路组成。

振荡电路负责产生稳定的基准信号,放大电路将基准信号放大到合适的幅度,输出电路将信号输出到外部设备。

二、信号发生器的应用1. 电子器件测试:信号发生器可以用于测试电子器件的频率响应、幅度响应等特性。

通过改变信号发生器的频率和幅度,可以模拟不同工作条件下的电子器件性能。

2. 通信系统调试:在通信系统的调试过程中,信号发生器可以用于模拟各种信号,如语音信号、数据信号等。

通过调整信号发生器的参数,可以测试通信系统的传输质量和容量。

3. 音频设备测试:信号发生器可以用于测试音频设备的频率响应、失真等特性。

通过产生不同频率和幅度的信号,可以对音频设备进行全面的测试和评估。

三、实验过程1. 测试频率响应:将信号发生器连接到待测设备的输入端,逐渐改变信号发生器的频率,并记录待测设备的输出结果。

通过绘制频率响应曲线,可以了解待测设备在不同频率下的响应情况。

2. 测试幅度响应:将信号发生器连接到待测设备的输入端,逐渐改变信号发生器的输出幅度,并记录待测设备的输出结果。

通过绘制幅度响应曲线,可以了解待测设备对不同幅度信号的响应情况。

3. 测试波形输出:将信号发生器连接到示波器,通过改变信号发生器的波形设置,观察示波器上的波形变化。

通过比较不同波形的特征,可以了解信号发生器的波形生成能力。

四、实验结果与分析1. 频率响应:根据实验数据绘制的频率响应曲线显示,待测设备在低频段具有较好的响应能力,而在高频段则逐渐衰减。

这可能是由于待测设备的电路结构和元件特性导致的。

2. 幅度响应:根据实验数据绘制的幅度响应曲线显示,待测设备对于低幅度信号的响应较差,而对于高幅度信号的响应较好。

实验一 伪随机码发生器实验一、实验目的1、 掌握伪随机码的特性。

2、 掌握不同周期伪随机码设计。

3、 用基本元件库和74LS系列元件库设计伪随机码。

4、 了解ALTERA公司大规模可编程逻辑器件EPM7128SLC84内部结构和应用。

5、 学习FPGA开发软件MAXPLUSⅡ,学习开发系统软件中的各种元件库应用。

6、 熟悉通信原理实验板的结构。

二、实验仪器1、 计算机 一台2、 通信基础实验箱 一台3、 100MHz 示波器 一台三、实验原理伪随机码是数字通信中重要信码之一,常作为数字通信中的基带信号源;扰码;误码测试;扩频通信;保密通信等领域。

伪随机码的特性包括四个方面:1、 由n 级移位寄存器产生的伪随机序列,其周期为-1; n 22、 信码中“0”、“1” 出现次数大致相等,“1”码只比“0”码多一个;3、 在周期内共有-1游程,长度为 i 的游程出现次数比长度为 i+1的 游程出现次数多一倍;n 24、 具有类似白噪声的自相关函数,其自相关函数为:()()⎩⎨⎧−≤≤=−−=221012/11n nτττρ其中n 是伪随机序列的寄存器级数。

例如:四级伪码产生的本原多项式为X 4+X 3+1。

利用这个本原多项式构成的4级伪随机序列发生器产生的序列为:1 1 1 1 0 0 0 1 0 0 1 1 0 1 0相应的波形图如图1-1所示:图1-1 四级伪随机序列波形图用4个D 触发器和一个异或门构成的伪码发生器具有以下特性: 1、 周期为24-1=15;2、 在周期内“0”出现24 -1-1=7次,“1”出现24 -1=8次;3、 周期内共有24 -1 =8个游程;4、 具有双值自相关特性,其自相关系数为:⎩⎨⎧−≤≤−−==221)12(10144τ / τ ρ(τ)四、实验内容及步骤1、在MAXPLUSⅡ设计平台下进行电路设计 1.1 四级伪随机码发生器电路设计电路原理图如图1-2所示。

图1-2 四级伪随机码电路原理图在MAXPLUS II 环境下输入上述电路,其中: dff ------ 单D触发器 xor ------ 二输入异或门 nor4 ------ 四输入或非门 not ------ 反相器clk ------ 时钟输入引脚(16M时钟输入) 8M ------ 二分频输出测试点引脚 nrz ------ 伪随机码输出引脚 1.2 实验电路编译及FPGA 引脚定义完成原理图输入后按以下步骤进行编译:(1) 在Assign Device 菜单选择器件MAX7128SLC84。

一、实训目的本次实训旨在通过使用仿真软件Proteus和Keil uVision,学习并掌握信号发生器的设计与仿真方法,加深对信号发生器原理和电路设计的理解,提高实际操作能力。

二、实训内容1. 信号发生器原理信号发生器是一种产生各种标准信号的设备,广泛应用于通信、测量、科研等领域。

本次实训主要设计以下四种波形发生器:正弦波、方波、三角波和锯齿波。

2. 信号发生器电路设计(1)正弦波发生器:采用STM32F103单片机作为核心控制单元,通过查找正弦波查表法生成正弦波数据,经DAC0832数模转换芯片转换为模拟信号输出。

(2)方波发生器:利用STM32F103单片机的定时器产生方波信号,通过改变定时器的计数值来调整方波频率。

(3)三角波发生器:通过STM32F103单片机的定时器产生方波信号,再经过积分电路转换为三角波信号。

(4)锯齿波发生器:利用STM32F103单片机的定时器产生方波信号,再经过微分电路转换为锯齿波信号。

3. 信号发生器仿真(1)使用Proteus软件搭建信号发生器电路,并进行仿真测试。

(2)通过调整电路参数,观察输出波形的变化,验证电路设计的正确性。

(3)将仿真结果与理论分析进行对比,分析仿真结果与理论分析的一致性。

三、实训步骤1. 设计信号发生器电路原理图根据信号发生器原理,设计电路原理图,包括单片机、DAC0832数模转换芯片、矩阵键盘、LCD12864液晶屏幕等元件。

2. 编写程序使用C语言编写信号发生器程序,包括初始化配置、按键扫描、波形生成、LCD显示等功能。

3. 仿真测试(1)在Proteus软件中搭建电路,将程序编译生成的hex文件烧录到STM32F103单片机中。

(2)运行仿真,观察输出波形,验证电路设计及程序的正确性。

(3)根据仿真结果,调整电路参数,优化波形输出。

四、实训结果与分析1. 仿真结果通过仿真测试,成功实现了正弦波、方波、三角波和锯齿波的产生,波形输出稳定,符合设计要求。

伪随机广域电磁法自动采集系统关键技术在科技领域,创新如同璀璨的星辰,点亮了人类探索未知的夜空。

其中,伪随机广域电磁法自动采集系统的出现,无疑是这片星空中最耀眼的一颗新星。

这项技术,宛如一位精通自然语言的诗人,用电流和磁场的诗句,吟唱出地球深处的秘密。

首先,让我们来探讨这项技术的“心脏”——伪随机信号发生器。

它就像是一位指挥家,挥舞着手中的指挥棒,精确地控制着电磁波的频率和强度。

这种精确的控制,使得我们能够像透视眼一样,穿透地层,捕捉到地下的构造信息。

这就像是在一片混沌中找到了秩序,为我们提供了一种全新的视角来观察地球。

然而,仅仅有了“心脏”还不够,我们还需要一套高效的数据解释系统。

这个系统就像是一台超级计算机,能够快速处理大量的数据,并从中提取出有价值的信息。

它运用先进的数学模型和算法,将原始数据转化为直观的图像和报告。

这一过程就像是从一堆杂乱无章的线索中,找到了通往宝藏的地图。

接下来,我们不得不提的是这项技术的应用领域。

它广泛应用于矿产资源勘查、地下水调查、地质工程等多个领域。

在这些领域中,它就像是一把锋利的剑,为我们开辟了前进的道路。

特别是在矿产资源勘查方面,这项技术就像是一盏明灯,照亮了隐藏在地下的宝藏。

然而,任何一项技术都不可能完美无缺。

伪随机广域电磁法自动采集系统虽然具有诸多优点,但也存在一些挑战和问题。

例如,如何进一步提高数据解释的准确性和效率?如何降低系统的成本和复杂性?这些问题就像是一道道难题,等待着我们去解答。

面对这些挑战,我们不能退缩。

相反,我们应该迎难而上,继续推动这项技术的发展。

我们需要更多的研究和创新,需要更多的合作和交流。

只有这样,我们才能克服这些挑战,让这项技术更好地服务于人类社会。

最后,我想说,伪随机广域电磁法自动采集系统的出现,就像是一场科技革命。

它改变了我们对地球的认知方式,为我们提供了一种新的工具来探索未知的世界。

让我们一起期待这项技术的未来吧!。

伪随机码发生器研究与设计伪随机码发生器是一种通过其中一种算法生成伪随机序列的电子设备或程序。

与真随机数发生器不同,伪随机码发生器是基于确定性算法生成的序列,其看似是随机的,但实际上可以通过逆向计算或算法分析来预测出后续的码值。

1.算法选择:伪随机码发生器的性能很大程度上取决于所选择的算法。

常用的算法包括线性反馈移位寄存器(LFSR)、离散余弦变换(DCT)、线性同余发生器(LCG)等。

研究者可以根据特定需求选择合适的算法,并通过数学分析、理论推导和模拟实验来评估其性能。

2.随机性测试:伪随机码发生器生成的序列是否具备足够的随机性是一个关键问题。

为了评估伪随机码发生器的性能,需要设计合适的随机性测试方法。

常用的测试方法包括统计分析、频谱分析、序列均匀性检测、序列独立性检验等。

3.秘密性与安全性:在密码学应用中,伪随机码发生器的秘密性和安全性是非常重要的。

秘密性指发生器的设计和参数应保密,只有掌握这些信息的人才能伪装成合法用户。

安全性指发生器生成的序列在密码攻击下能够抵抗各种攻击手段。

确保秘密性和安全性需要对伪随机码发生器进行全面的安全性分析和风险评估,以便发现可能存在的漏洞和弱点,并采取相应的安全措施和改进措施。

4.性能优化:伪随机码发生器的性能包括生成速度、存储空间和计算复杂度等方面。

研究者需要在保证安全性的前提下,尽可能提高伪随机码发生器的性能。

这包括改进算法、优化参数选择、使用硬件加速等。

总结起来,伪随机码发生器的研究与设计需要深入理解随机性、密码学和计算机科学等领域的知识,并结合具体应用需求来选择合适的算法和进行性能优化。

通过合理的算法设计、随机性测试和安全性分析评估,以及针对性的安全措施和改进措施,可以设计出安全可靠的伪随机码发生器。

![2N次方广谱伪随机信号发生器及VHDL程序[1]](https://uimg.taocdn.com/9c3811d426fff705cc170a1a.webp)

目录第一章前言 (1)第二章伪随机信号 (2)2.1 2n伪随机信号简介 (2)第三章伪随机信号的时域分析 (3)第四章伪随机信号发生器的VHDL描述 (8)4.1 用VHDL设计产生双频波 (9)4.2用VHDL设计产生三频波 (9)4.3 主要构思及设计图 (10)4.4 各种波的程序及波形 (14)第五章结论 (30)参考文献 (31)致谢 (32)第一章前言伪随机信号处理最早是从空间工程和军事等应用中发展起来的,至今已有40多年的历史。

在这些应用中,重点主要集中在寻求某种信号格式以及信号处理技术,以保证信息的完整性,尤其在受到干扰攻击的时候更是如此。

随着数字移动通信系统的发展、对定位系统需求的持续增长以及集成电路集成度的日益提高,伪随机信号处理作为一种可行的技术在民用和商用系统中得到越来越多的应用。

伪随机序列通过设置数学乱源产生,它的伪随机性表现在预先的可确定性、可重复产生与处理,伪随机序列虽然不是真正的随机序列,但是当伪随机序列周期足够长时,伪随机序列具有随机序列的良好统计特性。

伪随机序列广泛应用于密码学、扩频通讯、导航、集成电路的可测性设计等许多重要领域[3]。

比如,密码学中伪随机序列通常被作为密钥,流密码中通过密钥流生成器产生性能优良的密钥流序列,使用该序列加密信息流得到密文序列,所以流密码的安全强度完全决定于密钥流序列的好坏。

扩频通信中伪随机序列作为扩频码,利用伪随机序列码把基带信号的频谱进行扩展,形成相当带宽的低功率谱密度信号进行发射。

使用不同的伪随机序列编码,不同通信用户可以在同一频段、同一时间工作,互不影响或影响极小。

具有良好的伪随机特性的扩频编码对扩频通信及其技术的应用是非常重要的。

基于伪随机序列具有的科学和社会价值, 对伪随机序列已经有了比较深入的研究。

伪随机序列信号在雷达、遥控、遥测、通信加密和无线电测量系统领域有着广泛的应用。

第二章伪随机信号简介2n系列伪随机信号为中国工程院院士何继善发明和命名(He,jishan,1997,何继善,1998)。

第22卷第3期 吉林大学学报(信息科学版) V o l122 N o13 2004年5月 Journal of J ilin U n iversity(Info r m ati on Science Editi on) M ay2004 文章编号:167125896(2004)0320185204伪随机序列发生器的研究与实现α孙淑琴1,林 君1,张秉仁2,罗 军2(11吉林大学地球信息探测仪器教育部重点实验室,吉林长春130026;21吉林大学电子科学与工程学院,吉林长春130026)摘要:研究了伪随机序列的随机特征,推导出M序列具备伪随机序列的特征,给出M序列的反馈逻辑函数,设计了M序列发生器;分析了测试电路产生的n阶伪随机序列的波形图。

通过对测试结果的分析、比较发现,关于反馈移位寄存器的阶数与序列长度关系、码元的游程(该序列的伪随机性)等方面的分析是正确的,验证了该设计的可行性。

关键词:伪随机序列;反馈逻辑函数;频率域中图分类号:TN79 文献标识码:AInvestigati on and realigati on of p seudo2random sequence generato rSUN Shu2qin1,L I N Jun1,ZHAN G B ing2ren2,LUO Jun2(11Key laboratory of Earth Infor m ati on Exp l orati on Instrum entati on of M inistry of Educati on,J ilin U niversity,Changchun130026,China;21College of E lectron Science and Engineering,J ilin U niversity,Changchun130026,China)Abstract:T he random characteristics of p seudo2random sequence has been investigated,and the characteristics of M sequence has been educed,the feedback l ogic functi on of M sequence has been deduced,the M Sequence occur has been designed,the w avefo r m of p seudo2random sequence w as tested, the testing result has been analyzed and compared the relati on sh i p about the step s of feedback sh ift register,sequence length and travel of code(p seudo2random characteristic of the sequence)are co rrect. the feasibility of design w as validated.Key words:p seudo2random sequence;feedback l ogic functi on;frequency dom ain step s引 言伪随机序列具有良好的随机性,它的相关函数接近白噪声的相关函数(∆函数),即有窄的高峰或宽的功率谱密度,使它易于从其他信号或干扰中分离出来。

第1章 基于伪随机序列的传输处理综合设计1.1 伪随机序列伪随机序列包括m 序列、Gold 序列、M 序列和组合序列等,其中最常用到的是m 序列[5,6]。

本文根据m 序列完成了传输处理系统的综合设计。

1.1.1 m 序列的生成m 序列是线性反馈移位寄存器的最大长度序列。

它的生成可用移位寄存器序列发生器的特征多项式来确定,其特征多项式()F x 可以定义为:20120()...ni n i n i F x C x C C x C x C x ===++++∑ (2-1) 其中x 的幂次表示元素相应的位置。

根据代数理论的严格证明,当特征多项式()F x 满足以下3个条件时就一定能够产生m 序列:(1)()F x 是不可约的,即不能再分解因式; (2)()F x 可整除1p x +,这里21n p =-; (3)()F x 不能整除1q x +,这里q p <;目前广泛应用的m 序列都是由移位寄存器构成的。

如图2-1所示,m 序列发生器由n 个二元存储器和模2开关网络组成。

二元存储器通常是一种双稳态触发器,它的两种状态记为0和l ,其状态取决于时钟控制下输入的信息(0或1),例如第i 级移位寄存器的状态取决于时钟脉冲后的第i 一1级移位寄存器的状态。

图中C i 表示为反馈线的两种可能连接状态:C i =1表示连接线连通,即第n -i 级输出加入到反馈中;C i =0表示连接线断开,即第n -i 级输出未参加到反馈中。

图2-1由于移位寄存器的初始状态是随机的,它可能是1,也可能是0。

如果各级移位寄存器的初始状态都为0时,则模2加法器的输出将始终为0,这样就不能产生任何序列。

为了防止这种情况发生,在图2-1中往往还需要增加必要的检测电路。

1.1.2 m 序列的特性分析m 序列由n 级移位寄存器产生的m 序列,其周期为21n -。

m 序列具有如下的一些特性:1) 随机性:在m 序列的一个周期中,0和1出现概率大致相同,0码只比1码多一个,且1的个数为121n --,0的个数为12n -。

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 201911241117.8(22)申请日 2019.12.06(71)申请人 南方科技大学地址 518000 广东省深圳市南山区西丽学苑大道1088号(72)发明人 潘权 胡俊峰 于洪宇 姜培 汪青 (74)专利代理机构 北京品源专利代理有限公司11332代理人 孟金喆(51)Int.Cl.G06F 7/58(2006.01)(54)发明名称伪随机信号发生器(57)摘要本发明公开了一种伪随机信号发生器,包括:信号输入端,用于输入时钟信号;传输模块,与所述信号输入端连接,用于分流放大所述时钟信号;信号产生模块,与所述传输模块连接,用于接收模式切换信号并根据所述模式切换信号和所述时钟信号产生伪随机信号;信号输出模块,与所述信号产生模块连接,用于输出伪随机信号。

本发明提供的一种伪随机信号发生器,通过优化核心电路逻辑架构解决了现有技术中数据传输延迟高、工作速率低、电路功耗高的问题,实现了缩短数据传输延迟进而提高工作速率,并且在需要特定码元信号的情况下,可以切换模式任意产生多种不同的高速伪随机信号源的效果。

权利要求书2页 说明书7页 附图3页CN 110928524 A 2020.03.27C N 110928524A1.一种伪随机信号发生器,其特征在于,包括:信号输入端,用于输入时钟信号;传输模块,与所述信号输入端连接,用于分流放大所述时钟信号;信号产生模块,与所述传输模块连接,用于接收模式切换信号并根据所述模式切换信号和所述时钟信号产生伪随机信号;信号输出模块,与所述信号产生模块连接,用于输出伪随机信号。

2.根据权利要求1中所述的一种伪随机信号发生器,其特征在于,所述信号输入端包括:时钟信号输入端CLK in,用于输入时钟信号。

3.根据权利要求2中所述的一种伪随机信号发生器,其特征在于,所述传输模块包括:电阻缓冲器H1、时钟缓冲器S1、时钟缓冲器S2、时钟缓冲器S3、时钟缓冲器S4和时钟缓冲器S5,所述电阻缓冲器H1第一端连接到所述时钟信号输入端CLK in;所述时钟缓冲器S1第一端连接到所述电阻缓冲器H1的第二端;所述时钟缓冲器S2的第一端连接到所述时钟缓冲器S1的第二端;所述时钟缓冲器S3的第一端连接到所述时钟缓冲器S2的第二端,所述时钟缓冲器S3的第二端连接到所述信号产生模块;所述时钟缓冲器S4的第一端连接到所述述时钟缓冲器S2的第二端,所述时钟缓冲器S4的第二端连接到所述信号产生模块;所述时钟缓冲器S5的第一端连接到所述述时钟缓冲器S2的第二端,所述时钟缓冲器S5的第二端连接到所述信号产生模块。

通信系统专业课程设计一.课题名称:PN(伪随机码)码发生器的设计二.设计目的:1、巩固加深对电子线路的基本知识,提高综合运用专业知识的能力;2、培养学生查阅参考文献,独立思考、设计、钻研专业知识相关问题的能力;3、通过实际制作安装电子线路,学会单元电路以及整机电路的调试与分析方法;4、掌握相关电子线路工程技术规范以及常规电子元器件的性能技术指标;5、了解电气图国家标准以及电气制图国家标准,并利用电子CAD正确绘制电路图;6、培养严肃认真的工作作风与科学态度,建立严谨的工程技术观念;7、培养工程实践能力、创新能力和综合设计能力。

三.设计要求:1、通信系统的原理框图,说明系统中各主要组成部分的功能;2、根据选用的软件编好用于系统仿真的测试文件;3、拟采用的实验芯片的型号可选89c51、TSC 5402、5416、2407及ALTERA的EPM7128CPLD或EP1K30进行硬件验证;4、独立完成课程设计报告,严禁报告内容雷同;5、电路图中的图形符号必须符合国家或国际标准。

四.所用仪器设备:Altera的MAX 7000S系列芯片;方正文祥电脑。

五.设计内容:1、伪随机序列产生原理及作用:随着通信理论的发展,早在20世纪40年代,香农就曾指出,在某些情况下,为了实现最有效的通信,应采用具有白噪声的统计特性的信号。

另外,为了实现高可靠的保密通信,也希望利用随机噪声。

然而,利用随机噪声最大困难是它难以重复产生和处理。

直到60年代,伪随机噪声的出现才使这一难题得到解决。

伪随机噪声具有类似于随机噪声的一些统计特性,同时又便于重复产生和处理。

由于它具有随机噪声的优点,又避免了它的缺点,因此获得了日益广泛的应用。

目前广泛应用的伪随机序列都是由数字电路产生的周期序列得到的,我们称这种周期序列为伪随机序列。

对与伪随机序列有如下几点要求:①应具有良好的伪随机性,即应具有和随机序列类似的随机性;②应具有良好的自相关、互相关和部分相关特性,即要求自相关峰值尖锐,而互相关和部分相关值接近于零。

H a r b i n I n s t i t u t e o f T e c h n o l o g y

EDA技术高级应用

实验报告

姓名:禾小鬼

同组人:

学号:16S

班级:信息2班

指导教师:xxx

院系:电信学院

实验二伪随机信号发生器

一、实验原理

实验要求设计一个伪随机信号发生器,什么是伪随机信号发生器?如果一个序列,一方面它是可以预先确定的,并且是可以重复地生产和复制的;一方面它又具有某种随机序列的随机特性(即统计特性),我们便称这种序列为伪随机序列。

因此可以说,伪随机序列是具有某种随机特性的确定的序列。

它们是由移位寄存器产生确定序列,然而他们却具有某种随机序列的随机特性。

因为同样具有随机特性,无法从一个已经产生的序列的特性中判断是真随机序列还是伪随机序列,只能根据序列的产生办法来判断。

伪随机序列系列具有良好的随机性和接近于白噪声的相关函数,并且有预先的可确定性和可重复性。

这些特性使得伪随机序列得到了广泛的应用,特别是在CDMA系统中作为扩频码已成为CDMA技术中的关键问题。

特性为序列中两种元素出现的个数大致相等;如果把n个元素连续出现叫做一个长度为n的元素游程,则序列中长度为n的元素游程比长度为n+1的元素游程多一倍;序列有类似白噪声的自相关函数。

实验指导书上已经给出一个4位伪随机信号发生器的原理图,如图1所示,一个4位的移位寄存器,第1级和第4级的输出信号通过一个异或门反馈到第1级的输入。

随着连续的时钟周期信号,可以生成15个不同的测试向量。

图1 伪随机二进制序列产生器

在开始之前,首先要明确设计目的,我们的想要用电路图方法实现设计一个“伪随机信号发生器”。

首先设计一个4位伪随机信号发生器,按照图1所示连接电路即可。

然后,扩展到多位。

二实验过程和结果

1.第一步:建立一个新的工程

新建工程的过程中,最重要的是设置器件,不同的器件的,设计之间并不兼容。

会有一个综合的信息框,注明了我所做的设置,看看没问题就可以了。

然后新建一个原理图文件schematic,作为顶层文件,将顶层文件命名为psr(pseudo_random_signal),在上面进行画图。

2.第二步:画电路图

本次实验采用软件自带的器件库的器件即可,然后按照图1画出电路图。

我画的电路图,如图2所示。

其原理为:连续的四个D触发器起到依次平移的作用,即每来一个时钟依次将输出向低位移动,低位x0和高位x3进行异或作为输入。

图2 电路图设计方案

3.行为仿真验证和结果分析

在电路图链接无误后,开始行为仿真,新建仿真文件,由于我使用的是quartus ii 9.1,软件自带仿真功能,不用利用第三方软件仿真。

首先将引脚引入,然后设置各个输入引脚的输入状态,包括clk和pre,最后设置仿真长度。

我设置时钟1M,仿真长度100us。

仿真结果如图3所示。

图3 功能仿真结果

4.修改并实现一个8位伪随机序列发生器

由于画电路图实在麻烦,我采用的是语言的形式实现的8位M序列发生器。

设计的程序如图4所示,然后,进行仿真验证,结果如图5所示。

图4 8位伪随机序列发生器verilog设计方案

图5 8位伪随机序列发生器仿真验证结果

三讨论与分析

由于第二部分已经对实验结果进行了详细的分析,下面讲总结在实验过程中遇到的困难,总结如下:

1.Verilog语言的形式可以更简洁的表达功能,而电路图的形式更容易让

人理解电路的功能。

2.设置实验仿真的时候,要清晰处理好所有输入控制之间的关系,使得在

仿真结果中可以清晰的看出输入控制是否发挥作用。

附录

实验程序:

module PSR(nrst,clk,M_out);

input nrst,clk;

output M_out;

reg M_out;

reg [8:0] A;

reg [8:0]counter;

always @(posedge clk or negedge nrst)

begin

if(! nrst)

A<=9'b1_0000_0000;

else

begin

A<=A>>1;

A[8]<=(A[0]^A[4]^A[5]^A[6]^A[8]);

M_out<=A[0];

end

end

endmodule

指导教师签字:。