VHDL程序结构介绍

- 格式:pptx

- 大小:1.61 MB

- 文档页数:24

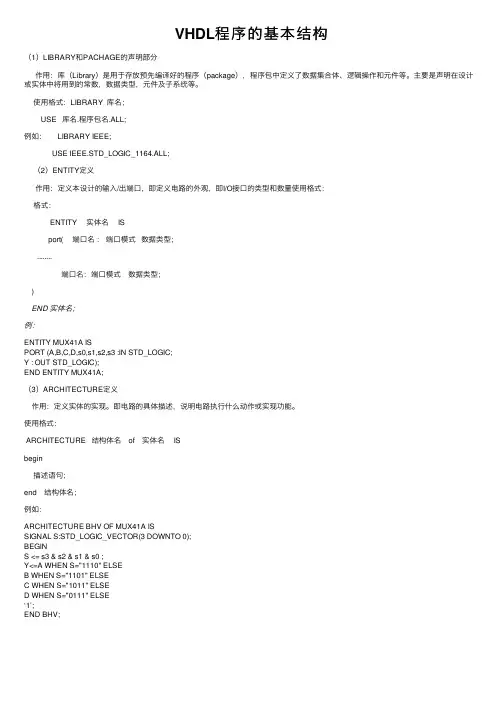

VHDL程序的基本结构(1)LIBRARY和PACHAGE的声明部分作⽤:库(Library)是⽤于存放预先编译好的程序(package),程序包中定义了数据集合体、逻辑操作和元件等。

主要是声明在设计或实体中将⽤到的常数,数据类型,元件及⼦系统等。

使⽤格式:LIBRARY 库名;USE 库名.程序包名.ALL;例如: LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;(2)ENTITY定义作⽤:定义本设计的输⼊/出端⼝,即定义电路的外观,即I/O接⼝的类型和数量使⽤格式:格式:ENTITY 实体名 ISport( 端⼝名:端⼝模式数据类型;........端⼝名:端⼝模式数据类型;)END 实体名;例:ENTITY MUX41A ISPORT (A,B,C,D,s0,s1,s2,s3 :IN STD_LOGIC;Y : OUT STD_LOGIC);END ENTITY MUX41A;(3)ARCHITECTURE定义作⽤:定义实体的实现。

即电路的具体描述,说明电路执⾏什么动作或实现功能。

使⽤格式:ARCHITECTURE 结构体名 of 实体名 ISbegin描述语句;end 结构体名;例如:ARCHITECTURE BHV OF MUX41A ISSIGNAL S:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINS <= s3 & s2 & s1 & s0 ;Y<=A WHEN S="1110" ELSEB WHEN S="1101" ELSEC WHEN S="1011" ELSED WHEN S="0111" ELSE‘1’;END BHV;。

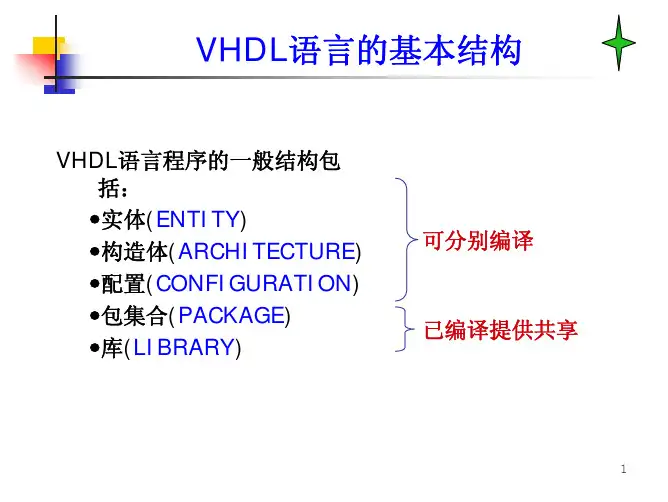

VHDL语言的程序结构与数据类型VHDL语言的程序结构与数据类型第2节 VHDL语言的程序结构与数据类型[学习要求] 掌握VHDL硬件描述语言的基本语法和源文件的结构,学会用VHDL硬件描述语言设计典型数字逻辑电路。

[重点与难点]重点:VHDL语言的程序结构;VHDL语言的数据类型及数据对象。

难点:VHDL的数据对象中的变量和信号的区别。

[理论内容]一、VHDL的程序结构图1 VHDL的程序结构图图1中是VHDL的全部结构,但实际上并不需要全部的结构,就像在许多设计项目中,大部分工程师只用到VHDL其中的30%的语法。

通常图2的结构才是基本和必需的。

USE定义区ENTITY定义区ARCHITECTURE定义区图2 VHDL程序的基本结构由于VHDL已是IEEE规定的标准,所以只是CPLD、FPGA等芯片公司,它们都会提供这个标准的定义库(Library IEEE),而且由于这里面写了许多的定义和参数,初学者一时之间也不容易全部了解,所以全部写上以减轻负担,后面的章节的程序默认也这么写。

程序如: USE IEEE.STD_LOGIC_1164.ALL; 代表本程序引用IEEE 标准定义库的STD_LOGIC_1164全部定义。

VHDL语言编写是属于自由格式,所以在一个完整命令叙述写完时,必须为它加上“;”,作为前后命令的分界,如上述的Use定义命令。

程序的注释采用“--”Entity部分是用来定义电路的输入和输出所用。

定义区的命令格式为:Architecture部分是描述这个电路的功能部分,其书写的语法因具体电路的功能而定,下一节将详细介绍。

_以下是一个简单的例子:library ieee; --采用ieee标准库use ieee.std_logic_1164.all; --使用其中的定义包,以后照着写即可use IEEE.STD_LOGIC_UNSIGNED.all; --同上use IEEE.STD_LOGIC_ARITH.all; --同上entity test is --定义实体名port( --以下是定义输入输出端口pin1 : in std_logic; --pin1为输入端口,数据类型为std_logic pin2 : in std_logic; --同上pin3 : out std_logic --pin3为输出端口,数据类型为std_logic ); --端口定义完成end test; --实体描述完成architecture behavior of test is --定义结构体begin --结构体开始pin3<=pin1 and pin2; --该语法表示将pin1和pin2相与送至pin3end behavior; --结构体描述完成其实VHDL语言在书写上和高级语言的描述十分相似(风格更似于Ada语言),与C语言的比较如图3所示,大家不要把它看得很神秘。

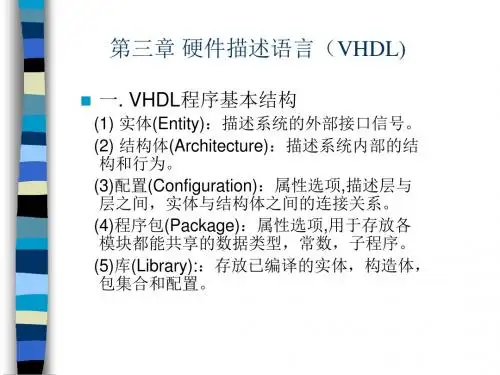

简述VHDL的基本结构及每部分的基本功能。

1.1. 简述VHDL的基本结构及每部分的基本功能。

(1)库库是经编译后的数据集合,库中存放的是各种程序包、实体定义、结构体描述等。

设计人员在用VHDL 语言设计系统时,库中内容有的可作为标准,有的可作为资源被引用。

库的作用就在于使设计者可以共享已经编译过的设计文件及有用数据。

(2)程序包程序包是VHDL程序的公共存储区,在程序包内说明的数据对实体是透明的。

程序包由程序包说明和程序包体组成。

(3)实体实体可以表示小到一个与门,也可以大到一个数字系统,这个系统可以像微处理器一样的复杂。

在实体的说明部分主要完成设计对象的输入输出端口名称、传输方向、数据类型的定义,即端口的定义。

(4)结构体结构体是设计实体的具体描述,如果把设计实体抽象为一个功能方块图,结构体则描述这个功能方块图内部的具体逻辑实现细节。

一个设计实体的内部实现细节通过结构体的具体描述表现出来。

(5)配置配置是用于描述设计不同层次之间的关系和实体与结构体之间的连接关系。

在实体与结构体之间的连接关系配置说明中,设计者可以利用配置语句为实体提供不同的结构体与之相匹配。

在仿真设计中,可以利用不同配置方式选择不同结构体,分别对不同结构体进行仿真测试。

2. 简述VHDL语言实体申明中:IN、OUT、BUFFER和INOUT 等端口模式各自的特点。

IN:输入型,只读模式。

OUT:输出型,只写。

BUFFER:缓冲型,带有读功能的输出模式,即输出并向内部反馈,out相似,但可读。

INOUT:输入输出型,可读可写,可以通过该端口读入或写出信息。

3. 在VHDL语言中,标识符必须遵循一些规则,有哪些规则?(1)标示符的第一个字母必须是英文字母。

(2)标示符的最后一个字母不能使下划线字符。

(3)标示符不允许连续出现两个下划线字符。

(4)标示符不区分字母的大小写。

(5)VHDL的保留字不能用于作为标示符使用。

4. VHDL的数据对象有哪几种,它们之间有什么不同?答:VHDL的数据对象包括信号、常量、变量和文件4类。

VHDL的基本结构由实体(ENTITY)和结构体(ARCHITECTURE)两部分构成。

其中,结构化描述主要使用AND、OR等逻辑运算符来描述元件之间的连接关系,具体步骤包括:

1.原件说明,用于说明原件的调用,并描述该元件的接口。

2.原件例化,指定原件的安放位置,并确定与其他元件放置的连线关系。

3.原件配置,指定原件所用的设计实体。

另外,结构化描述程序的主要步骤包括:

1.绘制框图。

2.原件说明。

3.信号说明。

4.元件例化。

5.添加必要的框架。

以上步骤和内容仅供参考,如需了解更多关于VHDL结构化描述的信息,建议查阅专业书籍或咨询专业技术人员。