数字电子技术第8章

- 格式:ppt

- 大小:3.40 MB

- 文档页数:7

第8章 可编程逻辑器件一、选择题1.(多选)关于PROM和PAL的结构,以下叙述正确的是()。

A.PROM的与阵列固定,不可编程B.PROM与阵列、或阵列均不可编程C.PAL与阵列、或阵列均可编程D.PAL的与阵列可编程【答案】AD【解析】PROM由存储矩阵、地址译码器和输出电路组成。

其中与阵列是固定的,不可编程,初始时所有存储单元中都存入了1,可通过将所需内容自行写入PROM而得到要求的ROM,PROM的内容一经写入以后(改变的是或阵列),不能修改。

PAL器件由可编程的与逻辑阵列、固定的或逻辑阵列和输出电路三部分组成。

二、填空题1.与PAL相比,GAL器件有可编程的输出结构,它是通过对______行编程设定其______的工作模式来实现的,而且由于采用了______的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

【答案】机构控制字;输出逻辑宏单元;E2CMOS2.PAL是______可编程,EPROM是______可编程。

【答案】与阵列;或阵列3.GAL 是______可编程,GAL 中的OLMC 称______【答案】与阵列;输出逻辑宏单元4.在图8-1所示的可编程阵列逻辑(PAL )电路中,Y 1=______,Y 3=______。

图8-1【答案】;123234134124I I I I I I I I I I I I +++12I I ⊕【解析】×表示连通,在一条线上的×表示与,然后通过或门连接在一起。

三、简答题1.如图8-2所示为PAL16L8的一部分电路,试分析该电路,写出电路在X 控制下的函数F 对应于输入A 、B 、C 的逻辑表达式。

图8-2答:当X=0时,F所在三态门选通;X=1时,三态门关闭。

故该电路的逻辑关系式为:。

2.下面图8-3所示的3个卡诺图代表3个4变量逻辑的逻辑函数。

(1)用PROM实现,画出码点矩阵图;(2)用PLA实现,画出码点矩阵图。

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000 二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:()16=6*162+13*161+14*160+13*16-1+8*16-2=()10所以:()16=()2=()8=()10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111 111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10 (4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10 所以:()16.11111101)2=(363)8=(1950.98828125)10、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则二、2、×4、×三、1、B3、D5、C练习题:2.2:(4)解:(8)解:2.3:(2)证明:左边=右式所以等式成立(4)证明:左边=右边=左边=右边,所以等式成立(1)(3)2.6:(1)2.7:(1)卡诺图如下:BCA00 01 11 100 1 11 1 1 1所以,2.8:(2)画卡诺图如下:BC A 0001 11 100 1 1 0 11 1 1 1 12.9:如下:CDAB00 01 11 1000 1 1 1 101 1 111 ×××10 1 ××2.10:(3)解:化简最小项式:最大项式:2.13:(3)技能题:2.16 解:设三种不同火灾探测器分别为A、B、C,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:BC00 01 11 10A0 0 0 1 01 0 1 1 1第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空;二、1、√8、√;三、1、A4、D练习题:、解:(a)Ω,开门电阻3kΩ,R>R on,相当于接入高电平1,所以(e) 因为接地电阻510ΩkΩ,R<R off,相当于接入高电平0,所以、、解:(a)(c)(f)、解: (a)、解:输出高电平时,带负载的个数2020400===IH OH OH I I N G 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===IL OL OL I I NG反相器可带17个同类反相器EN=1时,EN=0时,根据题意,设A为具有否决权的股东,其余两位股东为B、C,画卡诺图如下,BC00 01 11 10A0 0 0 0 01 0 1 1 1则表达结果Y的表达式为:逻辑电路如下:技能题::解:根据题意,A、B、C、D变量的卡诺图如下:CD00 01 11 10AB00 0 0 0 001 0 0 0 0 11 0 1 1 1 10 0 0 0 0电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C练习题:4.1;解:(a),所以电路为与门。

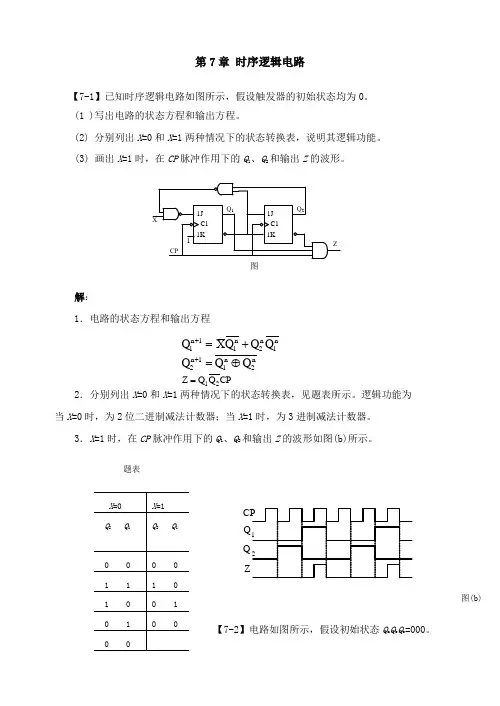

第7章 时序逻辑电路【7-1】已知时序逻辑电路如图所示,假设触发器的初始状态均为0。

(1 )写出电路的状态方程和输出方程。

(2) 分别列出X =0和X =1两种情况下的状态转换表,说明其逻辑功能。

(3) 画出X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形。

1J 1KC11J 1KC1Q 1Q 2CPXZ1图解:1.电路的状态方程和输出方程n 1n2n 11n 1Q Q Q X Q +=+n 2n 11n 2Q Q Q ⊕=+ CP Q Q Z 21=2.分别列出X =0和X =1两种情况下的状态转换表,见题表所示。

逻辑功能为 当X =0时,为2位二进制减法计数器;当X =1时,为3进制减法计数器。

3.X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形如图(b)所示。

题表Q Q Z图(b)【7-2】电路如图所示,假设初始状态Q a Q b Q c =000。

(1) 写出驱动方程、列出状态转换表、画出完整的状态转换图。

(2) 试分析该电路构成的是几进制的计数器。

Q c图解:1.写出驱动方程1a a ==K J ncn a b b Q Q K J ⋅== n b n a c Q Q J = n a c Q K = 2.写出状态方程n a 1n a Q Q =+ n a n a n a n a n c n a 1n b Q Q Q QQ Q Q +=+ nc n a n c n b n a 1n b Q Q Q Q Q Q +=+3.列出状态转换表见题表,状态转换图如图(b)所示。

图7.2(b)表7.2状态转换表CP na nbc Q Q Q 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 16 0 0 0n4.由FF a 、FF b 和FF c 构成的是六进制的计数器。

【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q 或Q )填入下表解:题表7-3下降沿触发 由 Q 端引出进位 由Q 端引出借位触发方式 加法计数器 减法计数器上升沿触发 由Q 端引出进位 由Q 端引出借位【7-4】电路如图(a)所示,假设初始状态Q 2Q 1Q 0=000。

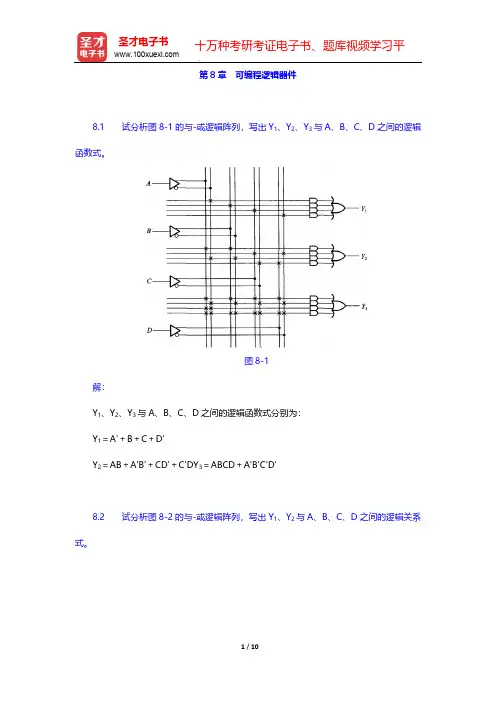

第8章 可编程逻辑器件8.1试分析图8-1的与-或逻辑阵列,写出Y 1、Y 2、Y 3与A 、B 、C 、D 之间的逻辑函数式。

图8-1解:Y 1、Y 2、Y 3与A 、B 、C 、D 之间的逻辑函数式分别为:Y 1=A'+B +C +D'Y 2=AB +A'B'+CD'+C'DY 3=ABCD +A'B'C'D'8.2试分析图8-2的与-或逻辑阵列,写出Y 1、Y 2与A 、B 、C 、D 之间的逻辑关系式。

图8-2解:Y1、Y2与A、B、C、D之间的逻辑关系式分别为:Y1=(AB'+A'B+CD)'当AB=1时,Y2=(CD'+C'D)',否则Y2呈现高阻态。

8.3 试分析图8-3中由PAL16L8构成的逻辑电路,写出Y1、Y2、Y3与A、B、C、D、E之间的逻辑关系式。

图8-3解:Y1、Y2、Y3与A、B、C、D、E之间的逻辑关系式分别为:Y1=(A'B'+A'C'+A'D'+A'E'+B'C'+B'D'+B'E'+C'D'+C'E'+D'E')'Y2=ABCD+ACDE+ABCE+ABDE+BCDEY 3=ABCDE8.4 用PAL16L8产生如下一组组合逻辑函数。

画出与-或逻辑阵列编程后的电路图。

PAL16L8的电路图见图8-3。

解:先将组合逻辑函数化为与-或-非形式。

得到用PAL16L8的实现如图8-4所示。

图8-48.5 试分析图8-5给出的用PAL16R4构成的时序逻辑电路,写出电路的驱动方程、状态方程、输出方程,画出电路的状态转换图。

工作时,11脚接低电平。

图8-5解:若11脚接低电平,电路正常工作。

《数字电子技术》目录第1章数制与编码1.1 数字电路基础知识1.1.1 模拟信号与数字信号1.1.2 数字电路的特点1.2 数制1.2.1 十进制数1.2.2 二进制数1.2.3 八进制数1.2.4 十六进制数1.3 数制转换1.3.1 二进制数与八进制数的相互转换1.3.2 二进制数与十六进制数的相互转换1.3.3 十进制数与任意进制数的相互转换1.4 二进制编码1.4.1 加权二进制码1.4.2 不加权的二进制码1.4.3 字母数字码1.4.4 补码1.5带符号二进制数的加减运算1.5.1 加法运算1.5.2 减法运算第2章逻辑门2.1 基本逻辑门2.1.1 与门2.1.2 或门2.1.3 非门2.2 复合逻辑门2.2.1 与非门2.2.2 或非门2.2.3 异或门2.2.4 同或门2.3 其它逻辑门2.3.1 集电极开路逻辑门2.3.2 集电极开路逻辑门的应用2.3.3 三态逻辑门2.4 集成电路逻辑门2.4.1 概述2.4.2 TTL集成电路逻辑门2.4.3 CMOS集成电路逻辑门2.4.4 集成逻辑门的性能参数2.4.5 TTL与CMOS集成电路的接口*第3章逻辑代数基础3.1 概述3.1.1 逻辑函数的基本概念3.1.2 逻辑函数的表示方法3.2 逻辑代数的运算规则3.2.1 逻辑代数的基本定律3.2.2 逻辑代数的基本公式3.2.3 摩根定理3.2.4 逻辑代数的规则3.3 逻辑函数的代数化简法3.3.1 并项化简法3.3.2 吸收化简法3.3.3 配项化简法3.3.4 消去冗余项法3.4 逻辑函数的标准形式3.4.1 最小项与最大项3.4.2 标准与或表达式3.4.3 标准或与表达式3.4.4 两种标准形式的相互转换3.4.5 逻辑函数表达式与真值表的相互转换3.5 逻辑函数的卡诺图化简法3.5.1 卡诺图3.5.2 与或表达式的卡诺图表示3.5.3 与或表达式的卡诺图化简3.5.4 或与表达式的卡诺图化简3.5.5 含无关项逻辑函数的卡诺图化简3.5.6 多输出逻辑函数的化简*第4章组合逻辑电路4.1 组合逻辑电路的分析4.1.1 组合逻辑电路的定义4.1.2 组合逻辑电路的分析步骤4.1.3 组合逻辑电路的分析举例4.2 组合逻辑电路的设计4.2.1 组合逻辑电路的一般设计步骤4.2.2 组合逻辑电路的设计举例4.3 编码器4.3.1 编码器的概念4.3.2 二进制编码器4.3.3 二-十进制编码器4.3.4 编码器应用举例4.4 译码器4.4.1 译码器的概念4.4.2 二进制译码器4.4.3 二-十进制译码器4.4.4 用译码器实现逻辑函数4.4.5 显示译码器4.4.6 译码器应用举例4.5 数据选择器与数据分配器4.5.1 数据选择器4.5.2 用数据选择器实现逻辑函数4.5.3 数据分配器4.5.4 数据选择器应用举例4.6 加法器4.6.1 半加器4.6.2 全加器4.6.3 多位加法器4.6.4 加法器应用举例4.6.5 加法器构成减法运算电路*4.7 比较器4.7.1 1位数值比较器4.7.2 集成数值比较器4.7.3 集成数值比较器应用举例4.8 码组转换电路4.8.1 BCD码之间的相互转换4.8.2 BCD码与二进制码之间的相互转换4.8.3 格雷码与二进制码之间的相互转换4.9 组合逻辑电路的竞争与冒险4.9.1 冒险现象的识别4.9.2 消除冒险现象的方法第5章触发器5.1 RS触发器5.1.1 基本RS触发器5.1.2 钟控RS触发器5.1.3 RS触发器应用举例5.2 D触发器5.2.1 电平触发D触发器5.2.2 边沿D触发器5.3 JK触发器5.3.1 主从JK触发器5.3.2 边沿JK触发器5.4 不同类型触发器的相互转换5.4.1 概述5.4.2 D触发器转换为JK、T和T'触发器5.4.3 JK触发器转换为D触发器第6章寄存器与计数器6.1 寄存器与移位寄存器6.1.1 寄存器6.1.2 移位寄存器6.1.3移位寄存器应用举例6.2 异步N进制计数器6.2.1 异步n位二进制计数器6.2.2 异步非二进制计数器6.3 同步N进制计数器6.3.1 同步n位二进制计数器6.3.2 同步非二进制计数器6.4 集成计数器6.4.1 集成同步二进制计数器6.4.2 集成同步非二进制计数器6.4.3 集成异步二进制计数器6.4.4 集成异步非二进制计数器6.4.5 集成计数器的扩展6.4.6 集成计数器应用举例第7章时序逻辑电路的分析与设计7.1 概述7.1.1 时序逻辑电路的定义7.1.2 时序逻辑电路的结构7.1.3 时序逻辑电路的分类7.2 时序逻辑电路的分析7.2.1时序逻辑电路的分析步骤7.2.2 同步时序逻辑电路分析举例7.2.3 异步时序逻辑电路分析举例7.3 同步时序逻辑电路的设计7.3.1 同步时序逻辑电路的基本设计步骤7.3.2 同步时序逻辑电路设计举例第8章存储器与可编程器件8.1 存储器概述8.1.1 存储器的分类8.1.2 存储器的相关概念8.1.3 存储器的性能指标8.2 RAM8.2.1 RAM分类与结构8.2.2 SRAM8.2.3 DRAM8.3 ROM8.3.1 ROM分类与结构8.3.2 掩膜ROM8.3.3 可编程ROM8.3.4 可编程ROM的应用8.4 快闪存储器(Flash Memory)8.4.1 快闪存储器的电路结构8.4.2 闪存与其它存储器的比较8.5 存储器的扩展8.5.1 存储器的位扩展法8.5.2 存储器的字扩展法8.6 可编程阵列逻辑8.6.1 PAL的电路结构8.6.2 PAL器件举例8.6.3 PAL器件的应用8.7 通用阵列逻辑8.7.1 GAL的性能特点8.7.2 GAL的电路结构8.7.3 OLMC8.7.4 GAL器件的编程与开发8.8 CPLD、FPGA和在系统编程技术8.8.1 数字可编程器件的发展概况8.8.2数字可编程器件的编程语言8.8.3数字可编程器件的应用实例第9章D/A转换器和A/D转换器9.1 概述9.2 D/A转换器9.2.1 D/A转换器的电路结构9.2.2 二进制权电阻网络D/A转换器9.2.3 倒T型电阻网络D/A转换器9.2.4 D/A转换器的主要技术参数9.2.5 集成D/A转换器及应用举例9.3 A/D转换器9.3.1 A/D转换的一般步骤9.3.2 A/D转换器的种类9.3.3 A/D转换器的主要技术参数9.3.4 集成A/D转换器及应用举例第10章脉冲波形的产生与整形电路10.1 概述10.2 多谐振荡器10.2.1 门电路构成的多谐振荡器10.2.2 采用石英晶体的多谐振荡器10.3 单稳态触发器10.3.1 门电路构成的单稳态触发器10.3.2 集成单稳态触发器10.3.3 单稳态触发器的应用10.4 施密特触发器10.4.1 概述10.4.2 施密特触发器的应用10.5 555定时器及其应用10.5.1 电路组成及工作原理10.5.2 555定时器构成施密特触发器10.5.3 555定时器构成单稳态触发器10.5.4 555定时器构成多谐振荡器第11章数字集成电路简介11.1 TTL门电路11.1.1 TTL与非门电路11.1.2 TTL或非门电路11.1.3 TTL与或非门电路11.1.4 集电极开路门电路与三态门电路11.1.5 肖特基TTL与非门电路11.2 CMOS门电路11.2.1 概述11.2.2 CMOS非门电路11.2.3 CMOS与非门电路11.2.4 CMOS或非门电路11.2.5 CMOS门电路的构成规则11.3 数字集成电路的使用。

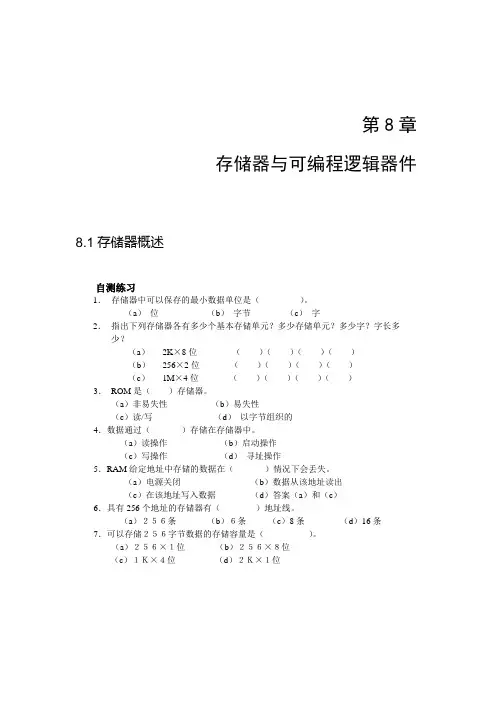

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a)2K×8位()()()()(b)256×2位()()()()(c)1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有()地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是()。

(a)256×1位(b)256×8位(c)1K×4位(d)2K×1位答案:1. a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

"数字电子技术"知识点第1章 数字逻辑根底1.数字信号、模拟信号的定义2.数字电路的分类3.数制、编码其及转换要求:能熟练在10进制、2进制、8进制、16进制、8421BCD 之间进展相互转换。

举例1:〔37.25〕10= ( )2= ( )16= ( )8421BCD解:〔37.25〕10= (100101.01)2= ( 25.4)16= (00110111.00100101)8421BCD4.根本逻辑运算的特点与运算:见零为零,全1为1;或运算:见1为1,全零为零;与非运算:见零为1,全1为零;或非运算:见1为零,全零为1;异或运算:相异为1,一样为零;同或运算:一样为1,相异为零;非运算:零变 1, 1变零;要求:熟练应用上述逻辑运算。

5.数字电路逻辑功能的几种表示方法及相互转换。

①真值表〔组合逻辑电路〕或状态转换真值表〔时序逻辑电路〕:是由变量的所有可能取值组合及其对应的函数值所构成的表格。

②逻辑表达式:是由逻辑变量和与、或、非3种运算符连接起来所构成的式子。

③卡诺图:是由表示变量的所有可能取值组合的小方格所构成的图形。

④逻辑图:是由表示逻辑运算的逻辑符号所构成的图形。

⑤波形图或时序图:是由输入变量的所有可能取值组合的高、低电平及其对应的输出函数值的高、低电平所构成的图形。

⑥状态图〔只有时序电路才有〕:描述时序逻辑电路的状态转换关系及转换条件的图形称为状态图。

要求:掌握这五种〔对组合逻辑电路〕或六种〔对时序逻辑电路〕方法之间的相互转换。

6.逻辑代数运算的根本规则①反演规则:对于任何一个逻辑表达式Y ,如果将表达式中的所有"·〞换成"+〞,"+〞换成"·〞,"0〞换成"1〞,"1〞换成"0〞,原变量换成反变量,反变量换成原变量,则所得到的表达式就是函数Y 的反函数Y 〔或称补函数〕。

第八章半导体存储器和可编程逻辑器件一、填空题1、一个10位地址码、8位输出的ROM,其存储容量为或。

2、将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM。

该ROM有根地址线,有根数据读出线。

二、综合题1、试写出图6-1所示阵列图的逻辑函数表达式和真值表,并说明其功能。

01F2F3图6-1 例6-1逻辑图2、试用256×4位的RAM扩展成1024×8位存储器。

3、下列RAM各有多少条地址线?⑴512×2位⑵1K×8位⑶2K×1位⑷16K×1位⑸256×4位⑹64K×1位4、写出由ROM所实现的逻辑函数的表达式。

(8分)Y1Y25、四片16×4RAM 和逻辑门构成的电路如图6-7所示。

试回答:AB AB 4AB AB 0地址线数据线图6-7 多片RAM 级联逻辑图⑴单片RAM 的存储容量,扩展后的RAM 总容量是多少?⑵图6-7所示电路的扩展属位扩展,字扩展,还是位、字都有的扩展? ⑶当地址码为00010110时,RAM0~RAM3,哪几片被选中?6.用ROM 设计一个组合逻辑电路,用来产生下列一组逻辑函数。

画出存储矩阵的点阵图。

D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=1 D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=2 D C B D B A Y ⋅⋅+⋅⋅=3D B D B Y ⋅+⋅=47、画出实现下面双输出逻辑函数的PLD 表示。

D C AB CD B A D C B A D C B A D C B A f ABCC B A C B A C B A f ),,,( ),,(21+++=++=三、简答题1、可编程逻辑器件是如何进行分类的?2、GAL16V8的OLMC 中4个数据选择器各有多少功能?3、ROM 和RAM 有什么相同和不同之处?ROM 写入信息有几种方式?4、为什么用ROM 可以实现逻辑函数式?第八章 习题答案一、填空题1、2138K 2、11 16 二、综合题1、解:根据与阵列的输出为AB 的最小项和阵列图中有实心点·为1,无·为0,可以写出AB W F ==30B A AB B A B A W W W F +=++=++=3211B A B A B A F ⊕=+=2AB B A B A B A B A W W W F =+=++=++=2103从上述逻辑表达式可以看出,图6-1所示阵列图实现了输入变量A 、B 的四种逻辑运算:与、或、异或和与非。

第一章数制和码制2.(单选题) 与二进制数等值的十进制数为()。

A. 9.21B. 9.3125C. 9.05D. 9.5参考答案:B3.(单选题) 与二进制数等值的十六进制数为()。

A. B0.C3B. C. 2C.C3D. 参考答案:D参考答案:B5.(单选题) 与二进制数等值的十进制数为()。

A. 6.11B. 6.21C. 6.625D. 6.5参考答案:C6.(单选题) 与二进制数等值的八进制数为()。

A. 6.44B. 6.41C. 3.44D. 3.41参考答案:A13.(单选题) 的原码、反码、补码分别是()。

A.11011、00100、00101 B.11011、10100、10101C.01011、00100、00101 D.01011、10100、10101参考答案:B第二章逻辑代数基础1.(单选题) 将函数式化成最小项之和的形式为()。

参考答案:D2.(单选题) 函数的反函数为()。

参考答案:B3.(单选题) 将函数式化成最小项之和的形式为()。

参考答案:A4.(单选题) 函数的反函数为()。

参考答案:B5.(单选题) 已知函数的卡诺图如图2-1所示, 则其最简与或表达式为()。

参考答案:A6.(单选题) 某电路当输入端A或B任意一个为高电平时,输出Y为高电平,当A和B均为低电平时输出为低电平,则输出Y与输入A、B之间的逻辑关系为Y=()。

参考答案:B7.(单选题) 全体最小项之和为()。

参考答案:C8.(单选题) 以下与逻辑表达式相等的式子是()。

参考答案:D9.(单选题) 和与非-与非逻辑表达式相等的式子是()。

参考答案:C11.(单选题) 某电路当输入端A或B任意一个为低电平时,输出Y为低电平,当A和B均为高电平时输出为高电平,则输出Y与输入A、B之间的逻辑关系为Y=()。

参考答案:A12.(单选题) 任何两个最小项的乘积为()。

参考答案:A13.(单选题) 以下与逻辑表达式相等的式子是()。

数字电子技术》知识点数字电子技术》知识点第1章数字逻辑基础本章主要介绍数字电路的基础知识,包括数字信号、模拟信号的定义,数字电路的分类,数制、编码及其转换,基本逻辑运算的特点,数字电路逻辑功能的几种表示方法及相互转换,逻辑代数运算的基本规则等内容。

1.数字信号、模拟信号的定义数字信号是离散的,只有两种状态,即高电平和低电平,而模拟信号是连续的,可以有无限种状态。

2.数字电路的分类数字电路分为组合逻辑电路和时序逻辑电路。

组合逻辑电路的输出只与输入有关,而时序逻辑电路的输出还与时间有关。

3.数制、编码及其转换我们需要熟练掌握在10进制、2进制、8进制、16进制、8421BCD之间进行相互转换的方法。

举例1:将(37.25)10转换为2进制、16进制、8421BCD码解:(37.25)10 = (.01)2 = (25.4)16 =(xxxxxxxx.xxxxxxxx)8421BCD4.基本逻辑运算的特点我们需要掌握与运算、或运算、与非运算、或非运算、异或运算、同或运算、非运算等基本逻辑运算的特点。

5.数字电路逻辑功能的几种表示方法及相互转换我们需要掌握真值表、逻辑表达式、卡诺图、逻辑图、波形图、状态图等几种表示方法,并能够相互转换。

6.逻辑代数运算的基本规则我们需要掌握反演规则和对偶规则,能够求逻辑函数的反函数和对偶函数。

反演规则是将逻辑表达式中的“·”换成“+”,“+”换成“·”,“”换成“1”,“1”换成“”,原变量换成反变量,反变量换成原变量,得到函数的反函数。

对偶规则是将逻辑表达式中的“·”换成“+”,“+”换成“·”,“”换成“1”,“1”换成“”,而变量保持不变,得到函数的对偶函数。

本章内容是数字电路的基础,是后续研究的重要基础。

需要认真掌握并应用于实际操作中。

7.逻辑函数化简逻辑函数化简有两种方法:公式法和图形法。

公式法是利用逻辑代数的基本公式、定理和规则来化简逻辑函数;图形法是将逻辑函数用卡诺图来表示,利用卡诺图来化简逻辑函数。