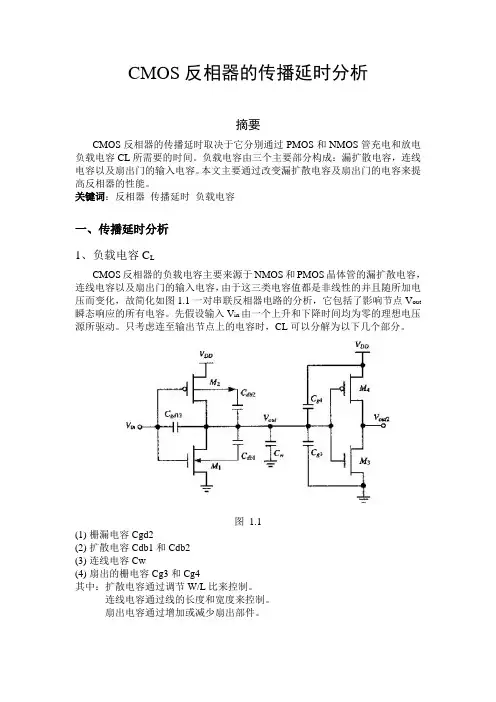

反相器及CMOS反相器性能分析

- 格式:ppt

- 大小:2.40 MB

- 文档页数:51

cmos常用电路中异或门及反相器的功能[CMOS常用电路中异或门及反相器的功能]CMOS(Complementary Metal-Oxide-Semiconductor)是一种常用的集成电路技术,在数字电路中起着重要的作用。

在CMOS常用电路中,异或门和反相器是常常会使用到的两种基本的逻辑门。

它们在数字电路设计中起着至关重要的作用,本文将探讨它们的功能以及在CMOS电路中的应用。

首先,让我们来了解一下反相器的功能及原理。

反相器是一种基本的逻辑门,它的输出与输入恰好相反。

也就是说,当输入为高电平时,输出为低电平;而当输入为低电平时,输出为高电平。

反相器常用来翻转输入信号的逻辑电平,它的符号通常表示为一个箭头,箭头指向一个小圆圈,表示逻辑反相。

在CMOS电路中,反相器通常是通过两个晶体管和一个负载电阻来实现的。

当输入为高电平时,其中一个晶体管导通,另一个截至,从而让输出变为低电平;而当输入为低电平时,另一个晶体管导通,一个截至,输出变为高电平。

这种反相器的实现方式在CMOS电路中非常常见,因为它能够提供高稳定性和高性能。

接下来我们来了解一下异或门的功能及原理。

异或门是一种逻辑门,它的输出为1的条件是两个输入信号不同。

换句话说,只有在一个输入为1,另一个输入为0的时候,输出才会为1;其他情况下输出为0。

异或门的符号通常表示为一个希腊字母“Σ”,表示逻辑异或。

在CMOS电路中,异或门通常是通过多个晶体管和负载电阻来实现的。

它的结构相对复杂一些,但原理其实和反相器类似。

通过合理地配置晶体管的导通状态,可以实现对两个输入信号进行异或运算,并得到相应的输出。

CMOS异或门通常具有高速、高稳定性和低功耗的特点,因此在数字电路设计中得到了广泛的应用。

总的来说,反相器和异或门是CMOS电路中常用的两种基本逻辑门,它们分别提供了对输入信号进行反相和异或运算的功能。

在数字电路设计中,我们可以借助这两种逻辑门来实现各种复杂的逻辑功能,比如加法、减法、乘法等等。

数字集成电路学习总结5CMOS反相器今天开始总结数字集成电路。

这本书其实算是本科最难的⼀本了,细节过多⽆法卒读,涉及到的知识也⾮常全⾯。

实际上本科课程安排中并为将其作为重点,我们的课⾮常⽔,不知道讲了什么。

今天详细总结⼀下。

当时然由于内容过多,⽆法全部涵盖,只能⼤致总结,并着重记录定性的结论。

涉及到计算之类的问题,就只能略过了。

第五章 COMS反相器5.1 引⾔为什么从第五章开始,原因是这章⽐较基础,详细学习CMOS反相器后,才能继续看组合电路和时序电路等等。

研究的对象有如下⼏个指标:成本(复杂性和⾯积)、完整性和稳定性(静态特性)、性能(动态特性)、能量效率(功耗)。

5.2 静态CMOS反相器——直观综述课本上的描述:晶体管只不过是⼀个具有⽆限关断电阻和有限导通电阻的开关。

以开关来理解,可以推导出其他重要特性:1、输出⾼电平和低电平分别为VDD和GND,换⾔之,电压摆幅等于电源电压。

因此噪声容限很⼤。

2、逻辑电平与器件的相对尺⼨⽆关,所以晶体管可以采⽤最⼩尺⼨。

这⾥有⼀个概念叫⽆⽐逻辑3、稳态时,输出和VDD或GND之间总存在有限电阻的通路。

因此⼀个设计良好的CMOS反相器具有低输出阻抗,这使得它对噪声和⼲扰不敏感。

4、输⼊电阻极⾼。

理论上,单个反相器可以驱动⽆穷个门,或者说有⽆穷⼤的扇出。

但很快我们发现增加扇出也会增加传播延时。

因此扇出不会影响稳态特性,会影响瞬态特性。

5、忽略漏电流的话,意味着⽆静态功耗。

之前常⽤的是NMOS电路,静态功耗不为0,限制了集成度。

后来必须转向CMOS。

电压传输特性(VTC)的性质和形状可以通过图解法迭加两管的图像得到。

结果是观察到VTC具有⾮常窄的过渡区。

我们可以把开关特性简化为RC电路,⼀个快速门的设计是通过减⼩输出电容或者减⼩晶体管的导通电阻(增⼤宽长⽐)实现的。

5.3 CMOS反相器稳定性的评估——静态特性5.3.1 开关阈值开关阈值VM定义是Vin=Vout的点,利⽤图解法可以看出。

CMOS集成电路的性能及特点CMOS功耗低CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。

实际上,由于存在漏电流,CMOS 电路尚有微量静态功耗。

单个门电路的功耗典型值仅为20mW,动态功耗(在1MHz工作频率时)也仅为几mW。

工作电压范围宽CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。

国产CC4000系列的集成电路,可在3~18V电压下正常工作。

逻辑摆幅大CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电影低电位VSS。

当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。

因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

抗干扰能力强CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。

随着电源电压的增加,噪声容限电压的绝对值将成比例增加。

对于VDD=15V的供电电压(当VSS=0V时),电路将有7V左右的噪声容限。

输入阻抗高CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

温度稳定性能好由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。

一般陶瓷金属封装的电路,工作温度为-55 ~ +125℃;塑料封装的电路工作温度范围为-45 ~ +85℃。

扇出能力强扇出能力是用电路输出端所能带动的输入端数来表示的。

由于CMOS集成电路的输入阻抗极高,因此电路的输出能力受输入电容的限制,但是,当CMOS集成电路用来驱动同类型,如不考虑速度,一般可以驱动50个以上的输入端。

TTL和CMOS器件种类和性能的比较TTL和CMOS器件的功能分类1:门电路和反相器逻辑门主要有与门74X08、与非门74X00、或门74X32、或非门74X02、异或门74X86、反相器74X04等。

2:选择器选择器主要有2-1、4-1、8-1选择器74X157、74X153、74X151等。

3:编/译码器编/译码器主要有2/4、3/8和4/16译码器74X139、74X138、74X154等。

4:计数器计数器主要有同步计数器74X161和异步计数器74X393等。

5:寄存器寄存器主要有串-并移位寄存器74X164和并-串寄存器74X165等。

6:触发器触发器主要有J-K触发器、带三态的D触发器74X374、不带三态的D触发器74X74、施密特触发器等。

7:锁存器锁存器主要有D型锁存器74X373、寻址锁存器74X259等。

8:缓冲驱动器缓冲驱动器主要有带反向的缓冲驱动器74X240和不带反向的缓冲驱动器74X244等。

9:收发器收发器主要有寄存器收发器74X543、通用收发器74X245、总线收发器等。

10:总线开关总线开关主要包括总线交换和通用总线器件等。

11:背板驱动器背板驱动器主要包括TTL或LVTTL电平与GTL/GTL+(GTLP)或BTL之间的电平转换器件。

TTL和CMOS逻辑器件的工艺分类1:Bipolar(双极)工艺TTL、S、LS、AS、F、ALS。

2::CMOS工艺HC、HCT、CD40000、ACL、FCT、LVC、LV、CBT、ALVC、AHC、AHCT、CBTLV、AVC、GTLP。

3:BiCMOS工艺BCT、ABT、LVT、ALVT。

TTL和CMOS逻辑器件的电平分类TTL和CMOS的电平主要有以下几种:5VTTL、5VCMOS(Vih≥0.7*Vcc,Vil≤0.3*Vcc)、3.3V电平、2.5V电平等。

1:5V的逻辑器件5V器件包含TTL、S、LS、ALS、AS、HCT、HC、BCT、74F、ACT、AC、AHCT、AHC、ABT等系列器件2:3.3V及以下的逻辑器件包含LV的和V 系列及AHC和AC系列,主要有LV、AHC、AC、ALB、LVC、ALVC、LVT 等系列器件。