EDA 第二章 VHDL语言应用基础1(基本结构、数据类型)

- 格式:ppt

- 大小:1.09 MB

- 文档页数:86

VHDL语⾔基础VHDL语⾔基础1 数据对象数据对象包括常量、变量、信号和⽂件四种类型1.1 常量常量是对某⼀常量名赋予⼀个固定的值,⽽且只能赋值⼀次。

通常赋值在程序开始前进⾏,该值的数据类型则在声明语句中指明--定义常量语句:--Constant 常数名:数据类型:=表达式Constant Vcc:real:=5.2; --指定Vcc的数据类型是实数,赋值为5.0VConstant bus_width:integer:=8; --定义总线宽度为常数8常量所赋的值应和定义的数据类型⼀致;常量在程序包、实体、构造体或进程的说明性区域必须加以说明。

定义程序包内的常量课提供所包含的任何实体、构造体所引⽤,定义在实体说明内的常量只能在该实体内可见,定义在进程说明内的常量只能在该实体内可见,定义在进程说明区域中的常量只能在该进程内可见1.2 变量变量只能在进程语句、函数语句和过程语句结构中使⽤。

变量的赋值是直接的,⾮预设的。

变量不能表达“连线”或储存原件,不能设置传输延迟量--定义变量语句--Variable 变量名:数据类型:=初始值;Variable count:integer 0 to 255:=20; --定义count整数变量,变化范围0-255,初始值为20--变量赋值语句--⽬标变量名:=表达式;x:=10.0; --实数变量赋值为10.0Y:=1.5+x; --运算表达式赋值,表达式必须与⽬标变量的数据类型相同A(3 to 6):=("1101") --位⽮量赋值1.3 信号信号表⽰逻辑门的输⼊或输出,类似于连接线,也可以表达存储元件的状态。

信号通常在构造体、程序包和实体中说明--信号定义语句--Signal 信号名:数据类型:=初始值Signal clock:bit:='0'; --定义时钟信号,初始值为0Signal count:BIT_VECTOR(3 DOWNTO 0); --定义count为4位位⽮量--信号赋值语句⽬标信号名<=表达式;x<=9;Z<=x after 5 ns; --在5ns后将x的值赋给z2 数据类型2.1 VHDL的预定义数据类型类型定义说明布尔(Boolean)TYPE BOOLEAN IS (FALSE,TRUE);取值为FALSE和TRUE,不是数值,不能运算,⼀般⽤于关系运算符位(Bit)TYPE BIT IS ('0','1');取值为0和1,⽤于逻辑运算位⽮量(Bit_Vector)TYPE BIT_VECTOR IS ARRAY(Natural range<>)OF BIT;基于Bit类型的数组,⽤于逻辑运算字符(Character)TYPE CHARACTER IS (NUL,SOH,STX,...,'','!',...);通常⽤''引号引起来,区分⼤⼩写字符串(String)VARIABLE string_var:STRING(1 TO 7);string_var:="A B C D";通常⽤""引起来,区分⼤⼩写整数(Integer)variable a:integer range -63 to 63取值范围 -(231 -1)~(231-1)要求⽤RANGE⼦句为所定义的数限定范围,以便根据范围决定此信号或变量的⼆进制位数实数(Real)-取值范围-1.0E38~+1.0E38,仅可⽤于仿真不可综合时间(Time)-物理量数据,完整的包括整数和单位两个部分,⽤⾄少⼀个空格隔开,仅可⽤于仿真不可综合时间(Time)-开,仅可⽤于仿真不可综合错误等级(SeverityLevel)TYPE severity_level IS (NOTE、WARNING、ERROR、FAILURE);表⽰系统状态,仅可⽤于仿真不可⽤于综合类型定义说明2.2 IEEE预定义标准逻辑位与⽮量标准逻辑类型对数字逻辑电路的逻辑特性描述更加完整、真实,因此在VHDL程序中,对逻辑信号的定义通常采⽤标准逻辑类型标准逻辑位(Std_Logic)符号说明'U'Undefined(未初始化)'X'Forcing Unknown(强未知)'0'Forcing 0(强0)'1'Forcing 1(强1)'Z'High Impedance(⾼阻)'W'Weak Unknown(弱未知)'L'Weak 0(弱0)'H'Weak 1(弱1)'-'Don't Care(忽略)标准逻辑位⽮量(Std_Logic_Vector)基于Std_Logic类型的数组使⽤Std_Logic和Std_Logic_Vector要调⽤IEEE库中的Std_Logic_1164程序包;就综合⽽⾔,能够在数字器件中实现的是“-、0、1、Z”四种状态。

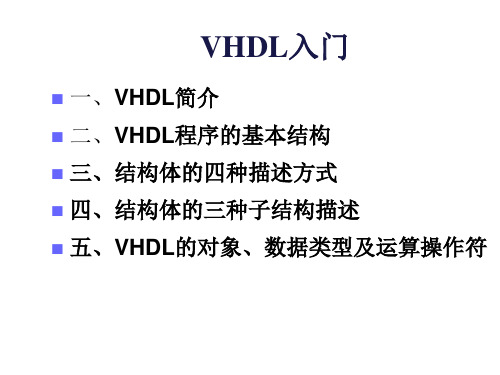

VHDL入门教程VHDL(Very High-Speed Integrated Circuit HardwareDescription Language)是一种硬件描述语言,用于设计数字电路和系统。

它是由美国国防部在20世纪80年代早期开发的,并由IEEE 1076标准化。

VHDL可以用于描述电路结构、电路行为和模拟。

一、VHDL概述VHDL是一种硬件描述语言,它允许工程师以更高级的语言编写硬件描述。

它可以描述电路结构、电路行为和模拟。

VHDL可以应用于各种电子系统的设计,从简单的数字逻辑门到复杂的处理器。

二、VHDL基本结构VHDL的基本结构包括实体声明、体声明和结构化代码。

实体声明描述了电路的接口,包括输入和输出。

主体声明描述了电路的行为。

结构化代码定义了电路的结构。

三、VHDL数据类型VHDL提供了多种数据类型,包括标量类型(比如整数和实数)、数组类型和记录类型。

每种类型都有其特定的操作和范围。

四、VHDL信号VHDL中的信号用于在电路中传递信息。

信号可以在过程中赋值,并且具有各种延迟属性。

信号还可以连接到模块的输入和输出端口,以实现电路之间的通信。

五、VHDL实体和体VHDL设计包含实体和体。

实体描述了电路的接口和连接,而体描述了电路的行为。

实体和体之间使用端口来传递信息。

六、VHDL组件VHDL中的组件用于将电路模块化,以实现更高层次的设计和复用。

组件可以在实体中声明,并在体中实例化。

七、VHDL并发语句VHDL中的并发语句用于描述电路中多个同时运行的过程。

并发语句包括并行语句、过程、并行块和并行时钟。

八、VHDL测试VHDL测试包括自动测试和手动测试。

自动测试使用测试工具和仿真器来验证电路的正确性。

手动测试包括使用仿真器进行手工测试和调试。

九、VHDL实例以下是一个简单的VHDL实例,实现了一个4位二进制加法器:```vhdllibrary IEEE;use IEEE.STD_LOGIC_1164.all;entity binary_adder isporta : in std_logic_vector(3 downto 0);b : in std_logic_vector(3 downto 0);sum : out std_logic_vector(4 downto 0);carry : out std_logicend binary_adder;architecture behavior of binary_adder isbeginprocess(a, b)variable temp_sum : std_logic_vector(4 downto 0);variable temp_carry : std_logic;begintemp_sum := ("0000" & a) + ("0000" & b);temp_carry := '0' when temp_sum(4) = '0' else '1';sum <= temp_sum;carry <= temp_carry;end process;end behavior;```上述VHDL代码定义了一个名为`binary_adder`的实体,它有两个4位输入`a`和`b`,一个5位输出`sum`和一个单一位输出`carry`。

EDA知识点汇总

一、VHDL基本概念

1、VHDL概念

VHDL(VHSIC(Very High Speed Integrated Circuit)Hardware Description Language)是用于描述硬件结构的高级语言,也是一种数字

系统设计语言,可以描述系统的逻辑结构,数据流,与特定硬件的映射实现,包括模块化,可重用,可综合和可测试特性,是精密,功能强大,拥

有仿真功能的高级硬件描述语言。

2、VHDL的作用

VHDL是一门语言,用它描述数字系统,使用它可以实现在抽象结构

与物理实现间的转换,也就是说VHDL把模型描述作为数字逻辑设计的一

部分,它把数字电路设计与电路的描述分离,实现了电路的抽象化,VHDL

作为一个设计语言,它既可以描述电路,也可以用于设计新的电路

3、VHDL的基本结构

VHDL由三部分组成,包括类型定义部分,声明部分,以及功能实现

部分;

(1)类型定义部分

类型定义部分提供了VHDL语言中的语法,包括数据类型、常量声明、变量声明、信号声明、类型定义等。

(2)声明部分

声明部分提供了用于定义数据类型和信号的描述,包括定义数据类型、变量声明、信号声明等。

(3)功能实现部分

功能实现部分描述了如何将信号和变量连接起来形成所需的逻辑功能。