TFT-Array工艺

- 格式:pptx

- 大小:726.32 KB

- 文档页数:38

名词解释:TFT阵列工序(TFT array process)从制造的角度来看液晶面板的话,可分为TFT阵列工序、液晶单元工序、液晶模块工序三类。

各工序使用专用制造装置及部件和材料。

在这些液晶面板制造工序中,尤其是TFT阵列工序和液晶单元工序决定液晶面板显示性能的重要工序。

其中,TFT阵列工序对面板制造成本的影响尤为突出。

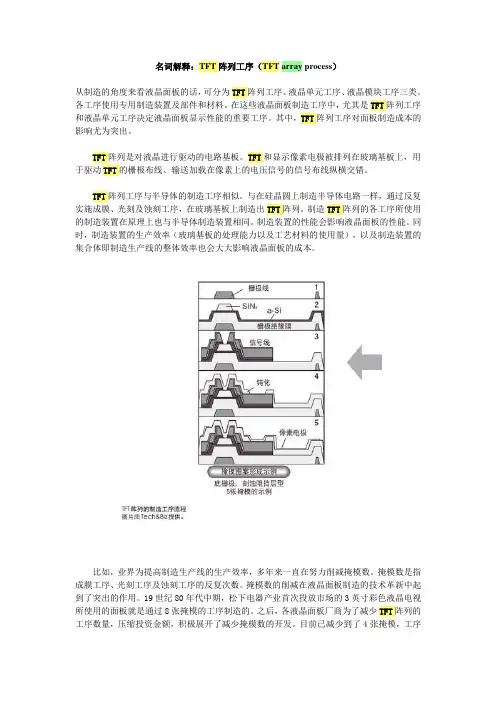

TFT阵列是对液晶进行驱动的电路基板。

TFT和显示像素电极被排列在玻璃基板上,用于驱动TFT的栅极布线、输送加载在像素上的电压信号的信号布线纵横交错。

TFT阵列工序与半导体的制造工序相似。

与在硅晶圆上制造半导体电路一样,通过反复实施成膜、光刻及蚀刻工序,在玻璃基板上制造出TFT阵列。

制造TFT阵列的各工序所使用的制造装置在原理上也与半导体制造装置相同。

制造装置的性能会影响液晶面板的性能。

同时,制造装置的生产效率(玻璃基板的处理能力以及工艺材料的使用量),以及制造装置的集合体即制造生产线的整体效率也会大大影响液晶面板的成本。

比如,业界为提高制造生产线的生产效率,多年来一直在努力削减掩模数。

掩模数是指成膜工序、光刻工序及蚀刻工序的反复次数。

掩模数的削减在液晶面板制造的技术革新中起到了突出的作用。

19世纪80年代中期,松下电器产业首次投放市场的3英寸彩色液晶电视所使用的面板就是通过8张掩模的工序制造的。

之后,各液晶面板厂商为了减少TFT阵列的工序数量,压缩投资金额,积极展开了减少掩模数的开发。

目前已减少到了4张掩模,工序数量大为减少。

另外,一直在支撑着PC用及电视用液晶面板走向大屏幕化、值得一提的技术是玻璃基板的大尺寸化。

19世纪90年代初TFT液晶面板开始量产时最初使用的是300mm×400mm左右的第一代基板,而目前已发展到了了2880mm×3130mm的第十代基板。

液晶面板尺寸一直加大的话,一块玻璃基板能够获得的面板数量就会减少,使生产效率下降。

为了对此进行弥补,就必须使玻璃基板实现大尺寸化。

TFT Array製程技術~The Technology of TFT Array Processing中小事業部產品設計總處面板設計處AR設計部isplaying your vision!isplaying your vision!E/B and E/S TFT StructureData Line &SourcePassivation SiNxGate Line Cs Line & CstGate InsulatorGlass SubstrateGate Line & CstGlass Sub.Passivation SiNxGate InsulatorData Line & SourceE/B Type TFT & Cs on Common TFT Array StructureE/S Type TFT & Cs on Gate TFT Array StructurePixel Elements isplaying your vision!isplaying your vision!5-Photo Exposure ProcessInsulatorPassivation(1)Gate Patterning (Mask 1)(2)SiN/a-Si/n+ a-Si Deposition(3)a-Si Pattering (Mask 2)(4)S/D Metal Patterning (Mask 3)(5)Back Channel Etching for B/E structure (6)Passivation Layer Coverage(7)Contact Hole/ Window Etching (Mask 4)(8)ITO Pixel Electrode Patterning (Mask 5)a-Si TFT BCE Profileisplaying your vision!From Innolux 7” 2005GE Patterning (Mask 1)isplaying your vision!GI and SE Layer Depositionisplaying your vision!Crossover CoverageActive Layerisplaying your vision!Data Line &SourceElectrode isplaying your vision!Back Channel Etching Data Line &SourceElectrodeisplaying your vision!CH Layer Deposition Passivation Layer(SiNx)isplaying your vision!Passivation Layer(SiNx)isplaying your vision!PassivationLayer (SiNx) isplaying your vision!PVD/ Sputteringisplaying your vision!Metal and AlloyGate Source/DrainAUO Mo/AlNdTi/Al/TiMoWMo/Al/MoCMO MoN/AlNd MoN/Al/MoN HANNSTAR MoWMo/AlNd/MoMo/AlNd/Mo Innolux Al/Mo Mo/Al/Mo AUO(QDI)Al/Ti Ti/Al/TiNCPT CrAlNdNMoNbCr MoNb Mo/Al/Moisplaying your vision!PECVDHeat StageSubstrateisplaying your vision!Thin Film Quality⏹理想的閘極絕緣層(Gate insulator) 性質:良好的階梯覆蓋能力(Good Step Coverage)適中的介電常數(Dielectric Constant)高崩潰電壓(High Breakdown V oltage)低薄膜應力(Low Stress)與a-Si 有良好的界面(Good interface with a-Si film)⏹理想的保護層(Passivation Layer) 性質:抗水氣能力佳(Diffusion Barrier Against Moisture)抗鹼金屬離子滲透力佳(Diffusion Barrier Against Alkali Ions)硬度佳,可承受機械性刮傷低製程溫度isplaying your vision!isplaying your vision!SiNxParticleSiNxPinholePECVDSiNx:4000A a-Si:1500A n+a-Si:300A洗淨、、a-Si/n+洗淨SPUTTERINGSD MetalGateGate a-Si / n+The Pin Holesisplaying your vision!PECVDSiNx:3000APECVD SiNx洗淨SiNxGateSiNxSiNxPinholeGate PECVD SiNx:1000ASiNxGate GateGateisplaying your vision!SiNx:4000A a-Si:1500A n+a-Si:300A PECVD 現製程SiNx:3000A一次成膜洗淨二次成膜洗淨SiNx:1000A a-Si:300A a-Si:1200A n+a-Si:300A PECVD 原製程洗淨(GI)(SE-i)(SE-n+)(SE-n+)(SE-HDR-i)(SE-LDR-i)(GI-2)(GI-1)Photolithographyisplaying your vision!P.R. CoatingSubstrate Substrateisplaying your vision!Photo ExposureSubstrate isplaying your vision!Photo StitchingSubstrate isplaying your vision!Random Shot for Stitching isplaying your vision!isplaying your vision!Scan PhotoMask MoveStage MoveSubstrateEtchingEtching Mode Dry WetEquipment Plasma Enhanced CVD Liquid TroughEtching Rate Slow FastUniformity Good NormalThin Film A-Si, SiNx, Mo Al, Mo, Cr, ITOEtchant HCl, SF6, CF6HCl, HNO3, CH3OOH Etch Profile Non-isotropic IsotropicTaper Etch Vertical(ex.80~90)Slope(ex.20~45) Cost Expensive Cheap isplaying your vision!isplaying your vision!1.斷面形狀(Taper )Taper 係指蝕刻後的斷面傾斜度,是蝕刻製程中相當重要的要求,與後續沉積之薄膜覆蓋性有相當密切的關係。

1.阵列制程(array)1)一片表面光滑,没有任何杂质的玻璃,是制造TFT玻璃基板最主要的原料.在制作之前,需用特殊的冼净液,将玻璃洗得干干净净,然后脱水,甩干.2)要使玻璃基板镀上金属薄膜,需先将金属材料放在真空室内,让金属上面的特殊气体产生电浆后,金属上的原子就会被撞向玻璃,然后就形成一层层的金属薄膜了.3)镀完金属膜后,我们还要镀上一层不导电层与半导电层,在真空室内,先将玻璃板加温,然后由高压电的喷洒器喷洒特殊气体,让电子与气体产生电浆,经过化学反应后,玻璃上就形成了不导电层与半导体层。

4)薄膜形成后,我们要在玻璃上制作电晶体的图案。

首先,要进入黄光室喷上感光极强的光阻液,然后套上光罩照射蓝紫光进行曝光,最后送到显影区喷洒显影液,这样可以去除照光后的光阻,还可以让光阻层定型哦。

5)光阻定型后,我们可用蚀刻进行湿式蚀刻,将没有用的薄膜露出,也可用电浆的化学反应进行干式蚀刻,蚀刻后再将留下的光阻以溜液去除,最后就产生电晶体所需要的电路图案了。

6)要形成可用的薄膜电晶体,需要重复清洗,镀膜,上光阻,曝光,显影,蚀刻,去光阻等过程,一般来说,要制造TFT-LCD,就要重复5到7次。

2.组立制程(cell)1)完成薄膜电晶体玻璃基板后,我们就要进行液晶面板的组合了,液晶面板是由电晶体玻璃基板与彩色滤光片组合而成,首先,我们要先将玻璃洗干净,再进行下一个步骤。

TFT-LCD的整个制造过程都必须在无尘室内,这样才不会有杂质在显示器里面。

2)彩色滤光片是以化学涂布的方式,在玻璃上形成红、绿、蓝的颜色,整齐排列后再覆盖一层会导电的薄膜即完成。

3)在整个组合的过程中,首先我们要为布满电晶体的玻璃和彩色滤光片涂上一层化学薄膜,然后再进行配向的动作。

4)在组合二片玻璃板之前,我们要先平均布满类似球状的隙子固定间隔,以免液晶面板组合后,二片玻璃向内凹曲。

通常液晶面板在组合时,会留下一个或二个缺口,以利后续灌入液晶,接着就以框胶及导电胶封在二片玻璃边缘,如此就完成玻璃的组合了。

专利名称:TFT液晶显示器ARRAY板的制备方法

专利类型:发明专利

发明人:任思雨,胡君文,郝付泼,阮文中,洪胜宝,于春崎,谢凡,何基强

申请号:CN201210255899.2

申请日:20120723

公开号:CN102738081A

公开日:

20121017

专利内容由知识产权出版社提供

摘要:本发明实施例提供一种TFT液晶显示器ARRAY板的制备方法,所述方法包括:在玻璃基板上依次形成栅极、栅极绝缘层、像素电极、源漏电极以及保护绝缘层;其中,形成所述保护绝缘层包括:形成第一薄层氮化硅;在所述第一薄层氮化硅之上形成第二层氮化硅;其中,所述第一薄层氮化硅的厚度小于所述第二层氮化硅的厚度。

本发明实施例提供的ARRAY板的制备方法能够在不更改掩膜版设计图案的情况下提高ARRAY板的透过率。

申请人:信利半导体有限公司

地址:516600 广东省汕尾市城区工业大道信利电子工业城

国籍:CN

代理机构:北京集佳知识产权代理有限公司

代理人:王宝筠

更多信息请下载全文后查看。