半导体封装过程wire bond 中 wire loop 的研究及其优化

- 格式:doc

- 大小:4.23 MB

- 文档页数:43

wirebond工艺术语介绍Wirebond工艺术语是指在集成电路封装过程中使用的一种连接技术,通过金属线将芯片与封装基座之间进行电气连接。

本文将介绍一些常见的Wirebond工艺术语。

1. Wirebond:Wirebond是指通过焊线将芯片与封装基座之间进行电气连接的过程。

这种连接方式可以实现高密度的连接,并且具有可靠性高、成本低等优点。

2. Ball bond:Ball bond是Wirebond过程中的一种常见连接方式。

它通过在芯片金属引脚和基座之间形成一个小球状焊点来实现连接。

3. Wedge bond:Wedge bond是Wirebond过程中的另一种常见连接方式。

它通过将金属线压紧在芯片金属引脚和基座之间的焊脚上来实现连接。

4. Bond pad:Bond pad是芯片上用于连接Wirebond的金属引脚的区域。

它通常是一个金属化的区域,具有良好的导电性。

5. Bonding tool:Bonding tool是用于执行Wirebond过程的工具。

它通常由超声波发生器、焊头和压力传感器等组成。

6. Loop height:Loop height是指Wirebond连接中金属线形成的弯曲部分的高度。

合适的Loop height可以保证连接的可靠性和稳定性。

7. Bonding force:Bonding force是指在Wirebond过程中施加在金属线上的力。

适当的Bonding force可以保证连接的牢固性。

8. Bonding time:Bonding time是指在Wirebond过程中施加在金属线上的时间。

适当的Bonding time可以保证焊点的质量。

9. Wire diameter:Wire diameter是指用于Wirebond连接的金属线的直径。

合适的Wire diameter可以保证连接的可靠性和稳定性。

10. Bonding temperature:Bonding temperature是指在Wirebond过程中施加在金属线上的温度。

wirebond资料(实用版)目录1.Wirebond 的定义和作用2.Wirebond 的种类和特点3.Wirebond 的应用领域4.Wirebond 的优缺点5.Wirebond 的未来发展趋势正文一、Wirebond 的定义和作用Wirebond,又称为引线键合,是一种将半导体芯片与外部电路连接的技术。

简单来说,它是一种将微小的金属引线与芯片上的焊盘进行键合的方法,从而实现电气连接。

Wirebond 技术在半导体封装和电子产品制造中具有重要作用,它有助于提高芯片的性能、减小封装尺寸以及增强产品的可靠性。

二、Wirebond 的种类和特点根据键合材料的不同,Wirebond 技术可分为金线键合、铝线键合和铜线键合等。

这些技术各自具有以下特点:1.金线键合:金具有优良的导电性和耐腐蚀性,使得金线键合具有较高的电导率和可靠性。

但金线的成本较高,限制了其广泛应用。

2.铝线键合:铝线键合具有较低的成本,且导电性能尚可。

但铝线的耐腐蚀性较差,可能影响键合的可靠性。

3.铜线键合:铜线键合具有较高的导电性和较低的成本。

然而,铜线的耐腐蚀性较差,可能限制其在某些应用领域的发展。

三、Wirebond 的应用领域Wirebond 技术广泛应用于各种半导体封装和电子产品制造中,如:1.集成电路(IC)封装:Wirebond 技术可用于连接 IC 芯片与封装载体,实现电信号的传输。

2.光电子器件制造:Wirebond 技术可用于制造 LED、激光器等光电子器件,提高器件的性能和可靠性。

3.微电子机械系统(MEMS):Wirebond 技术可用于连接 MEMS 器件与外部电路,实现信号传输和能量传递。

四、Wirebond 的优缺点Wirebond 技术的优点包括:1.高电导率:Wirebond 技术能够实现高电导率的连接,降低电阻损耗。

2.小尺寸:Wirebond 技术可以实现微小的引线连接,有助于提高封装密度和缩小产品尺寸。

南京师范大学电气与自动化科学学院毕业设计(论文)半导体封装过程wire bond中wire loop的研究及其优化专业机电一体化班级学号22010439学生姓名刘晶炎单位指导教师储焱学校指导教师张朝晖评阅教师2005年5月30日摘要在半导体封装过程中,IC芯片与外部电路的连接一段使用金线(金线的直径非常小0.8--2.0 mils)来完成,金线wire bond过程中可以通过控制不同的参数来形成不同的loop形状,除了金线自身的物理强度特性外,不同的loop形状对外力的抵抗能力有差异,而对于wire bond来说,我们希望有一种或几种loop形状的抵抗外力性能出色,这样,不仅在半导体封装的前道,在半导体封装的后道也能提高mold过后的良品率,即有效地抑制wire sweeping, wire open.以及由wire sweeping引起的bond short.因此,我们提出对wire loop的形状进行研究,以期得到一个能够提高wire抗外力能力的途径。

对于wire loop形状的研究,可以解决:(1)金线neck broken的改善。

(2)BPT数值的升高。

(3)抗mold过程中EMC的冲击力加强。

(4)搬运过程中抗冲击力的加强。

关键词:半导体封装,金线,引线焊接,线型。

AbstractDuring the process of the semiconductor assembly, we use the Au wire to connect the peripheral circuit from the IC. (The diameter of the Au wire is very small .Usually, it’s about 0.8mil~2mil.) And during the Au wire bonding, we can get different loop types from control the different parameters. Besides the physics characteristic of the Au wire, the loop types can also affect the repellence under the outside force. For the process of the wire bond, we hope there are some good loop types so that improve the repellence under the outside force. According to this, it can improve the good device ratio after molding. It not only reduces the wire sweeping and the wire open of Au wires but also avoid the bond short cause by the wire sweeping.Therefore, we do the disquisition about the loop type for getting the way to improve the repellence under outside forces.This disquisition can solve the problem about:(1)Improve the neck broken of Au wire.(2)Heighten the BST data.(3)Enhance the resist force to EMC during the molding process.(4)Decrease the possibility of device broken when it be moved. Keyword: the semiconductor assembly, Au wire, wire bond, wire loop.目录摘要………………………………………………………………………Abstract…………………………………………………………………1 绪论……………………………………………………………………1.1本课题研究的意义………………………………………………1.2环境及实验设备简介……………………………………………1.3主要的研究工作…………………………………………………2 基础知识介绍………………………………………………………2.1wire bond的介绍及基本原理………………………………2.2wire loop 的基本参数………………………………………2.2.1 loop type(弧型)……………………………………2.2.2 LH(弧高)……………………………………………2.2.3 reverse distance(反向线弧长度) ……………………2.2.4RDA(反向线弧角度) ………………………………2.2.52nd kink(第二弯曲点) ………………………………2.2.62nd kink HT factor(第二弯曲点高度因素) …………2.6.7 span length (水平长度) ……………………………2.3 mold 的基本概念…………………………………………2.4 BPT 测试的简单介绍3 实验设备及环境条件…………………………………………3.1实验材料…………………………………………………3.2实验设备介绍……………………………………………3.2.1wire bond设备………………………………………3.2.2BPT测试仪…………………………………………3.2.3 mold设备及wire sweeping 测试设备……………3.3环境条件…………………………………………………4 实验设计及数据处理…………………………………………4.1实验设计及研究方法……………………………………4.2实验过程及数据采集……………………………………4.2.1 loop type: Q-LOOP (1)…………………………………4.2.1.1 参数………………………………………………4.2.1.2 BPT数据…4.2.1.3 wire sweeping测试数据…………………………4.2.2 loop type: Q-LOOP(2)…………………………………4.2.2.1 参数………………………………………………4.2.2.2 BPT数据…………………………………………4.2.2.3 wire sweeping测试数据…………………………4.2.3 loop type: SQUARE-LOOP(1)………………………4.2.3.1 参数………………………………………………4.2.3.2 BPT数据…………………………………………4.2.3.3 wire sweeping测试数据…………………………4.2.4 loop type: SQUARE-LOOP(2)…………………………4.2.4.1 参数………………………………………………4.2.4.2 BPT数据…………………………………………4.2.4.3 wire sweeping测试数据…………………………4.3数据处理分析及其结果…………………………………4.3.1实验数据处理………………………………………4.3.2数据分析及分析结果………………………………4.3.2.1 BPT数据分析及结果……………………………4.3.2.2 wire sweeping测试数据分析及结果……………4.3.2.3综合分析及结果…………………………………5理论计算5.1关于理论计算的说明5.2转动惯量的概念5.2.1转动惯量的定义5.2.2移轴定理5.3转动惯量条件下S弧与Q弧的比较5.3.1S弧的转动惯量5.3.2Q弧的转动惯量5.3.3 一定条件下两弧的比较计算5.4转动惯量对S弧模型的影响5.4.1S弧模型15.4.2S弧模型25.5转动惯量对Q弧模型的影响5.5.1 Q弧模型15.5.2 Q弧模型26结论绪论1.1 本课题研究的意义在现在的半导体封装中,大多在对金线的机械强度的提高在做努力,即提高原材料的机械强度,而对wire loop形状的研究还鲜有报道,即使有这方面的研究也并未正式公开的发表相关论文。

70一种涂胶封装半导体绑定金线断裂失效原因分析及改善方法甘声豹,苏华飞,宋建华(岚图汽车科技有限公司,武汉 430056)摘 要:在半导体封装工艺中,芯片键合是非常关键的一环,其中绑定是芯片键合的一种普遍方式,它用高纯度金线把芯片接口和基板接口键合,从而实现信号的传输和电气连接[1]。

然而使用过程中绑定容易出现一些故障,金线断裂是绑定常见的故障原因之一。

本文通过对一种PCBA上涂有防护胶的传感器进行不良解析,采用故障树梳理金线断裂的可能因素,结合CT扫描、金线断面SEM对比分析等方式,找出金线颈部断裂的根本原因并提出改善方法,为金线断裂分析提供了一种有效的解析方式。

关键词:涂胶封装;绑定金线断裂;故障树;CT扫描;SEM;对比分析中图分类号:U463.46 文献标志码:A 文章编号:1005-2550(2024)02-0070-05Failure Reason Analysis and Improvement Method of Bonding Gold Wire for a Semiconductor Encapsulated with Protective AdhesiveGAN Sheng-bao, SU Hua-fei, SONG Jian-hua( VOYAH Automobile Technology Co., Ltd., Wuhan 430056, China)Abstract: In semiconductor encapsulation technology, chip bonding is a crucial step, and bonding is a common method of chip bonding. It uses high-purity gold wire to bond the chip interface and substrate interface, thereby achieving signal transmission and electrical connection [1]. However, bonding is prone to some faults during use, and gold wire breakage is one of the common causes of bonding failures. This article analyzes the defects of a PCBA sensor coated with protective adhesive, uses a fault tree to sort out the possible factors of gold wire fracture, and combines CT scanning, and SEM comparative analysis of gold wire cross-section to identify the root cause of gold wire neck fracture and propose improvement methods, providing an effective analysis method for gold wire fracture analysis.Key Words: Adhesive Encapsulated; Bonding Wire Breakage; Fault Tree; CT Scanning; Sem; Comparative Analysisdoi:10.3969/j.issn.1005-2550.2024.02.012 收稿日期:2023-11-27引 言传感器是现代汽车重要的电子元器件,通过感知汽车实际情况,为车辆的控制提供关键信号。

WireBond工艺培训1. 概述WireBond工艺是一种常用于半导体封装和芯片连接的技术。

它主要通过金或铝线将芯片的引脚与相关设备连接,以实现电信号传输和电源供应。

本文档将介绍WireBond工艺的基本原理、操作步骤以及常见问题解决方法,以供工程师和操作人员参考。

2. WireBond工艺原理WireBond工艺的基本原理是采用金属线将芯片引脚与其他器件或引线连接。

其主要有两种类型:•焊线连接(Wedge Bonding):通过压焊法将金属线焊接在芯片的引脚和外部元器件之间的连接点上。

•黏结连接(Ball Bonding):先将金属线焊接在芯片上,然后通过高温和压力形成金属球,并将金属球与外部元器件连接。

WireBond工艺通常采用自动化设备进行操作,其中包括焊丝机、金属线拨线机、焊丝剪切机等。

操作人员需要熟悉设备的使用方法,以及掌握正确的工艺参数和操作技巧。

3. WireBond工艺流程WireBond工艺的基本流程如下:1.准备工作:确认所需材料和设备齐全,检查设备是否正常工作。

2.芯片连接准备:将芯片放置在夹具上,根据芯片引脚位置设置正确的工艺参数。

3.焊丝选择:根据芯片和外部器件的要求,选择合适的金属线材料和直径。

4.焊丝切割:使用焊丝剪切机将金属线切割成适当的长度。

5.焊丝拨线:使用金属线拨线机将焊丝正确地放置在芯片引脚和外部器件之间的连接点上。

6.焊接操作:根据焊丝机设定的参数,在芯片引脚和外部器件之间进行焊接。

7.检查与测试:对焊接后的连接进行目视检查和必要的电性测试,确保连接质量符合要求。

8.清理和维护:清理焊丝机和其他设备,记录工艺参数和操作记录。

4. 常见问题解决方法在WireBond工艺中,常见的问题包括焊丝断裂、焊丝位置偏移、焊接不牢固等。

以下是一些常见问题的解决方法:•焊丝断裂:检查焊丝剪切机的切割质量和参数,并确保金属线的质量符合要求。

另外,注意操作时不要过度拉扯焊丝。

半导体wire bond工艺流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!半导体 Wire Bond 工艺流程。

1. 焊盘镀层。

芯片封装技术——WireBond与FlipChip文章目录•前言•一、COB技术——Wire bond•1.Ball Bonding(球焊)•o 1.1球焊压焊头o 1.2球焊流程示意图o 1.3球焊机•2.Wedge Bonding(平焊/楔焊)•o 2.1楔焊压焊头o 2.2平焊流程示意图o 2.3平焊机•3.金属线•o 3.1金线o 3.2铝线•4.bonding技术优势•5.常见缺陷•二、Flip Chip封装技术前言裸芯片技术主要有两种形式:一种是COB技术,另一种是倒装片技术(Flip Chip)。

COB是简单的裸芯片贴装技术,但它的封装密度远不如TAB和倒片焊技术。

板上芯片(Chip On Board, COB)工艺过程首先是在基底表面用导热环氧树脂(一般用掺银颗粒的环氧树脂)覆盖硅片安放点,然后将硅片直接安放在基底表面,热处理至硅片牢固地固定在基底为止,随后再用丝焊的方法在硅片和基底之间直接建立电气连接。

Flip Chip也叫倒晶封装或者覆晶封装,是一种先进的封装技术,有别于传统的COB技术,Flip Chip技术是将芯片连接点长凸块(bump),然后将芯片翻转过来使凸块与基板(substrate)直接连接。

wire bond图一、COB技术——Wire bond1.Ball Bonding(球焊)金线通过空心夹具的毛细管穿出,然后经过电弧放电使伸出部分熔化,并在表面张力作用下成球形,然后通过夹具将球压焊到芯片的电极上,压下后作为第一个焊点,为球焊点,然后从第一个焊点抽出弯曲的金线再压焊到相应的位置上,形成第二个焊点,为平焊(楔形)焊点,然后又形成另一个新球用作于下一个的第一个球焊点。

球焊的第一个焊点为球焊点,第二个为平焊点Ball Bonding 图1.1球焊压焊头球焊选用毛细管头,一般用陶瓷或钨制成;焊点是在热(一般为100-500°C)、超声波、压力以及时间的综合作用下形成的。

qfn封装wire bongding设计规则-概述说明以及解释1.引言1.1 概述概述部分的内容将简要介绍本文所涉及的主题——qfn封装wire bongding设计规则,并对文章结构和目的进行概括说明。

概述:QFN封装是一种广泛应用于电子元件的封装形式,它具有小尺寸、低成本、良好的热传导性能等特点,已经成为现代电子设备中常见的封装选择之一。

在QFN封装中,wire bonding是一项非常关键的步骤,它涉及到在芯片和封装基座之间通过金属线进行连接。

而qfn封装wire bonding 设计规则则是指在进行wire bonding过程中,需要遵循的一系列设计准则和原则,以确保连接的可靠性和稳定性。

文章结构:本文将围绕qfn封装wire bongding设计规则展开讨论,分为三个主要部分:引言、正文和结论。

引言部分将对文章的背景和目的进行介绍,正文部分将详细阐述qfn封装wire bongding设计规则的重要性、基本原则和具体要点,结论部分将对文章进行总结,并展望未来qfn封装wire bongding设计规则的发展。

目的:本文的目的是探讨qfn封装wire bongding设计规则在电子封装领域的重要性,为相关领域的从业者和研究人员提供有关于qfn封装wire bongding设计规则的基本知识和具体要点。

通过对qfn封装wire bongding设计规则的讨论和总结,本文旨在提高电子封装领域从业者对该规则的认识和理解,以减少因设计不当而导致的不良连接和可靠性问题。

同时,本文也将展望未来qfn封装wire bongding设计规则的发展趋势,为该领域的进一步研究和应用提供参考和启示。

1.2 文章结构文章结构部分的内容可以包括以下信息:文章结构部分旨在为读者介绍本文的整体结构,使读者对文章的内容有一个清晰的了解。

本文分为引言、正文和结论三个部分。

引言部分首先概述了文章的主题和重要性,然后介绍了文章的结构和目的。

wire bonding引线键合形成机理模型-回复wire bonding引线键合是一种常见的半导体封装技术,用于将芯片与封装基板之间连接。

本文将以"wire bonding引线键合形成机理模型"为主题,从基础知识到详细步骤,逐步回答并解释这个主题。

引线键合是一种可靠的连接技术,它通过使用金属线将芯片的引脚与封装基板的引脚连接在一起。

这种连接可以传输信号和电力,同时提供机械支撑和热耦合。

在wire bonding引线键合中,金属线通常是由铝或金制成的。

它们具有优良的导电性和足够的弹性,可以承受一定的应变。

引线键合可以分为两种类型:压力键合和焊锡键合。

压力键合是通过应用机械力来实现金属线的弯曲和连接。

焊锡键合则是通过加热和融化焊锡来形成连接。

下面将逐步介绍wire bonding引线键合的形成机理模型的步骤:1. 准备工作: 引线键合之前,首先要准备好芯片和封装基板。

芯片上有许多金属引脚,而封装基板上有相应的焊盘或引脚,用来连接金属线。

此外,还需要一些工具和设备,如键线机、焊锡头等。

2. 金属线制备: 在键线机中,金属线从线盘上穿过,并通过一系列的轮式供给装置,将金属线传递到合适的位置。

引线键合中常用的金属线通常是细丝状的,直径在10-50微米之间。

3. 定位与对准: 在键线机的辅助元件的帮助下,芯片和封装基板被准确地定位和对准。

这一步非常关键,因为引线的准确性和可靠性取决于对准的精度。

4. 压力键合: 在压力键合过程中,金属线首先被压缩和弯曲,然后通过机械力压到芯片引脚和封装基板引脚上。

这种压力力量在金属线和引脚之间形成机械紧固和电接触。

5. 热焊键合: 在焊锡键合过程中,金属线首先被压缩和弯曲,然后通过焊锡头提供的热量进行焊接。

热焊加热金属线和引脚,并融化焊锡,使其形成牢固的连接。

6. 检测和质量控制: 在引线键合完成后,需要进行检测和质量控制。

这些检测可以包括接触电阻、焊点质量、焊点可靠性等方面的测试。

南京师范大学电气与自动化科学学院毕业设计(论文)半导体封装过程wire bond中wire loop的研究及其优化专业机电一体化班级学号22010439学生姓名刘晶炎单位指导教师储焱学校指导教师张朝晖评阅教师2005年5月30日摘要在半导体封装过程中,IC芯片与外部电路的连接一段使用金线(金线的直径非常小0.8--2.0 mils)来完成,金线wire bond过程中可以通过控制不同的参数来形成不同的loop形状,除了金线自身的物理强度特性外,不同的loop形状对外力的抵抗能力有差异,而对于wire bond来说,我们希望有一种或几种loop形状的抵抗外力性能出色,这样,不仅在半导体封装的前道,在半导体封装的后道也能提高mold过后的良品率,即有效地抑制wire sweeping, wire open.以及由wire sweeping引起的bond short.因此,我们提出对wire loop的形状进行研究,以期得到一个能够提高wire抗外力能力的途径。

对于wire loop形状的研究,可以解决:(1)金线neck broken的改善。

(2)BPT数值的升高。

(3)抗mold过程中EMC的冲击力加强。

(4)搬运过程中抗冲击力的加强。

关键词:半导体封装,金线,引线焊接,线型。

AbstractDuring the process of the semiconductor assembly, we use the Au wire to connect the peripheral circuit from the IC. (The diameter of the Au wire is very small .Usually, it’s about 0.8mil~2mil.) And during the Au wire bonding, we can get different loop types from control the different parameters. Besides the physics characteristic of the Au wire, the loop types can also affect the repellence under the outside force. For the process of the wire bond, we hope there are some good loop types so that improve the repellence under the outside force. According to this, it can improve the good device ratio after molding. It not only reduces the wire sweeping and the wire open of Au wires but also avoid the bond short cause by the wire sweeping.Therefore, we do the disquisition about the loop type for getting the way to improve the repellence under outside forces.This disquisition can solve the problem about:(1)Improve the neck broken of Au wire.(2)Heighten the BST data.(3)Enhance the resist force to EMC during the molding process.(4)Decrease the possibility of device broken when it be moved.Keyword: the semiconductor assembly, Au wire, wire bond, wire loop.目录摘要………………………………………………………………………Abstract …………………………………………………………………1 绪论……………………………………………………………………1.1 本课题研究的意义………………………………………………1.2环境及实验设备简介……………………………………………1.3主要的研究工作…………………………………………………2 基础知识介绍………………………………………………………2.1 wire bond的介绍及基本原理………………………………2.2 wire loop 的基本参数………………………………………2.2.1 loop type(弧型)……………………………………2.2.2 LH(弧高)……………………………………………2.2.3 reverse distance(反向线弧长度) ……………………2.2.4 RDA(反向线弧角度) ………………………………2.2.5 2nd kink(第二弯曲点) ………………………………2.2.6 2nd kink HT factor(第二弯曲点高度因素) …………2.6.7 span length (水平长度) ……………………………2.3 mold 的基本概念…………………………………………2.4 BPT 测试的简单介绍3 实验设备及环境条件…………………………………………3.1实验材料…………………………………………………3.2实验设备介绍……………………………………………3.2.1wire bond设备………………………………………3.2.2 BPT测试仪…………………………………………3.2.3 mold设备及wire sweeping 测试设备……………3.3环境条件…………………………………………………4 实验设计及数据处理…………………………………………4.1实验设计及研究方法……………………………………4.2实验过程及数据采集……………………………………4.2.1 loop type: Q-LOOP (1) …………………………………4.2.1.1 参数………………………………………………4.2.1.2 BPT数据…4.2.1.3 wire sweeping测试数据…………………………4.2.2 loop type: Q-LOOP(2) …………………………………4.2.2.1 参数………………………………………………4.2.2.2 BPT数据…………………………………………4.2.2.3 wire sweeping测试数据…………………………4.2.3 loop type: SQUARE-LOOP(1) ………………………4.2.3.1 参数………………………………………………4.2.3.2 BPT数据…………………………………………4.2.3.3 wire sweeping测试数据…………………………4.2.4 loop type: SQUARE-LOOP(2) …………………………4.2.4.1 参数………………………………………………4.2.4.2 BPT数据…………………………………………4.2.4.3 wire sweeping测试数据…………………………4.3数据处理分析及其结果…………………………………4.3.1实验数据处理………………………………………4.3.2数据分析及分析结果………………………………4.3.2.1 BPT数据分析及结果……………………………4.3.2.2 wire sweeping测试数据分析及结果……………4.3.2.3综合分析及结果…………………………………5理论计算5.1关于理论计算的说明5.2转动惯量的概念5.2.1转动惯量的定义5.2.2移轴定理5.3转动惯量条件下S弧与Q弧的比较5.3.1 S弧的转动惯量5.3.2 Q弧的转动惯量5.3.3 一定条件下两弧的比较计算5.4转动惯量对S弧模型的影响5.4.1 S弧模型15.4.2 S弧模型25.5转动惯量对Q弧模型的影响5.5.1 Q弧模型15.5.2 Q弧模型26结论绪论1.1 本课题研究的意义在现在的半导体封装中,大多在对金线的机械强度的提高在做努力,即提高原材料的机械强度,而对wire loop形状的研究还鲜有报道,即使有这方面的研究也并未正式公开的发表相关论文。

南京师范大学电气与自动化科学学院毕业设计(论文)半导体封装过程wire bond中wire loop的研究及其优化专业机电一体化班级学号 22010439学生姓名刘晶炎单位指导教师储焱学校指导教师张朝晖评阅教师2005年5月30日摘要在半导体封装过程中,IC芯片与外部电路的连接一段使用金线(金线的直径非常小0.8--2.0 mils)来完成,金线wire bond过程中可以通过控制不同的参数来形成不同的loop形状,除了金线自身的物理强度特性外,不同的loop形状对外力的抵抗能力有差异,而对于wire bond 来说,我们希望有一种或几种loop形状的抵抗外力性能出色,这样,不仅在半导体封装的前道,在半导体封装的后道也能提高mold过后的良品率,即有效地抑制wire sweeping, wire open.以及由wire sweeping引起的bond short.因此,我们提出对wire loop的形状进行研究,以期得到一个能够提高wire抗外力能力的途径。

对于wire loop形状的研究,可以解决:(1)金线neck broken的改善。

(2)BPT数值的升高。

(3)抗mold过程中EMC的冲击力加强。

(4)搬运过程中抗冲击力的加强。

关键词:半导体封装,金线,引线焊接,线型。

AbstractDuring the process of the semiconductor assembly, we use the Au wire to connect the peripheral circuit from the IC. (The diameter of the Au wire is very small .Usually, it’s about 0.8mil~2mil.) And during the Au wire bonding, we can get different loop types from control the different parameters. Besides the physics characteristic of the Au wire, the loop types can also affect the repellence under the outside force. For the process of the wire bond, we hope there are some good loop types so that improve the repellence under the outside force. According to this, it can improve the good device ratio after molding. It not only reduces the wire sweeping and the wire open of Au wires but also avoid the bond short cause by the wire sweeping.Therefore, we do the disquisition about the loop type for getting the way to improve the repellence under outside forces.This disquisition can solve the problem about:(1)Improve the neck broken of Au wire.(2)Heighten the BST data.(3)Enhance the resist force to EMC during the molding process.(4)Decrease the possibility of device broken when it be moved.Keyword: the semiconductor assembly, Au wire, wire bond, wire loop.目录摘要………………………………………………………………………Abstract…………………………………………………………………1 绪论……………………………………………………………………1.1本课题研究的意义………………………………………………1.2环境及实验设备简介……………………………………………1.3主要的研究工作…………………………………………………2 基础知识介绍………………………………………………………2.1wire bond的介绍及基本原理………………………………2.2wire loop 的基本参数………………………………………2.2.1 loop type(弧型)……………………………………2.2.2 LH(弧高)……………………………………………2.2.3 reverse distance(反向线弧长度) ……………………2.2.4 RDA(反向线弧角度) ………………………………2.2.52nd kink(第二弯曲点) ………………………………2.2.62nd kink HT factor(第二弯曲点高度因素) …………2.6.7 span length (水平长度) ……………………………2.3 mold 的基本概念…………………………………………2.4 BPT 测试的简单介绍3 实验设备及环境条件…………………………………………3.1实验材料…………………………………………………3.2实验设备介绍……………………………………………3.2.1wire bond设备………………………………………3.2.2BPT测试仪…………………………………………3.2.3 mold设备及wire sweeping 测试设备……………3.3环境条件…………………………………………………4 实验设计及数据处理…………………………………………4.1实验设计及研究方法……………………………………4.2实验过程及数据采集……………………………………4.2.1 loop type: Q-LOOP (1)…………………………………4.2.1.1 参数………………………………………………4.2.1.2 BPT数据…4.2.1.3 wire sweeping测试数据…………………………4.2.2 loop type: Q-LOOP(2)…………………………………4.2.2.1 参数………………………………………………4.2.2.2 BPT数据…………………………………………4.2.2.3 wire sweeping测试数据…………………………4.2.3 loop type: SQUARE-LOOP(1)………………………4.2.3.1 参数………………………………………………4.2.3.2 BPT数据…………………………………………4.2.3.3 wire sweeping测试数据…………………………4.2.4 loop type: SQUARE-LOOP(2)…………………………4.2.4.1 参数………………………………………………4.2.4.2 BPT数据…………………………………………4.2.4.3 wire sweeping测试数据…………………………4.3数据处理分析及其结果…………………………………4.3.1实验数据处理………………………………………4.3.2数据分析及分析结果………………………………4.3.2.1 BPT数据分析及结果……………………………4.3.2.2 wire sweeping测试数据分析及结果……………4.3.2.3综合分析及结果…………………………………5理论计算5.1关于理论计算的说明5.2转动惯量的概念5.2.1转动惯量的定义5.2.2移轴定理5.3转动惯量条件下S弧与Q弧的比较5.3.1S弧的转动惯量5.3.2Q弧的转动惯量5.3.3 一定条件下两弧的比较计算5.4转动惯量对S弧模型的影响5.4.1S弧模型15.4.2S弧模型25.5转动惯量对Q弧模型的影响5.5.1 Q弧模型15.5.2 Q弧模型26结论绪论1.1 本课题研究的意义在现在的半导体封装中,大多在对金线的机械强度的提高在做努力,即提高原材料的机械强度,而对wire loop形状的研究还鲜有报道,即使有这方面的研究也并未正式公开的发表相关论文。

Wirebond仿真1. 介绍Wirebond(线键合)是一种常用的半导体封装技术,用于连接芯片和封装基板之间的电路。

在Wirebond过程中,金线被焊接在芯片的金属焊盘和封装基板之间,以建立电气连接。

Wirebond仿真是一种通过计算机模拟Wirebond过程来预测和优化连接质量的方法。

2. Wirebond仿真的目的Wirebond仿真旨在评估Wirebond连接的性能和可靠性,以便在实际制造过程中提前发现潜在问题并进行改进。

通过仿真,可以预测Wirebond连接的电阻、电感和电容等特性,以及连接的强度和耐热性能。

这有助于提高产品的可靠性和性能,并减少制造过程中的损失和成本。

3. Wirebond仿真的方法3.1 有限元分析(FEA)有限元分析是一种常用的Wirebond仿真方法。

它将Wirebond连接建模为一个复杂的三维结构,并使用数值方法求解其力学和电学特性。

通过对材料的物理特性和连接参数的输入,可以模拟Wirebond连接在不同载荷下的行为。

FEA可以帮助设计师评估连接的强度、应力分布和变形情况,以及连接在高温环境下的稳定性。

3.2 电磁仿真电磁仿真是另一种常用的Wirebond仿真方法。

它基于Maxwell方程组和电磁场理论,通过数值求解来模拟Wirebond连接的电学特性。

电磁仿真可以预测连接的电阻、电感和电容等参数,并分析其对整个电路的影响。

这对于高频和射频应用非常重要,因为Wirebond连接的电学特性会对信号传输和功耗产生显著影响。

3.3 热仿真热仿真是用来评估Wirebond连接在高温环境下的稳定性和可靠性的方法。

它基于热传导理论和数值求解,模拟连接在不同温度下的热分布和热应力。

热仿真可以帮助设计师确定连接的耐热性能,并优化连接材料和结构,以确保连接在高温环境下的长期稳定性。

4. Wirebond仿真的优势4.1 提高产品可靠性通过Wirebond仿真,设计师可以提前评估连接的性能和可靠性,避免在实际制造过程中出现问题。

南京师范大学电气与自动化科学学院毕业设计(论文)半导体封装过程wire bond中wire loop的研究及其优化专业机电一体化班级学号22010439学生姓名刘晶炎单位指导教师储焱学校指导教师张朝晖评阅教师2005年5月30日摘要在半导体封装过程中,IC芯片与外部电路的连接一段使用金线(金线的直径非常小0.8--2.0 mils)来完成,金线wire bond过程中可以通过控制不同的参数来形成不同的loop形状,除了金线自身的物理强度特性外,不同的loop形状对外力的抵抗能力有差异,而对于wire bond来说,我们希望有一种或几种loop形状的抵抗外力性能出色,这样,不仅在半导体封装的前道,在半导体封装的后道也能提高mold过后的良品率,即有效地抑制wire sweeping, wire open.以及由wire sweeping引起的bond short.因此,我们提出对wire loop的形状进行研究,以期得到一个能够提高wire抗外力能力的途径。

对于wire loop形状的研究,可以解决:(1)金线neck broken的改善。

(2)BPT数值的升高。

(3)抗mold过程中EMC的冲击力加强。

(4)搬运过程中抗冲击力的加强。

关键词:半导体封装,金线,引线焊接,线型。

AbstractDuring the process of the semiconductor assembly, we use the Au wire to connect the peripheral circuit from the IC. (The diameter of the Au wire is very small .Usually, it’s about 0.8mil~2mil.) And during the Au wire bonding, we can get different loop types from control the different parameters. Besides the physics characteristic of the Au wire, the loop types can also affect the repellence under the outside force. For the process of the wire bond, we hope there are some good loop types so that improve the repellence under the outside force. According to this, it can improve the good device ratio after molding. It not only reduces the wire sweeping and the wire open of Au wires but also avoid the bond short cause by the wire sweeping.Therefore, we do the disquisition about the loop type for getting the way to improve the repellence under outside forces.This disquisition can solve the problem about:(1)Improve the neck broken of Au wire.(2)Heighten the BST data.(3)Enhance the resist force to EMC during the molding process.(4)Decrease the possibility of device broken when it be moved. Keyword: the semiconductor assembly, Au wire, wire bond, wire loop.目录摘要………………………………………………………………………Abstract…………………………………………………………………1 绪论……………………………………………………………………1.1本课题研究的意义………………………………………………1.2环境及实验设备简介……………………………………………1.3主要的研究工作…………………………………………………2 基础知识介绍………………………………………………………2.1wire bond的介绍及基本原理………………………………2.2wire loop 的基本参数………………………………………2.2.1 loop type(弧型)……………………………………2.2.2 LH(弧高)……………………………………………2.2.3 reverse distance(反向线弧长度) ……………………2.2.4RDA(反向线弧角度) ………………………………2.2.52nd kink(第二弯曲点) ………………………………2.2.62nd kink HT factor(第二弯曲点高度因素) …………2.6.7 span length (水平长度) ……………………………2.3 mold 的基本概念…………………………………………2.4 BPT 测试的简单介绍3 实验设备及环境条件…………………………………………3.1实验材料…………………………………………………3.2实验设备介绍……………………………………………3.2.1wire bond设备………………………………………3.2.2BPT测试仪…………………………………………3.2.3 mold设备及wire sweeping 测试设备……………3.3环境条件…………………………………………………4 实验设计及数据处理…………………………………………4.1实验设计及研究方法……………………………………4.2实验过程及数据采集……………………………………4.2.1 loop type: Q-LOOP (1)…………………………………4.2.1.1 参数………………………………………………4.2.1.2 BPT数据…4.2.1.3 wire sweeping测试数据…………………………4.2.2 loop type: Q-LOOP(2)…………………………………4.2.2.1 参数………………………………………………4.2.2.2 BPT数据…………………………………………4.2.2.3 wire sweeping测试数据…………………………4.2.3 loop type: SQUARE-LOOP(1)………………………4.2.3.1 参数………………………………………………4.2.3.2 BPT数据…………………………………………4.2.3.3 wire sweeping测试数据…………………………4.2.4 loop type: SQUARE-LOOP(2)…………………………4.2.4.1 参数………………………………………………4.2.4.2 BPT数据…………………………………………4.2.4.3 wire sweeping测试数据…………………………4.3数据处理分析及其结果…………………………………4.3.1实验数据处理………………………………………4.3.2数据分析及分析结果………………………………4.3.2.1 BPT数据分析及结果……………………………4.3.2.2 wire sweeping测试数据分析及结果……………4.3.2.3综合分析及结果…………………………………5理论计算5.1关于理论计算的说明5.2转动惯量的概念5.2.1转动惯量的定义5.2.2移轴定理5.3转动惯量条件下S弧与Q弧的比较5.3.1S弧的转动惯量5.3.2Q弧的转动惯量5.3.3 一定条件下两弧的比较计算5.4转动惯量对S弧模型的影响5.4.1S弧模型15.4.2S弧模型25.5转动惯量对Q弧模型的影响5.5.1 Q弧模型15.5.2 Q弧模型26结论绪论1.1 本课题研究的意义在现在的半导体封装中,大多在对金线的机械强度的提高在做努力,即提高原材料的机械强度,而对wire loop形状的研究还鲜有报道,即使有这方面的研究也并未正式公开的发表相关论文。

所以,在这方面的深入研究还是很有意义的。

1.2环境及实验设备简介固定一种金线(2.0mil)作为实验原材料,固定实验机器为A SM*Eagle 60 wire bonder进行实验。

(注:1mil=25.4um)1.3主要的研究工作本设计主要的研究工作是对芯片进行引线焊接所行成的各种不同线型的研究分析。

我们通过设计实验的方法将其进行优化,以提高金线承受外力的能力,并最终指导实际生产工具。

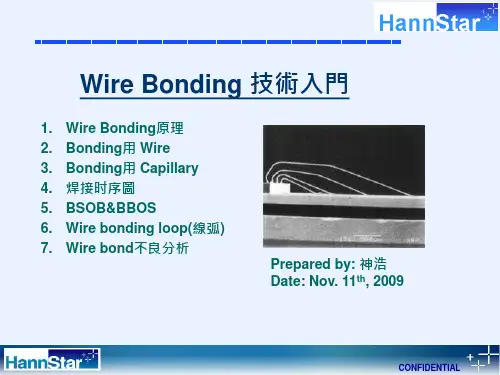

2 基础知识介绍2.1wire bond的基本原理Wire bonding是一种使用了热能、压力以及超声能量的芯片内互连技术,本质上是一种固相焊接工艺。

用金线或铝线把芯片上的焊盘与引线框架上的相应引脚连接起来,以实现芯片与外部电路连接的功能,如图2.1.1。

图2.1.1本设计中金线的wire bond采用热超声法,其将焊件加热到200~250oC,使用劈刀。

图2.1.2是wire bond-ball bonding的大致过程。

图2.1.2 W/B过程Bond过程是一个极其复杂的过程,它汇集了计算机控制技术、高精度图像识别处理技术(PRS)、高精度机械配合、自动控制反馈等高科技。

Wire bond技术的发展是围绕封装技术的发展进行的。

目前还是最成熟的芯片内互连技术。

在任何开发出的新封装类型中都可以应用WB技术。

随着技术的发展,提出了超细间距BOND技术、铜线BOND技术、带BOND 技术等新技术,也给我们带来了新的研究课题。

同时我们也应该看到,毕竟作为一种“老”技术也有不可避免的缺点如:线长带来阻抗增加和电感增大,从而限制了对高频器件封装的选择,另外散热性能也没有裸倒装芯片来得好。

不过掌握wire bond技术从而保证生产的稳定,对公司的发展来说有重要的意义。

2.2 wire loop的基本参数2.2.1 loop type(弧型):图2.2.1.1 Q-LOOP 图2.1.1.2 SQUARE-LOOP 2.2.2LH(弧高)图2.2.2 LH = loop height(弧高)2.2.3reverse distance(反向线弧长度)图2.2.3 reverse distance(反向线弧长度)2.2.4RDA(反向线弧角度)图2.2.4 RDA=reverse distance angle(反向线弧角度)2.2.52nd kink(第二弯曲点)图2.2.5 2nd Kink(第二弯曲点)2.2.62nd kink HT factor(第二弯曲点高度因素)图2.2.6 2nd kink HT factor2.2.7span length(水平长度)图2.2.7 span length (水平长度)2.3 mold的基本概念Mold就是把已经Wire-bond完成后的材料用EMC包装起来,从而达到保护Chip,使其免受外界的因素,包括热辐射、机械冲击、化学腐蚀等因素的影响、维持其本身所具有的电子性能,因而Mold工程对PKG技术的发展具有很重要的意义。