同步RS触发器电路结构、工作原理及功能表示

- 格式:docx

- 大小:116.54 KB

- 文档页数:3

rs触发器实验报告《RS触发器实验报告》摘要:本实验旨在通过搭建RS触发器电路,探究其工作原理和性能特点。

通过实验数据的收集和分析,我们得出了RS触发器的真值表和时序图,并对其稳定性和可靠性进行了评估。

实验结果表明,RS触发器在特定条件下能够实现稳定的状态转换,具有一定的应用潜力。

引言:RS触发器是数字电路中常用的一种触发器类型,它能够实现存储和传输数据的功能,广泛应用于各种数字系统中。

本实验旨在通过实际搭建电路和观察实验现象,深入理解RS触发器的工作原理和性能特点,为进一步应用和研究提供基础。

实验目的:1. 了解RS触发器的基本结构和工作原理;2. 掌握RS触发器的真值表和时序图的绘制方法;3. 评估RS触发器的稳定性和可靠性。

实验原理:RS触发器由两个交叉连接的门电路组成,其中一个门电路的输出端连接到另一个门电路的输入端,形成一个反馈环路。

当输入端的信号发生变化时,通过反馈环路的作用,触发器的输出端状态也会相应发生变化。

RS触发器有两个输入端(R和S)和两个输出端(Q和Q'),通过不同的输入信号组合可以实现不同的状态转换。

实验步骤:1. 按照实验指导书上的电路图搭建RS触发器电路;2. 分别给R和S输入端施加不同的信号组合,记录输出端的状态变化;3. 根据实验数据绘制RS触发器的真值表和时序图;4. 对实验结果进行分析和总结。

实验结果与分析:通过实验数据的收集和分析,我们得出了RS触发器的真值表和时序图。

在不同的输入信号组合下,触发器的输出状态发生了相应的变化,符合触发器的工作原理。

同时,我们还评估了触发器的稳定性和可靠性,发现在一定条件下,触发器能够实现稳定的状态转换,具有一定的应用潜力。

结论:本实验通过搭建RS触发器电路,深入探究了其工作原理和性能特点。

实验结果表明,RS触发器能够实现稳定的状态转换,具有一定的应用潜力。

通过本实验的学习,我们对数字电路中的触发器类型有了更深入的理解,为进一步的学习和研究打下了基础。

斯密特触发器斯密特触发器波形图[1]斯密特触发器又称斯密特与非门,是具有滞后特性的数字传输门。

该器件既可以像普通“与非”门那样工作,也可以接成斯密特触发器来使用。

斯密特触发器具有如下两个特点:1、电路具有两个阈值电压,分别称为正向阈值电压和负向阈值电压;2、与双稳态触发器和单稳态触发器不同,斯密特触发器属于“电平触发型”电路,不依赖于边沿陡峭的脉冲。

它是一种阈值开关电路,具有突变输入——输出特性的门电路。

这种电路被设计成阻止输入电压出现微小变化(低于某一阈值)而引起的输出电压的改变。

当输入电压由低向高增加,到达V+时,输出电压发生突变,而输入电压Vi由高变低,到达V-时,输出电压发生突变,因而出现输出电压变化滞后的现象,可以看出对于要求一定延迟启动的电路,它是特别适用的。

斯密特触发器原理图[2]而从IC内部的逻辑符号和“与非”门的逻辑符号相比就略有不同,它增加了一个类似方框的图形,该图形正是代表斯密特触发器一个重要的滞后特性。

滞后特性是指当把输入端并接成非门时,它们的输入、输出特性是:当输入电压V1上升到VT+电平时,触发器翻转,输出负跳变;过了一段时间输入电压回降到VT+电平时,输出并不回到初始状态而需输入V1继续下降到VT-电平时,输出才翻转至高电平(正跳变),用公式:VT+—VT-=△VT 表示,△VT称为斯密特触发器的滞后电压。

△VT与IC的电源电压有关,当电源电压提高时,△VT略有增加,一般△VT值在3V左右。

因斯密特触发器具有电压的滞后特性,常用它对脉冲波形整形,使波形的上升沿或下降沿变得陡直;有时还用它作电压幅度鉴别,在数字电路中它也是很常用的器件。

电路结构斯密特触发器把两个与非门G1、G2的输入、输出端交叉连接,即可构成基本RS触发器,其逻辑电路如图7.2.1.(a)所示。

它有两个输入端R、S和两个输出端Q、Q。

工作原理基本RS触发器的逻辑方程为:根据上述两个式子得到它的四种输入与输出的关系:1.当R端无效,S端有效时,则Q=0,Q=1,触发器置1。

rs主从触发器原理RS主从触发器原理引言:RS主从触发器是一种基本的数字电路元件,常用于时序电路中。

它在计算机内存中起着重要的作用,用于存储和传输数据。

本文将介绍RS主从触发器的原理及其工作方式。

一、什么是RS主从触发器RS主从触发器是由两个互补反馈的逻辑门组成的电路元件。

它由两个触发器构成,一个是主触发器,一个是从触发器。

主触发器用于存储输入信号,从触发器用于传输输出信号。

RS主从触发器可以存储一位二进制数据,并在时钟信号的控制下进行数据传输。

二、RS主从触发器的原理RS主从触发器的原理基于逻辑门的工作原理。

它由两个与非门(NOR)组成。

其中,一个与非门的输出连接到另一个与非门的输入,形成互相反馈的电路。

这种反馈机制使得RS主从触发器可以存储和传输数据。

三、RS主从触发器的工作方式1. 重置状态(Reset):当RS主从触发器的R(Reset)输入为1,S (Set)输入为0时,主触发器的输出Q为0,从触发器的输出Q'为1。

这种状态下,RS主从触发器被重置,输出为逻辑低电平。

2. 设置状态(Set):当RS主从触发器的R输入为0,S输入为1时,主触发器的输出Q为1,从触发器的输出Q'为0。

这种状态下,RS 主从触发器被设置,输出为逻辑高电平。

3. 禁用状态(Hold):当RS主从触发器的R和S输入都为0时,主触发器和从触发器的状态不变,保持之前存储的数据。

4. 非法状态(Illegal):当RS主从触发器的R和S输入都为1时,主触发器和从触发器的状态将无法确定,处于非法状态。

四、RS主从触发器的应用RS主从触发器常用于时序电路中,用于存储和传输数据。

它可以作为计数器、寄存器、状态机等电路的关键组成部分。

在计算机内存中,RS主从触发器被广泛应用,用于存储和读取数据。

五、RS主从触发器的优缺点1. 优点:RS主从触发器结构简单,易于设计和实现;可以存储一位二进制数据,并在时钟信号的控制下进行数据传输。

RS触发器编辑本段基本RS电路结构把两个与非门G1、G2的输入、输出端交叉连接,即可构成基本RS触发器,其逻辑电路如图7.2.1.(a)所示。

它有两个输入端R、S和两个输出端Q、Q非。

工作原理基本RS触发器的逻辑方程为: Q(n+1)=S+R非·Q(n)[1]约束方程:R·S=0[1]根据上述两个式子得到它的四种输入与输出的关系:1.当R端无效(0),S端有效时(1),则Q=1,Q非=0,触发器置1。

2.当R端有效(1)、S端无效时(0),则Q=0,Q非=1,触发器置0。

RS触发器(10张)如上所述,当触发器的两个输入端加入不同逻辑电平时,它的两个输出端Q和Q 非有两种互补的稳定状态。

一般规定触发器Q端的状态作为触发器的状态。

通常称触发器处于某种状态,实际是指它的Q端的状态。

Q=1、Q非=0时,称触发器处于1态,反之触发器处于0态。

S=1,R=0使触发器置1,或称置位。

因置位的决定条件是S=1,故称S 端为置1端。

R=1,S=0时,使触发器置0,或称复位。

同理,称R端为置0端或复位端。

若触发器原来为1态,欲使之变为0态,必须令R端的电平由1变0,S端的电平由0变1。

这里所加的输入信号(低电平)称为触发信号,由它们导致的转换过程称为翻转。

由于这里的触发信号是电平,因此这种触发器称为电平控制触发器。

从功能方面看,它只能在S和R的作用下置0和置1,所以又称为置0置1触发器,或称为置位复位触发器。

其逻辑符号如图7.2.1(b)所示。

由于置0或置1都是触发信号低电平有效,因此,S端和R 端都画有小圆圈。

3.当RS端均有效时,触发器状态保持不变。

触发器保持状态时,输入端都加非有效电平(高电平),需要触发翻转时,要求在某一输入端加一负脉冲,例如在S端加负脉冲使触发器置1,该脉冲信号回到高电平后,触发器仍维持1状态不变,相当于把S端某一时刻的电平信号存储起来,这体现了触发器具有记忆功能。

4.当RS端均无效时,触发器状态不确定在此条件下,两个与非门的输出端Q和Q非全为1,在两个输入信号都同时撤去(回到1)后,由于两个与非门的延迟时间无法确定,触发器的状态不能确定是1还是0,因此称这种情况为不定状态,这种情况应当避免。

rs触发器工作原理

RS触发器是一种经典的数字电路元件,它在数字系统中起着重要的作用。

在本文中,我们将详细介绍RS触发器的工作原理,以及它在数字电路中的应用。

首先,让我们来了解一下RS触发器的基本结构。

RS触发器由两个输入端R和S组成,以及两个输出端Q和Q'。

R和S分别代表复位(Reset)和设置(Set)信号。

当R为低电平(通常为0),S 为高电平(通常为1)时,触发器处于复位状态;当R为高电平,S 为低电平时,触发器处于设置状态。

在这种状态下,输出端Q和Q'的状态会发生改变。

当R和S同时为高电平时,触发器处于禁止状态,此时输出端的状态不确定。

接下来,让我们来详细了解一下RS触发器的工作原理。

当R为低电平,S为高电平时,触发器处于设置状态。

此时,输出端Q为高电平,输出端Q'为低电平。

当R为高电平,S为低电平时,触发器处于复位状态。

此时,输出端Q为低电平,输出端Q'为高电平。

在禁止状态下,无论R和S的状态如何,输出端的状态都会保持不变。

这就是RS触发器的基本工作原理。

RS触发器在数字电路中有着广泛的应用。

它常常被用来存储一个比特的信息,或者作为时序逻辑电路中的一部分。

在时序逻辑电路中,RS触发器可以用来实现状态机、寄存器等功能。

此外,RS触发器还可以被用来设计各种类型的计数器、分频器等电路。

总的来说,RS触发器是数字电路中非常重要的一个元件,它的工作原理简单清晰,应用范围广泛。

通过本文的介绍,相信读者对RS触发器的工作原理有了更深入的了解,希望本文能够对大家有所帮助。

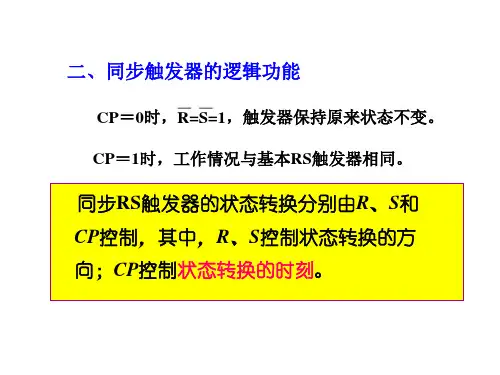

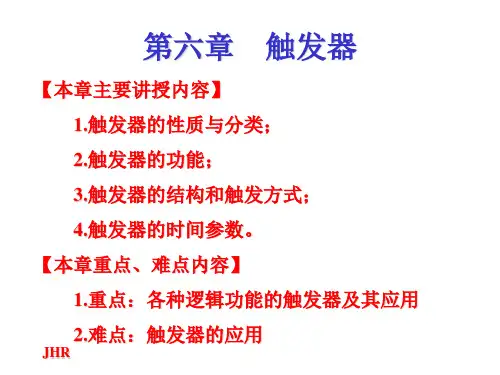

江苏省XY中等专业学校2022-2023-1教案编号:专业名称计算机应用课程名称电子线路主备教师授课教师课题:13.2 计数触发型钟控同步RS触发器及其空翻现象教学目标1.理解计数触发型钟控同步RS解发器及空翻现象2.会根据逻辑功能画波形图重点钟控同步RS触发器的逻辑功能应用难点空翻现象教法讲授法、探究法、讨论法教学设备教学平台、虚拟实验室、实验室教学环节教学活动内容及组织过程个案补充教学内容A.复习1.基本RS触发器的真值表2.同步RS触发器真值表B.引入触发器的用途之一是构成计数电路,具有计数功能。

每输入一个计数脉冲,触发器状态要改变一次,利用触发状态的改变把计数脉冲的个数记忆下来。

C.新授课13.2.1计数触发型钟控同步RS触发器一、逻辑图教学内容二、工作过程:Q n = 0:初态、原态1.S = Q = 1 R = Q = 1G3 = 1 (封)、 G4 = 0(不封——开)→Q n+1 = 1 2.S = 0 R = Q = 1G3 = 0 (开)、G4 = 1(封) →Q n+1 = 0可见,每来一个计数脉冲,触发器就翻转一次,触发器翻转的次数反映了计数脉冲的个数。

13.2.2 计数触发型钟控同步RS触发器的空翻现象1.计数触发型钟控同步触发器,必须在时钟脉冲宽度足够窄的条件下,才能正常工作。

2.分析:当tp=4tpd时,触发器将连续翻转两次。

若tp>>4tpd将多次翻转。

3.空翻现象:时钟脉冲太宽时,一个CP脉冲会引起触发器的多次翻转。

13.3防止空翻的触发器举例主从RS触发器教学内容一、电路结构1.G1~G4——同步RS触发器“从触发器”。

2.G5~G8——主触发器。

3.G9——高低电平的时钟脉冲分别控制主从触发器。

初态为0,从Q=0,主Q’=0可见:(1)从触发器状态由主触发器状态决定。

(2)主从触发器对每个输入的CP脉冲,只能翻转一次(CP下降沿翻转),在计数翻转时与CP脉冲的宽度无关,从而避免空翻。

基本RS触发器原理1 基本RS触发器的工作原理基本RS触发器的电路如图1(a)所示。

它是由两个与非门,按正反馈方式闭合而成,也可以用两个或非门按正反馈方式闭合而成。

图(b)是基本RS触发器逻辑符号。

基本RS触发器也称为闩锁(Latch)触发器。

图1 基本RS触发器电路图和逻辑符号定义A门的一个输入端为Rd 端,低电平有效,称为直接置“0”端,或直接复位端(Reset),此时Sd 端应为高电平;B门的一个输入端为Sd 端,称为直接置“1”端,或直接置位端(Set),此时Rd 端应为高电平。

我们定义一个与非门的输出端为基本RS触发器的输出端Q ,图中为B门的输出端。

另一个与非门的输出端为Q 端,这两个端头的状态应该相反。

因基本RS触发器的电路是对称的,定义A门的输出端为Q端,还是定义B门的输出端为Q端都是可以的。

一旦Q端确定,Rd和Sd 端就随之确定,再不能任意更改。

2 两个稳态这种电路结构,可以形成两个稳态,即Q =1,Q=0,Q=0,Q =1当Q=1时,Q=1和Rd =1决定了A门的输出,即Q=0 ,Q=0反馈回来又保证了Q=1 ;当Q=0时,Q=1,Q=1和Sd =1决定了B门的输出,即Q=0,Q=0又保证了Q =1 。

在没有加入触发信号之前,即Rd和Sd 端都是高电平,电路的状态不会改变。

3 触发翻转电路要改变状态必须加入触发信号,因是与非门构成的基本RS触发器,所以,触发信号是低电平有效。

若是由或非门构成的基本RS触发器,触发信号是高电平有效。

Rd和Sd 是一次信号,只能一个一个的加,即它们不能同时为低电平。

在Rd 端加低电平触发信号,Rd =0,于是Q =1 ,Q =1和Sd =1决定了Q=0 ,触发器置“0”。

Rd 是置“0”的触发器信号。

Q=0以后,反馈回来就可以替代Rd =0的作用,Rd=0就可以撤消了。

所以,Rd 不需要长时间保留,是一个触发器信号。

在Sd 端加低电平触发信号,Sd =0,于是Q =1 ,Q =1和Rd =1决定了Q=0 ,触发器置“1”。

同步RS 触发器电路结构、工作原理及功能表示

1.电路结构

主从RS 触发器是时钟触发器的一种。

由与非门构成的时钟RS 触发器电路结构如图8.9所示,CP 为时钟脉冲输入端。

1S C1S CP

Q Q

1R

R

(a)同步RS 触发器电路 (b )逻辑符号

图8.9 同步RS 触发器

2.功能分析

当CP =0时,G 3、G 4门关闭,不论R 、S 如何变化,触发器输出保持不变。

而CP =1时,R 、S 端的信号经与非门反相后引到基本RS 触发器的输入端,此时触发器输出由R 、S 及CP 决定。

S =0、R =1时,S =1、R =0,Q =1,反馈到G 1门使Q =0,即不论触发器原态是0态还是1态,电路的输出一定为0;S =1、R =0时,S =0、R =1,Q =1,反馈到G 2门使Q =0,即不论触发器原态是0态还是1态,电路的输出一定为1;S =0、R =0时,S =1、R =1,触发器的状态将保持不变。

S =1、R =1时,S =0、R =0,使Q =1、Q =1,破坏了输出信号互补的原则,而随后S =0、R =0时,输出状态可能是1也可能是0,出现了不定状态,这在触发器工作时是不允许出现的。

R 、S 控制输出状态转换,CP 控制何时发生状态转换。

时钟RS 触发器是在CP =1时发生状态转换,称为高电平触发。

3.功能表示方法 (1)功能表

时钟RS 触发器的功能表如表8.3。

其功能与基本RS 触发器功能相似,但在CP =1到

Q

& &

G 1 G

Q

S R

&

G 3

&

G 4

S

R

来时状态才能变化。

Q n 为CP 脉冲到来前触发器的状态,称为现态,Q n+1为CP 脉冲到来后触发器的状态,称为次态。

表8.3 RS 触发器的功能表

(2)特征方程

表示触发器次态与触发器输入及现态的逻辑关系式称为触发器的特征方程。

根据功能表画出卡诺图,如图8.10,经过化简,得到时钟RS 触发器在CP =1时的特征方程:

n n Q R S Q +=+1;RS =0约束条件

RS =0为约束条件,表示S 、R 不能同时为1。

图8.10 时钟RS 触发器卡诺图

(3)状态转换图

用两个圆表示触发器的两种稳态0和1。

箭头表示由现态到次态的转换方向,箭尾表示原态,箭头线上的数字标注出了原态转换成次态所需的触发条件。

如图8.11所示。

图8.11 时钟RS 触发器状态转换图

(4)波形图

触发器的功能可以通过输入输出波形表示。

图8.12为RS 触发器的波形图。

R S Q n

Q n+1

功能说明 0 0 0 0 0 1 0 1 保持 0 0 1 1 0 1 1 1 置1 1 1 0 0 0 1 0 0 置0 1 1

1 1

0 1

不定 不定

禁止

Q n

RS 0 1

10

11

00 01 0 1 × 0

1 1 × ×0

01

10

0×

1

CP

S

R

不定Q

图8.12 时钟RS触发器的波形图。