Applying Slicing Technique to Software Architectures

- 格式:pdf

- 大小:205.89 KB

- 文档页数:12

有难度的技巧英文Challenging Skill Techniques1. Advanced Data Analysis: This skill involves conducting complex statistical analyses, data mining, and using advanced software and programming languages like R or Python to extract meaningful insights from large datasets.2. Multivariable Calculus: Multivariable calculus deals with functions of more than one variable and techniques for studying them, such as partial derivatives, multiple integrals, and vector calculus. Mastering this skill enables a deeper understanding of complex mathematical models and their applications in fields like physics and economics.3. Ethical Hacking: Ethical hacking, also known as penetration testing or white-hat hacking, involves identifying vulnerabilities and weaknesses in computer systems and networks. This skill requires knowledge of various hacking techniques, network protocols, and programming languages like C++ or Python to exploit vulnerabilities safely and secure systems against cyber-attacks.4. Advanced Pilates: Pilates is a system of exercises designed to improvephysical strength, flexibility, and control. Advanced Pilates techniques include mastering complex movements like the flying squirrel, scorpion, or side crow, which require exceptional core strength, balance, and coordination.5. Fluent Public Speaking: Public speaking is a valuable skill, but becoming fluent in it takes practice and refinement. This includes techniques such as mastering persuasive language, effective body language, managing nerves, and engaging with different types of audiences.6. Advanced Chess Strategies: Chess is a game of strategy and tactics, and advanced techniques involve understanding various strategies such as positional play, sacrifices, endgame theory, and deep calculations. These skills enable players to anticipate and plan several moves ahead, making it challenging to master.7. High-Level Musical Instrument Proficiency: Mastering a musical instrument at a high level involves honing technique, sight-reading, improvisation skills, and understanding advanced musical theory and concepts. Achieving mastery often requires years of dedicated practice and study.8. Advanced Yoga Poses: Yoga comprises a range of postures, and advanced techniques involve achieving challenging poses like scorpion, handstand, or one-armed peacock. These advanced poses require exceptional balance, strength, and flexibility, making them difficult to master.9. Expert-level Programming: Becoming an expert programmer involves mastering multiple programming languages, algorithms, data structures, and software development methodologies. Advanced programming skills are essential for building complex software systems and solving intricate technical problems efficiently.10. Professional Level Cooking Techniques: Professional chefs employ advanced cooking techniques like molecular gastronomy, sous vide, or intricate knife skills to elevate their culinary creations. These skills require precise timing, attention to detail, and a deep understanding of ingredients and flavors.。

fdm打印工艺流程英文回答:FDM (Fused Deposition Modeling) is a popular 3Dprinting technology that uses a thermoplastic filament to create objects layer by layer. The process involves several steps, which I will explain in detail.1. Designing the Model:The first step in the FDM printing process is to create a 3D model using computer-aided design (CAD) software. This software allows me to design and customize the object according to my requirements. I can choose the dimensions, shape, and even add intricate details to the model.2. Slicing the Model:Once the design is complete, I need to slice the 3D model into thin layers. Slicing software is used to dividethe model into numerous horizontal layers, each with a specific thickness. This step is crucial as it determines the quality and accuracy of the final printed object.3. Preparing the Printer:Now that I have the sliced model, I need to prepare the 3D printer for the printing process. This involves several tasks such as leveling the build plate, ensuring proper filament loading, and calibrating the printer settings. These steps are essential to ensure the printer operates smoothly and produces high-quality prints.4. Printing the Object:Once the printer is ready, I can start the printing process. The 3D printer heats the thermoplastic filament to its melting point and extrudes it through a nozzle. The nozzle moves along the X, Y, and Z axes, depositing the melted filament layer by layer to create the object. The printer follows the instructions from the sliced model to determine the movement and deposition of each layer.5. Post-Processing:After the printing is complete, there are a few post-processing steps that may be required. This can include removing support structures, sanding the surface for a smoother finish, or applying additional coatings orfinishes to enhance the appearance of the printed object. These steps may vary depending on the specific requirements of the printed object.中文回答:FDM(熔融沉积建模)是一种常用的3D打印技术,它使用热塑性丝材料逐层构建物体。

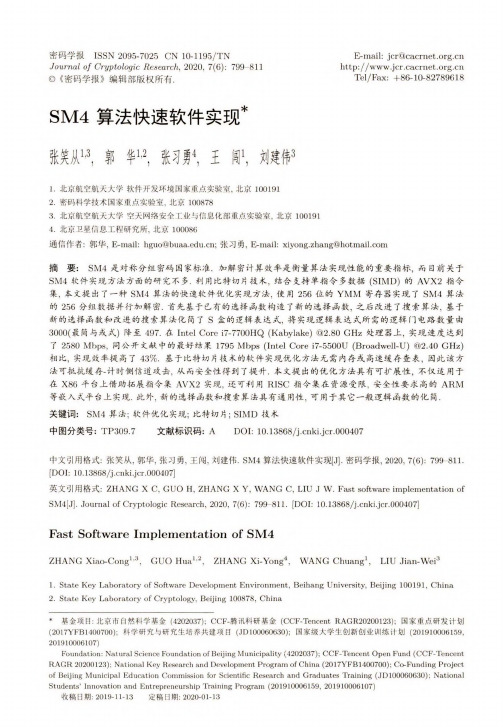

密码学报 ISSN 2095-7025 CN 10-1195/TNJournal of Cryptologic Research, 2020, 7(6): 799-811 ©《密码学报》编辑部版权所有.E-mail: ***************.cn Tel/Fax: +86-10-82789618SM4算法快速软件实现**基金项目:北京市自然科学基金(4202037); CCF-腾讯科研基金(CCF-Tencent RAGR20200123);国家重点研发计划 (2017YFB1400700);科学研究与研究生培养共建项目(JD 100060630);国家级大学生创新创业训练计划(201910006159, 201910006107)Foundation: Natural Science Foundation of Beijing Municipality (4202037); CCF-Tencent Open Fund (CCF-Tencent RAGR 20200123); National Key Research and Development Program of China (2017YFB1400700); Co-Funding Project of Beijing Municipal Education Commission for Scientific Research and Graduates Training (JD 100060630); National Students 1 Innovation and Entrepreneurship Training Program (201910006159, 201910006107)收稿日期:2019-11-13 定稿日期:2020-01-13张觌气I 华气张习肚王肌刘建伟31. 北京航空航天大学软件开发环境国家重点实验室,北京1001912. 密码科学技术国家重点实验室,北京1008783. 北京航空航天大学空天网络安全工业与信息化部重点实验室,北京1001914. 北京卫星信息工程研究所,北京100086通信作者:郭华,E-mail: *************.cn;张习勇,E-mail: ************************摘要:SM4是对称分组密码国家标准•加解密计算效率是衡量算法实现性能的重要指标,而目前关于SM4软件实现方法方面的研究不多.利用比特切片技术,结合支持单指令多数据(SIMD)的AVX2指令 集,本文提出了一种SM4算法的快速软件优化实现方法,使用256位的YMM 奇存器实现了 SM4算法的256分组数据并行加解密.首先基于已有的选择函数构造了新的选择函数,之后改进了搜索算法,基于新的选择函数和改进的搜索算法化简了 S 盒的逻辑表达式,将实现逻辑表达式所需的逻辑门电路数量由 3000(最简与或式)降至497.在Intel Core I7-7700HQ (Kabylake) @2.80 GHz 处理器上,实现速度达到了 2580 Mbps,同公开文献中的最好结果 1795 Mbps (Intel Core i7-5500U (Broadwell-U) @2.40 GHz)相比,实现效率提高了 43%.基于比特切片技术的软件实现优化方法无需内存或高速缓存查表,因此该方法可抵抗缓存-计时侧信道攻击,从而安全性得到了提升.本文提出的优化方法具有可扩展性,不仅适用于 在X86平台上借助拓展指令集AVX2实现,还可利用RISC 指令集在资源受限,安全性要求高的ARM等嵌入式平台上实现.此外,新的选择函数和搜索算法具有通用性,可用于其它一般逻辑函数的化简.关键词:SM4算法;软件优化实现;比特切片;SIMD 技术中图分类号:TP309.7 文献标识码:A DOI: 10.13868力.cnki.jcr.000407中文引用格式:张笑从,郭华,张习勇,王闯,刘建伟.SM4算法快速软件实现[J].密码学报,2020, 7(6): 799-811.[D0I : 10.13868/ki.jcr.000407]英文引用格式:ZHANG X C, GUO H, ZHANG X Y, WANG C, LIU J W. Fast software implementation ofSM4[J]. Journal of Cryptologic Research, 2020, 7(6): 799-811. [DOI: 10.13868/ki.jcr.000407]Fast Software Implementation of SM4ZHANG Xiao-Cong b3, GUO Hua b2, ZHANG Xi-Yong 4, WANG Chuang 1, LIU Jian-Wei 31. State Key Laboratory of Software Development Environment, Beihang University, Beijing 100191, China2. State Key Laboratory of Cryptology, Beijing 100878, China800Journal of Cryptologic Research密码学报Vol.7,No.6,Dec.20203. Key Laboratory of Aerospace Network Security(Ministry of Industry and Information Technology), Beihang University,Beijing100191,China4. Beijing Institute of Satellite Information Engineering,Beijing100086,ChinaCorresponding author:GUO Hua,E-mail:*************.cn;ZHANG Xi-Yong,E-mail:xiyongzhang@Abstract:The SM4algoiithm is China's national standard of symmetric block cipher,and its efficiency is one of the most important features.So far,insufficient work has been done on fast software implementation of SM4algorithm.Exploiting bit-slicing technique and SIMD(single instruction multiple data)instruction set AVX2,this paper presents a fast implementation of SM4algorithm which can process256blocks in parallel via256bits YMM registers.Firstly,a new selection function is constructed based on existing ones.Then,the logic circuit generating algorithm corresponding to the selection function is improved.Furthermore,the number of gates of the S box is reduced from3000to ing an Intel Core i7-7700HQ(Kabylake)@2.80GHz processor,the software performance is2580 Mbps,43%ahead of SM4's benchmark on software implementation which is1795Mbps(Intel Core i7-5500U(Broadwell-U)@2.40GHz).Bit-sliced implementation does not require to store a table in memory or in cache,hence it is immune to side channel attacks such as cache attack and timing attack. The improved method presented in this paper can be implemented on various computing platforms, which means that it is suitable to X86architecture with extended instruction set AVX2,and is also suitable to embedded systems with RISC instructions and limited resource.Note that the improved selection function and the improved logic circuit generating algorithm are a generic approach,which can be used to the reduction of general logical functions.Key words:SM4;software implementation:bit slicing;SIMD1引言SM4分组密码算法⑴是我国自主设计的对称分组密码,为众多信息系统提供安全、完整的数据加密方案.SM4算法的高效软件实现为我国应用在安全产品(如IPSec、VPN、SSL、TLS等)上的密码算法由国际标准替换为国家标准提供了强有力的支撑,为SM4算法广泛用于政府办公、公安、银行、税务、电力等自主可控要求高的信息系统提供了可靠的保障.目前关于SM4算法的软件优化实现方面的相关工作不多,多使用查表的方法何,但由于代替表规模相对较大,CPU在做查表操作时,表中数据在内存和cache 之间频繁对换导致查表延时较大,且不利于高效并行加/解密多组消息.此外,查表法无法抵抗缓存-计时侧信道攻击,因此在一定程度上制约了SM4的软件实现性能和安全性.1996年Intel推出单指令多数据的SSE(Streaming SIMD Extensions)指令集后,Biham同于1997年提出一种新的对称分组密码快速软件实现方法,核心思想是将处理器视为以1比特为单位的单指令多数据处理器,随后被Matthew Kwan称为比特切片(bit slicing)⑷.比特切片方法在64位平台上实现了64组DES消息的并行加解密,将逻辑门个数从理论上需要的132个每比特输出优化到10()个每比特输岀.之后研究者们对门函数个数进一步进行了优化,使得标准逻辑门(与、或、非、异或)和非标准逻辑门均达到了平均50+个每比特输出.2011年Roman Rusakov同又将门函数的个数降至平均44个逻辑门每比特输岀.比特切片方法可大大提高实现效率,也可用于搜索密钥,对RISC和CISC的指令集平台均适用,且具有更好的安全性.为了提高软件实现速度,国内外许多学者尝试将采用SIMD(Single Instruction Multiple Dada,单指令多数据)技术用于密码算法的软件实现.A.Adomnicai和T.Peyrin何给出改进的比特切片方法“Fixslicing”,在ARM和RISC-V平台实现了AES.2012年Intel推出高级向量指令集(Advanced Vector Extensions,AVX)后,众多学者开始研究如何利用AVX指令集加速对称分组密码算法的实现速度,尤其是轻量级密码算法的实现速度.Seiichi Matsuda和Shiho Moriai卩】利用AVX指令集加速切片实现,给张笑从等:SM4算法快速软件实现801出了轻量级密码算法面向云端的实现,将SSE指令与比特切片方法结合并应用到PRESENT/Piccolo,使两者的实现吞吐量分别达到4.3cycle/byte和4.57cycle/byte.2013年,Neves和Aumasson同将AVX2指令应用到SHA-3候选算法BLAKE上并提高了其实现性能.最近,郎欢等何利用X86架构下的SIMD 指令给出了高效的SM4实现,他们釆用C语言调用AVX2指令接口方式实现,在并行查表的基础上,给出了两种不同的方法.2014年Kostas Papapagiannopoulos等人口°】将比特切片方法修改为nibble切片方法,并减少了访问内存,在AVR处理器上给出了高效实现.此外,研究者们将比特切片方法和其它方法结合,对SM4算法进行软件实现,也取得了较好的效果. SM4算法公布不久,Fen Liu等【切破解了SM4算法S盒的结构,公布了S盒的代数表达式及具体参数值.之后,Hao Liang等问基于已破解的SM4中S盒结构,提出了基于复合域的SM4实现方法,将S 盒的有限域求逆运算变换到复合域中实现,并在FPGA上进行验证.Jingbin Zhang等问提出了SM4在复合域中的软件实现,使用X86架构普通指令实现,速率达到20Mbps.最近,A.Eldosouky和W. Saad")针对物联网应用的效率、安全需求改进了轻量级密码算法LED的比特切片方法,并在嵌入式处理器ARM Cortex-A53进行了实现验证.O.Hajihassani等1151利用比特切片方法进一步提高了高级加密算法AES的加解密吞吐率.总的来说,在国密标准SM4算法的软件优化实现方法取得了一些进展,但和其他对称加密算法如AES相比,SM4的软件优化实现仍需进一步研究.本文利用比特切片方法,结合支持单指令多数据(SIMD)的AVX2指令集,提出了一种SM4算法的快速软件优化实现方法,使用256位的YMM寄存器实现了SM4算法的256分组数据并行加解密.该方法首先对待加密的明文消息通过SIMD版本的数据编排算法进行预处理;之后提出了一种改进的化简逻辑表达式的新方法,将实现逻辑表达式所需的逻辑门电路数量由3000降至497;最后使用反编排算法得到密文.在Intel Core i7-7700HQ(Kabylake)@2.80GHz处理器上,结合x86平台拓展指令集AVX2和上述方法对SM4算法进行软件实现,实现速度达到了2580Mbps.相比于传统的查表实现(Intel Core i7-5500U(Broadwell-U)@2.40GHz)、未优化的比特切片实现(Intel Core i7-5500U(Broadwell-U)@2.40 GHz)、SM4软件优化实现公开文献的最佳结果[9](Intel Core i7-550()U(Broadwell-U)@2.40GHz),新方法的实现效率分别提升了 1.8倍、2.6倍和43%.综上所述,本文主要贡献如下:(1)提出了一种通用的对称分组密码算法的软件优化实现方法,该方法通用于所有对称加密算法的快速软件实现.(2)提出的基于比特切片的软件优化实现方法无需内存或高速缓存查表,因此可抵抗缓存-计时侧信道攻击"1,从而安全性得到了提升.(3)提出的优化方法具有较强的通用性.该方法可用于所有对称加密算法的软件优化实现,并适用于不同的软件架构:在CISC架构平台如X86适合借助SSE、AVX2、AVX512等拓展指令集实现,在RISC架构(ARM,RISC-V)的平台可使用普通指令集实现.(4)新的选择函数和搜索算法具有通用性,可用于一般逻辑函数的化简.本文其余内容组织如下:第2节介绍SM4算法及AVX2指令;第3节介绍新的选择函数及基于选择函数的改进的搜索算法;第4节介绍SM4的基于比特切片和AVX指令的软件优化实现方法;第5节介绍实验结果;第6节总结全文.2预备知识2.1SM4简介SM4算法釆用非平衡Feistel结构"1,分组长度和密钥长度各为128比特,解密算法与加密算法结构相同,区别在于轮密钥使用顺序相反.下面首先介绍SM4的轮函数.设明文输入为(Xo,X“X2,X3)6(Z护)4,密文输出为(Yo,m,⑹€(Z跻丫,轮密钥为rk:6Zf2, 1=0,1,••-,31.SM4加密算法的轮函数F如图1所示.轮函数F每次迭代的输入为(Xi,X,+l,X;+2,X<+3),输出为(X,+l,X,+2,X;+3,尢+4),尢+4的计算方法如下:802Journal of Cryptologic Research 密码学报 Vol.7, No.6, Dec. 2020X :+4 = F(Xi, Xi+i, Xi+2, X :+3)= X : + T(Xi+i + Xi+2 + X+3 + rki)其中,rk.为当前迭代的轮密钥,T 为一个Z/2 t Zf 的可逆变换.T 为一个Zf t Z 舁的可逆变换,由非线性变换T 和线性变换L 复合而成,即T(・)= L(r(-)).非线性变换t 由4个并行的S 盒构成.设输入为A = (ao,ai,a2,a3)€ (Z®)4,输出为B = (feo,&i,&2, &3)€ (Z 寻)4,贝!I :(6(), bi, &3)= r(A) = (Sbox(ao), Sbox(ai), Sbox(a2), Sbox@3))对于每个S 盒的8位输入,前4位作为行,后4位作为列,输岀即为查找表中对应行列所对应的值.S 盒如图2所示.D C B A 95926857E 13F 18O 48O 96A A 389A E 65D B 84C 6C F F D 8851E B A 4692O A 3497C 1B 455B C 3B 6F F 56141C 3C O 5E BF 8C 8852C 68561E 6C 89D 56O 1O 95D D F 85724E 7E 7O A F F O 61B C D 263A 9B B 7E O B 2129EC 24F 143E C 3A 741O 3644F 9B 26739F 9 49EB 45D 5E 23F 92F D 7B E 6A 3O 385C 3D O 31D 591A 388F 24A A C O 1267 73A 5A B 2255O F F D E OB C 79B 8A.5B 5627B 72D 4887A 178A AE C B 7D 3O 9E 1D D 231C 8B 774 1EF 83483746D D D 6QE B E O 765D C 36F D C 9D C A 19 313F O B 2E B 5C AC 29C F 7 69 498D B A O 3E 64 9C 2E 724E 528A CF 7F A F B 55D A 24984E 9A O C 71E 6A D 27F 17DE 951A 8O 485E 3A 397 O 7237B 4OF E 6B B 19O964B O 62O B A F D 1C 6F 6B C 478E 4A O D 5D A 9 8D 29E 461D E E 1D 8O 814 cF C 2 2 29 3 o 7 o F 33A c o 1 F6 5 D F 5图2 SM4代替表Figure 2 Substitution table in SM4 algorithm图1 SM4轮函数Figure 1 Round function in SM4 algorithm L 是线性变换,非线性变换丁的输出是线性变换L 的输入.设输入为B t Z 沪,输出为C t Z 沪,则C = L(B) = B + (£«2) + (£ « 10) + (£ « 18) + (£ « 24)其中,《代表循环左移,如E «2代表循环左移2位.2.2 SIMD 技术及AVX2指令集SIMD (single instruction multiple data)技术可实现同一操作并行处理多组数据.目前支持SIMD技术的处理器厂商主要有Intel. AMD 、ARM 等.目前大多数PC 及服务器采用的是Intel 处理器,而Intel 处理器中的SSE/AVX 指令集采用的正是SIMD 技术.AVX (Advanced Vector Extensions)指令 集1181是256-bit 宽向量指令集,指令操作对象称为YMM 的256-bit SIMD 寄存器.该寄存器内容分为2个128-bit lane. AVX 指令操作对象为lanes,该指令不支持跨越lanes 的操作.AVX2指令集是AVX 指令集的扩展和改进,也称为Haswell New Instructions,支持跨越lanes 的操作.AVX2 支持 8 道 32-bit 整数异或(vpxor)、移位(vpslld),置换(vpermd)、查表(vpgatherdd)等. 2013年Inter 在22 nm Haswell 微架构处理器上正式推出AVX2指令集.表1给出了部分AVX2指令,这些指令可用于对称分组密码的切片实现.3构造新的选择函数及搜索算法“选择函数” 119>是Mattew 为比特切片方法中简化实现S 盒逻辑门电路数量而提出的一种逻辑函数 表达形式.选择函数的思想为二分法,每次分得两个子函数,直至最终分解到的子函数可以直接实现.经研究发现,对于上述特定问题选择函数形式比其他常用的标准形式优越许多.如上所述,对于SM4算法 的S 盒,使用最简与或形式、最简或与形式、最简与或非形式等需要逻辑门数约为3000,而使用己知的3张笑从等:SM4算法快速软件实现803表1相关AVX2指令总结Table1Summary of relevant AVX2instructionsAVX2指令C/C++接口功能描述vpshufhw_mm256_shufflehi_ep订64道64位数据重排vpshuflw_mm256_shufflelo_ep订64道64比特数据重排vpshufd_mm256_shu田e_epi328道32比特数据重排vpermq_mm256_permute4x64_epi644道64比特数据重排vpslld_mm256_slli_epi328道32比特逻辑左移vpsrld_mm256_srli_epi328道32比特逻辑右移vpxor_mm256_xor_si25625&比特逻辑异或vpor_mm256_or_si256256-比特逻辑或vpgatherdd_mm256_load_si256/_mm256_store_si2568道32比特查表vmovdqa_mm256_load_si256/_nim256_store__si256加载/存储256比特数据(要求内存对齐) vmovdqu_mm256_loadu_si256/_mm256_storeu_si256加载/存储256比特数据(不要求内存对齐)个选择函数形式时,可将逻辑门数限制在:N sm4=12+8x(2'+22+---+28-2)=1032.使用本文提出的新的选择函数及改进的搜索算法,可进一步将逻辑门数减至497门.一般来说,使用的选择函数越多,搜索越充分,越能减少逻辑门数量.本节首先基于已有的选择函数构造新的选择函数、之后基于新的选择函数给出改进的搜索算法,最后 介绍如何使用新的选择函数及改进的搜索算法化简S盒的逻辑表达式.3.1选择函数简介为化简比特切片方法中实现S盒所用的逻辑门电路数量,Mattew提出了化简逻辑门电路的算法及“选择函数”的概念.使用选择函数,DES中实现S盒的逻辑门电路数量从平均70门每比特输出被约简到平均45门每比特输岀.设凡为8比特逻辑函数,即F o(abcdefgh),从输入abcdefgh中任选一个比特,记为sei,给岀选择函数基本形式:F o=(Fi and sei)or(F2and not sei)不妨设sei为d,规定:Fi=Fi(abcefgh),F2=F2(abcefgh)由于Fi与F2均唯一存在,从而8比特逻辑函数被分解成7比特逻辑函数,这一过程称为利用“选择函数”的一次选择.Mattew给出了三种“选择函数”表达式:F。

课程基本信息东北大学课程编号课程名称学期学时原课程编号英文名学分理论学时B070110100方法论①24070100581Methodology 11.520B070110110方法论②32070100582Methodology 2232B070120100信号与系统*64070100060Signals & Commu45648070100160Digital Signal 332B070120200数字信号处理基础B070120210数字信号处理*64Digital Signal 452B070120300微机原理与应用*48070300010Computer Princi340B070120400单片机原理及应用56070100120SCM Theory & Ap3.540B070120500可编程逻辑器件E48070100390Programmable Lo332B070120600嵌入式系统技术*48070100680Embedded System340B070120610嵌入式系统技术*64070100680Embedded System448B070130100生物医学电子学48070100170Biomedical Elec33264Biomedical Elec448B070130110生物医学电子学及B070130200生物医学仪器64070100200Biomedical equi432B070140100生产实习64070100540Industrial Inte464B070140200毕业实习16070100550Graduation Prac116B070140300毕业设计(论文)240070100560Graduation Desi15240B070140400电工电子实训32Electronics Pra2056070100495Design Centered3.50B070140500以项目为中心的课56070100494Design Centered3.50B070140600以项目为中心的课B070200020计算机图形学64070100220Computer Graphi432B070200040医学成像技术及系64070100231Medical Image T432B070200050数字图像处理与分64070100250Computer Image 432B070200070影像诊断学48070100661Image Diagnosis332B070200090Matlab32070100690Matlab216B070200110Mathematica语言32070100740Mathematica20B070200111Mathematica语言32070100741Mathematica216B070200120多尺度图像分析32070200141Multi-scale Ima216B070200130影像诊断学32Image Diagnosis232B070200140生产实习64070100540Industrial Prac464B070200150毕业实习16070100550Graduation Inte116B070200160毕业设计(论文)240070100560Graduation Proj15240B070200170以项目为中心的课56070100492Design Centered3.5056070100495Design Centered3.50B070200180以项目为中心的课48Computer Graphi332B070200220计算机图形学和可B070200240C++暑期实训48C++ Programming336B070200250嵌入式暑期实训64Embedded System43624070100010Introduction to1.524B070210200专业概论与职业发B070230110医学影像研究*64Study on Medica448B070300010生产实习64070100540Industrial Inte40B070300020毕业实习16070100550Graduation Inte10240070100560Graduation Proj150B070300030毕业设计(论文)B070300040以项目为中心的课56070100493Design Centered3.50B070311010人体解剖学*64070100030Human Anatomy43280070100610Human Anatomy &548B070311020人体解剖与生理学B070312010病理生理学*48070300030Pathophysiology332B070313010分子生物学32070100280Molecular Biolo220B070321010计算机引论(1)*64070100020Introduction to432B070321020高级语言程序设计64070300021Advanced Progra436B070321040java语言48070100150Java324B070321060C++程序设计*64070200010C++ Programming432B070322010数据结构*48070100720Data Structure332B070322020数据库原理*48070100410Database Princi340B070322050计算机网络48070100400Computer Networ33264070100100Assembly Langua440B070322060汇编语言程序设计B070322070软件工程48070300020Software Engine340 B070322080操作系统*48Operation Syste340 B070322090通讯与网络*48Communications 340 B070331010医学信息学32070100620Medical Informa220 B070331020医学信息学32070100260Medical Informa232 B070332010生物信息学32070100330Bioinformatics2032070100361Bioinformatics 216 B070332020生物信息与建模(B070333010项目管理16070100490Project managem116 B070333020商务管理16Business manage116 B070342010C语言程序实践32 C Programming P20 B070400021专业英语(1)32070100513Applied technic232 B070400022专业英语(2)32070100521Applied technic232 B070400041强化英语(1)48070100522Intensive Engli348 B070400042强化英语(2)48070100523Intensive Engli34856070100491Design Centered3.50 B070400050以项目为中心的课B070400060大学日语32College Japanes232 B070400070大学韩语32College Korean232 B070400080欧美文化32European & Amer23232European & Amer232 B070400090创新创业知识与技B080110180离散数学64080101251Discrete Mathem46424080101120Specialty Outli1.524 B080131130专业概论与职业发B080132180计算机引论(C语64080100021Introduciton to448 B080132250计算机编程导论40080101262Introduction to2.52448080100972Object-Oriented332 B080132360面向对象程序设计40Mainframe Datab2.532 B080132450主机数据库管理系B080133140通信概论32080100410Communication O232 B080134180电子技术基础64Fundamentals of448 B080141180数据结构64080100081Data Structure456 B080141250数据库系统40080101022Database System2.540 B080141350计算机网络40080101042Computer Networ2.540 B080141480软件工程64080101051Software Engine440 B080141550操作系统40080100200Operating Syste2.532 B080141650计算机组成原理40080100061Computer Organi2.53248080100711Software Requir348 B080142160软件需求分析与设B080142250软件测试技术40080100150Software Testin2.53216080100981User Interface 116 B080142320用户界面设计与评B080142450编译方法40080100190Compiling Metho2.532 B080143140实践考核类课程(32080101035Practice Course21632080101036Practice Course216 B080143240实践考核类课程(32080101037Practice Course216 B080143340实践考核类课程(B080143440实践考核类课程(32080101038Practice Course21640080101072Software Proces2.540 B080151150软件过程改进与项B080151250软件体系结构与设40080100741Software Archit2.532 B080151350组件技术40080100761Component Techn2.532 B080152150SOA与服务计算40080101341SOA and Service2.524 B080152250服务IT技术40080101500Service IT 2.532 B080153150电子商务概论40080100281Introduciton to2.532 B080161150C++程序设计40080100031C++ Programming2.532 B080161250C#程序设计40C# Program Desi2.532 程序设计 Program 2.532 B080162150主机系统导论40080101350Introduction to2.53240Mainframe CICS2.532 B080162350主机CICS交易系统40Mainframe Appli2.532 B080162550主机应用案例分析B080162650COBOL语言程序设40COBOL Language 2.532 B080163150多媒体技术40Multimedia Tech2.532 B080163250图像处理技术40Image Processin2.532B080171150汇编语言程序设计40080100051Assembly Langua2.53240080100321Embedded Softwa2.532 B080172150嵌入式软件开发技40080100322Embedded System2.524 B080172250嵌入式系统开发工B080172350嵌入式系统实例分40080100323Case Analysis o2.524 B080173150LINUX操作系统40080100300Linux Operating2.52424080101160Contract Law an1.524 B080181130合同法与知识产权B080182150多媒体技术40080100311Multimedia Tech2.53240Mainframe Appli2.532 B080182250主机应用开发技术40080101520Introduction to2.524 B080182350企业级服务器系统B080183120新技术讲座16080101370Seminars on New116 B080184140认证类课程32080101380Certification C23240Foundation of O2.524 B080185150ORACLE数据库基础B080185250ORACLE数据库高级40Advanced Admini2.524 B080185340形式化方法32Formal Method23240Mobile Applicat2.532 B080185450移动应用开发技术B080186140信息检索32Information Ret224 B080191140编程实践32080101205Programming Pra20 B080192140国际程序实践(一40Programming Pra2.50 B080192160程序实践(一)48080101201Programming Pra30 B080192240程序实践(二)32080101202Programming Pra20 B080192340程序实践(三)32080101203Programming Pra20 B080192440程序实践(四)32080101204Programming Pra20 B080193140课程设计32080100951Course Design2040Programming Pra2.50 B080193240国际程序实践(二B080194000企业实训208080101600Enterprise Proj130 B080195000毕业设计256080100501Graduation Desi160 B080911010Introduction to72Introduction to4.536 B080912010Introduction to48Introduction to324 B080913000Program Design,64Program Design,444 B080913010Introduction to64B080911010Introduction to432 B080914002Technical Commu48Technical Commu348 B080915010OO analysis, de64OO analysis, de424 B080921000Software Develo56Software Develo3.532 B080922010Introduction to48Introduction to324 B080931010Software Engine32Software Engine23272080100020Introduciton to4.548 B080200010计算机引论(C语言B080200020C++程序设计64080100030C++ Programming440 B080200030汇编语言程序设计56080100050Assembly Langua3.54856080100060Computer Organi3.548 B080200040计算机组成原理与B080200050算法设计与分析40080100070Algorithm Desgi2.532 B080200060数据结构80080100080Data Stucture 560 B080200070软件工程40080100090Software Engine2.540 B080200090WEB技术与应用40080100260Web Technologie2.532 程序设计40080100780Dot NET Program2.524 B080200140高级操作系统24080101170Advanced Operat1.524 B080200150嵌入式软件开发技40080101301Embedded Softwa2.53264080200010Mathematics for464 B080200160信息安全数学基础B080200170通信原理80080200030Communication P580 B080200180现代密码学与加解64080200050Modern Cryptolo44840080200100Security Techno2.532 B080200220数据通信安全技术B080200230PKI原理与技术40080200110PKI Principles 2.540 B080200240入侵检测技术56080200130Intrusion Decti3.54032080200170Information Sec232 B080200260信息安全测评技术24080200180Computer Crimin1.524 B080200270计算机犯罪和犯罪32080200190Law and Society232 B080200280信息安全的法律与48080200210Computer Virus 340 B080200290计算机病毒及其防B080200300信息隐藏技术40080200240Information Hid2.53224080200250Specialty Outli1.524 B080200310专业概论与职业发B080200320离散数学64080200300Discrete Mathem464 B080200340可信计算基础24080200340Introcution to 1.52464080200360The Principles 448 B080200350操作系统原理与安B080200360MFC可视化程序设40080200380MFC and Visuali2.524 B080200370Linux程序设计48080200400Linux Programmi336 B080200380数字版权管理24080200400Digital Copyrig1.524 B080200391程序实践(一)48080200614Programming Pra30 B080200392程序实践(二)48080200615Programming Pra30 B080200393程序实践(三)48080200616Programming Pra30 B080200394程序实践(四)48080200617Programming Pra30 B080200395信息安全实践(五48080200618Programming Pra30144080200630Integrated Prac9144 B080200400综合实践(实训)B080200410信息安全新技术24080200730New Technologie1.524 B080200420安全性程序设计40080200740Security Progra2.540 B080200430数学建模40080200750Mathematical Mo2.53032E-Commerce and 232 B080200440电子商务及安全技48Database System340 B080200450数据库系统及安全B080200460网络安全48Network Securit340 B080200470计算机网络56Computer Networ3.548 B080200480接口与通信技术40Interface and C2.532 B080200490网络管理40Network Managem2.53248Java Programmin332 B080200500JAVA语言程序设计B080200510服务器安全技术24Security Techno1.52424Next Generation1.524 B080200520新一代互联网技术B080200530创新与创业指导32Guide for Innov232 B080201003电子技术基础64Electronics Tec448 B080201013数据结构64B080200060Data Stucture456 B080201023通信原理64B080200170Communication P464 B080203003计算机组成原理与48B080200040Computer Organi340 B080203014计算机网络48B080200470Computer Networ34056B080200350The Principles 3.548 B080203024操作系统原理与安48B080200030Assembly Langua340 B080203034汇编语言程序设计56B080200180Modern Cryptolo3.544 B080203044现代密码学与加解40B080200450Database System2.532 B080203054数据库系统及安全B080203065网络安全40B080200460Network Securit2.540 B080203075网络管理32B080200170Communication P224 B080203085接口与通信技术32B080200480Interface and C22440B080200290Computer Virus 2.532 B080203096计算机病毒及其防B080203106Linux程序设计40B080200370Linux Programmi2.532 B080203117入侵检测技术48B080200240Intrusion Decti344 B080204004数据管理新技术24New Technologie1.524 B080209002计算机编程实践48B080200391Practice of Com3048B080200392Practice of Net30 B080209014网络程序设计实践B080209025密码学实践48B080200393Practice of Cry30 B080209036网络攻防实践48B080200394Practice of Net30 B080209047计算机病毒实践48B080200395Practice of Com30 B080301111大学英语(一)64080100831College English43216089900011College English016 B080301121大学英语(一)听16089900012College English00 B080301131大学英语(一)自B080301212大学英语(二)64080100832College English43216089900021College English016 B080301222大学英语(二)听16089900022College English00 B080301232大学英语(二)自B080301313大学英语(三)64080100833College English43216089900031College English016 B080301323大学英语(三)听B080301333大学英语(三)自16089900032College English00 B080301414大学英语(四)64080100834College English43216089900041College English016 B080301424大学英语(四)听16089900042College English00 B080301434大学英语(四)自B08030150强化英语口语48Intensive Engli348 B080301515大学英语(五)64080100835College English43216089900051College English016 B080301525大学英语(五)听16089900052College English00 B080301535大学英语(五)自B080301616大学英语(六)64080100836College English43216089900061College English016 B080301626大学英语(六)听16089900062College English00 B080301636大学英语(六)自B080301710IT职业英语48080101270IT Professional348 B080301717大学英语(七)64College English43216College English116 B080301727大学英语(七)听B080301737大学英语(七)自16College English116 B080301811大学英语精读(一48College English34864College English464 B080301812大学英语精读(二B080301821大学英语听力(一32College English23232College English232 B080301822大学英语听力(二32College Oral En232 B080301831大学英语口语(一32College Oral En232 B080301832大学英语口语(二B080301841报刊选读32Selected Readin232 B080302011日语(一)64080101091Japanese(Ⅰ)464 B080302012日语(二)64080101091Japanese(Ⅱ)464 B080302013日语(三)64080101091Japanese(Ⅲ)464 B080302021基础日语(一)80Basic Japanese 580 B080302022基础日语(二)80Basic Japanese 580 B080302023基础日语(三)80Basic Japanese 580 B080302024高级日语80Advanced Japane580 B080302031日语听力会话(一32Japanese listen23232Japanese listen232 B080302032日语听力会话(二32Japanese listen232 B080302033日语听力会话(三B080302034日语听力会话(四32Japanese listen232 B080302041日语写作(一)32Japanese writin232 B080302042日语写作(二)32Japanese writin232 B080302051日本简史16History of Japa116 B080303011韩语(一)64080101101Korean(I)464 B080303012韩语(二)64080101102Korean(II)464 B080303013韩语(三)64080101103Korean(III)464 B080311111大学英语(一)80College English53216College English116 B080311121大学英语(一)听B080311131大学英语(一)口32College English232 B080311212大学英语(二)80College English53216College English116 B080311222大学英语(二)听B080311232大学英语(二)口32College English232 B080311313大学英语(三)80College English53216College English116 B080311323大学英语(三)听B080311333大学英语(三)口32College English232 B080311414大学英语(四)80College English53216College English116 B080311424大学英语(四)听32College English232 B080311434大学英语(四)口B080311515大学英语(五)80College English53216College English116 B080311525大学英语(五)听32College English232 B080311535大学英语(五)口B080311616大学英语(六)80College English53216College English116 B080311626大学英语(六)听B080311636大学英语(六)口32College English232 B080311717大学英语(七)80College English53216College English116 B080311727大学英语(七)听32College English232 B080311737大学英语(七)口24Introduction to1.524 B080531150专业概论与职业发64Advanced langua448 B080532150高级语言程序设计B080532250C++程序设计64C++ Programmin44064Data Structure 452 B080532350数据结构与算法设B080533150素描48Sketch348 B080533250色彩48Color34832Fundamentals of232 B080533350游戏动画美术基础64Introduction to448 B080541150数字艺术设计概论B080542150计算机系统64Computer System448 B080542250软件工程40Software Engine2.53248Multimedia Tech332 B080543150多媒体技术基础与B080543250计算机图形学64Computer Graphi448 B080543350计算机三维建模56Computer Aided 3.540 B080543450虚拟现实技术64Virtual Reality448 B080544150人机交互技术32Human-Computer 22448Webpage Design 332 B080544250网页制作脚本编程B080544350动画插件编程40Animation Plug-2.532 B080551150动画设计基础48Fundamentals o340 B080551250Flash 动画设计40Flash Animatio2.528403D Game Charact2.528 B080552150三维游戏角色设计B080552250游戏策划40Games Planning2.532 B080552350游戏场景造型40Game Scene Mode2.528 B080553150光影渲染技术40Rendering Techn2.532 B080553250数字音效与视频40Digital Audio &2.532 B080553350计算机动画创作40Creation of Com2.528 B080561150游戏设计基础48Fundamentals of34040Computer Games 2.528 B080561250计算机游戏程序设40Interactive Med2.532 B080562150互动多媒体娱乐开B080562250游戏引擎架构分析40Game Engines St2.52840Development of 2.528 B080562350移动媒体游戏开发B080563150游戏开发协作与管40Games Developme2.532 B080563250游戏人工智能40Game Artificial2.532 B080563350OpenGL 三维编程40OpenGL 3D Progr2.528 B080571150在线互动媒体技术40Online Techniqu2.52840Multi-core and 2.528 B080571250多核与并行程序设B080572150数据可视化技术40Data Visualizat2.528 B080572250数字内容管理与版40Management of D2.528 B080581150创意设计与表达32Creative Design228 B080591150素描实习32Sketch Practice232 B080591250色彩实习32Color Practice232 B080592150课程设计(一)32Course Design(Ⅰ2020 B080592250课程设计(二)32Course Design(ⅡB080593150设计实践(一)32Design Practice20 B080593250设计实践(二)32Design Practice20 B080593350设计实践(三)32Design Practice20 B080594150企业实训208Enterprise Proj13208 B080595150毕业设计256Graduation Desi16256 B080923000Web Application40Web Application2.528 B080924000Network and Int48Network and Int348 B080932000Project and Pro24Project and Pro1.524 B080933002Professional Is16Professional Is116 B080934010Software Qulity48Software Qulity348B080935010Embedded System48Embedded System348 B080936012Information Ret48Information Ret348 B080937012SOA48348 B090100010基本乐理32090100010Theory of Music232 B090100021视唱练耳㈠64090100021Sight-singing a464 B090100022视唱练耳㈡64090100022Sight-singing a464 B090100023视唱练耳㈢64090100023Sight-singing a464 B090100024视唱练耳㈣64090100024Sight-singing a464 B090100031和声学㈠32090100031HarmonyⅠ232 B090100032和声学㈡32090100032HarmonyⅡ232 B090100040艺术概论32090100040Introduction to23232090100051Musical Forms a232 B090100051曲式与作品分析㈠B090100052曲式与作品分析㈡32090100052Musical Forms a232 B090100061音乐名著欣赏㈠32090100061Appreciation of232 B090100062音乐名著欣赏㈡32090100062Appreciation of232 B090100071民间音乐㈠32090100071Folk MusicⅠ232 B090100072民间音乐㈡32090100072Folk MusicⅡ232 B090100081中国音乐史㈠32090100081History of Chin232 B090100082中国音乐史㈡32090100082History of Chin232 B090100091外国音乐史㈠32090100091History of West232 B090100092外国音乐史㈡32090100092History of West232 B090100140电脑音乐32090100140Computer Music232 B090100151即兴伴奏㈠32090100151Improvised acco232 B090100152即兴伴奏㈡32090100152Improvised acco232 B090100161自弹自唱㈠32090100161Singing with Pi232 B090100162自弹自唱㈡32090100162Singing with Pi23232090100171Professional En232 B090100171专业英语(音乐)32090100172Professional En232 B090100172专业英语(音乐)B090100180音乐表演美学32090104100Aesthetics of M232232 B090100911艺术实践㈠32090100911Art ActivitiesⅠ232 B090100912艺术实践㈡32090100912Art ActivitiesⅡ232 B090100913艺术实践㈢32090100913Art ActivitiesⅢ348 B090100914艺术实践㈣48090100914Art ActivitiesⅣB090100920毕业论文96090100920Thesis for Bach696 B090101011独奏(管弦)㈠32090101011Solo for Instru232 B090101012独奏(管弦)㈡32090101012Solo for Instru232 B090101013独奏(管弦)㈢32090101013Solo for Instru232 B090101014独奏(管弦)㈣32090101014Solo for Instru232 B090101015独奏(管弦)㈤32090101015Solo for Instru232 B090101016独奏(管弦)㈥32090101016Solo for Instru232 B090101017独奏(管弦)㈦32090101017Solo for Instru232 B090101018独奏(管弦)㈧16090101018Solo for Instru116 B090101021合奏(管弦)㈠96090101021EnsembleⅠ696 B090101022合奏(管弦)㈡96090101022EnsembleⅡ696 B090101023合奏(管弦)㈢96090101023EnsembleⅢ696 B090101024合奏(管弦)㈣96090101024EnsembleⅣ696 B090101025合奏(管弦)㈤96090101025EnsembleⅤ696 B090101026合奏(管弦)㈥96090101026EnsembleⅥ696 B090101027合奏(管弦)㈦96090101027EnsembleⅦ696 B090101031重奏(管弦)㈠32090101031Chamber MusicⅠ232 B090101032重奏(管弦)㈡32090101032Chamber MusicⅡ232 B090101033重奏(管弦)㈢32090101033Chamber MusicⅢ232 B090101034重奏(管弦)㈣32090101034Chamber MusicⅣ23232Ensemble(Orches232 B090101035重奏(管弦)(五32Ensemble(Orches232 B090101036重奏(管弦)(六8090101041Art Supervisor 0.58 B090101041艺术指导(管弦)B090101042艺术指导(管弦)8090101042Art Supervisor 0.588090101043Art Supervisor 0.58 B090101043艺术指导(管弦)8090101044Art Supervisor 0.58 B090101044艺术指导(管弦)B090101045艺术指导(管弦)8090101045Art Supervisor 0.588090101046Art Supervisor 0.58 B090101046艺术指导(管弦)8090101047Art Supervisor 0.58 B090101047艺术指导(管弦)8090101048Art Supervisor 0.58 B090101048艺术指导(管弦)B090102011独奏(键盘)㈠32090102011PianoⅠ232 B090102012独奏(键盘)㈡32090102012PianoⅡ232 B090102013独奏(键盘)㈢32090102013PianoⅢ232 B090102014独奏(键盘)㈣32090102014PianoⅣ232 B090102015独奏(键盘)㈤32090102015PianoⅤ232 B090102016独奏(键盘)㈥32090102016PianoⅥ232 B090102017独奏(键盘)㈦32090102017PianoⅦ232 B090102018独奏(键盘)㈧16090102018PianoⅧ11632090102021Art Supervisor 232 B090102021艺术指导(键盘)B090102022艺术指导(键盘)32090102022Art Supervisor 23232090102023Art Supervisor 232 B090102023艺术指导(键盘)B090102024艺术指导(键盘)32090102024Art Supervisor 23223232090102031Piano TeachingⅠB090102031教学法(键盘)㈠232 B090102032教学法(键盘)㈡32090102032Piano TeachingⅡ32090102041 Appreciation o232 B090102041钢琴艺术及名著欣32090102042 Appreciation o232 B090102042钢琴艺术及名著欣32090102051Piano Literatur232 B090102051钢琴文献(键盘)B090102052钢琴文献(键盘)32090102052Piano Literatur232 B090103011独奏(民乐)㈠32090103011Solo for Chines232 B090103012独奏(民乐)㈡32090103012Solo for Chines232 B090103013独奏(民乐)㈢32090103013Solo for Chines232 B090103014独奏(民乐)㈣32090103014Solo for Chines232 B090103015独奏(民乐)㈤32090103015Solo for Chines232 B090103016独奏(民乐)㈥32090103016Solo for Chines232 B090103017独奏(民乐)㈦32090103017Solo for Chines232 B090103018独奏(民乐)㈧16090103018Solo for Chines116 B090103021合奏(民乐)㈠96090103021Ensemble for Ch696 B090103022合奏(民乐)㈡96090103022Ensemble for Ch696 B090103023合奏(民乐)㈢96090103023Ensemble for Ch696 B090103024合奏(民乐)㈣96090103024Ensemble for Ch696 B090103025合奏(民乐)㈤96090103025Ensemble for Ch696 B090103026合奏(民乐)㈥96090103026Ensemble for Ch696 B090103027合奏(民乐)㈦96090103027Ensemble for Ch696 B090103031重奏(民乐)㈠32090103031Chamber Music f232 B090103032重奏(民乐)㈡32090103032Chamber Music f232 B090103033重奏(民乐)㈢32090103033Chamber Music f232 B090103034重奏(民乐)㈣32090103034Chamber Music f232 B090103041弹拨乐小合奏㈠32090103041Ensemble for Ch232 B090103042弹拨乐小合奏㈡32090103042Ensemble for Ch232 B090103043弹拨乐小合奏㈢32090103043Ensemble for Ch232 B090103044弹拨乐小合奏㈣32090103044Ensemble for Ch232 B090103051广东音乐㈠32090103051Cantonese Music232 B090103052广东音乐㈡32090103052Cantonese Music232 B090104011独唱(声乐)㈠32090104011VocalⅠ232 B090104012独唱(声乐)㈡32090104012VocalⅡ232 B090104013独唱(声乐)㈢32090104013VocalⅢ232 B090104014独唱(声乐)㈣32090104014VocalⅣ232 B090104015独唱(声乐)㈤32090104015VocalⅤ232 B090104016独唱(声乐)㈥32090104016VocalⅥ232B090104017独唱(声乐)㈦32090104017VocalⅦ232 B090104018独唱(声乐)㈧16090104018VocalⅧ21632090104021FigureⅠ232 B090104021形体课(声乐)㈠32090104022FigureⅡ232 B090104022形体课(声乐)㈡16090104031PianoⅠ116 B090104031钢琴副科(声乐)16090104032PianoⅡ116 B090104032钢琴副科(声乐)16090104033PianoⅢ116 B090104033钢琴副科(声乐)16090104034PianoⅣ116 B090104034钢琴副科(声乐)B090104040意大利语语音(美32090104040Pronunciation o232 B090104051合唱(声乐)㈠32090104051ChorusⅠ232 B090104052合唱(声乐)㈡32090104052ChorusⅡ232 B090104053合唱(声乐)㈢32090104053ChorusⅢ232 B090104054合唱(声乐)㈣32090104054ChorusⅣ23232090104061PerformanceⅠ232 B090104061表演课(声乐)㈠32090104062PerformanceⅡ232 B090104062表演课(声乐)㈡B090104071重唱(美声)㈠32090104071EnsembleⅠ232 B090104072重唱(美声)㈡32090104072EnsembleⅡ232 B090104081艺术指导(声乐)8090104081Art Supervisor 0.588090104082Art Supervisor 0.58 B090104082艺术指导(声乐)8090104083Art Supervisor 0.58 B090104083艺术指导(声乐)8090104084Art Supervisor 0.58 B090104084艺术指导(声乐)8090104085Art Supervisor 0.58 B090104085艺术指导(声乐)8090104086Art Supervisor 0.58 B090104086艺术指导(声乐)B090104087艺术指导(声乐)8090104087Art Supervisor 0.588090104088Art Supervisor 0.58 B090104088艺术指导(声乐)32B170602000German speech(232 B090104100德语语音(美声)B090200010专业概论与职业发24090200800Specialty Consp1.524 B090200020中国美术史32090200030Chinese Fine Ar232 B090200030西方美术史32090200040Western Fine Ar232 B090200040现代设计简史*32090200370The General His232 B090200050设计艺术概论*32090200380Introduction to232 B090200061素描㈠56090200241Pencil Sketch㈠3.556 B090200062素描㈡48090200242Pencil Sketch㈡3483.556 B090200071色彩㈠56090200251Color Painting㈠348 B090200072色彩㈡48090200252Color Painting㈡B090200080造型基础*72090200430The Basis of Mo4.572 B090200090图形和字体基础32090200400The basis of Pa232 B090200100透视与制图*96090200390Perspective and69632Aesthetic Consp232 B090200110艺术设计美学概论B090200120创造性思维方法32Methods of Crea23232Art design and 232 B090200130艺术设计与形象思B090200140Flash及动画基础16Flash and Anima116 B090200511美术㈠96090200511Fine arts㈠696 B090200512美术㈡112090200512Fine arts㈡7112 B090200513美术(建筑学)80090200513Fine arts(Archi580 B090200520构成56090200520Composition 3.556 B090200530品牌学(平面)332090200530Brand Research(232 B090200550传统中国画赏析与32090200550Appreciation an23248090200910Landscape Sketc348 B090200910艺术实践(写生)48090200920Landscape Sketc348 B090200920艺术实践(写生)B090200931艺术实践(环艺)48090200931Artistic Practi34848090200941Artistic Practi348 B090200941艺术实践(平面)384090200971Graduation Proj24384 B090200971毕业设计(论文)B090200981毕业设计(论文)384090200981Graduation Proj24384 B090201010环境艺术摄影32Photography of 232 B090201020手绘表现技法*56Presenting Tech3.556B090201030CAD与建筑制图*32Auto CAD Drafte232 B0902010403DMAX/Photoshop723D Max and Phot4.572 B090201050室内设计史16090201260History of Inte11648Foudation and T348 B090201060室内设计基础与理B090201070建筑史16History of Arch11648Foudation and T348 B090201080建筑设计基础与理B090201090造园史16History of Gard116 B090201100景观设计基础与理48Foudation and T348 B090201110建筑技术*48090201230Building Techno34856Interior Design3.556 B090201120居住空间室内设计B090201130住区景观设计*72Landscape Desig4.572 B090201140家具与陈设设计*48Furniture and F348 B090201150装饰雕塑与配饰48Decorative Scul348 B090201160建筑及装饰材料*48090201170Architectural a348 B090201170公共空间室内设计72Interior Design4.572 B090201180园艺景观设计*56Landscape Garde3.556 B090201190建筑细部24090201400Architectural D1.524 B090201200工程概算24090201410Engineering Bud1.524 B090201210公共景观设计*56Public Landscap3.556 B090201220版式设计24090201320Layout Design1.524 B090201230展示空间设计*56090201420Design of Exhib3.55656Comprehensive E3.556 B090201240综合环境艺术设计B090202010Photoshop软件*32090202410Photoshop232 B090202020摄影基础32090200310Foundation of P232 B090202030平面设计软件*48090202011Software of Gra348 B0902020403DMAX软件320902020913D Max232 B090202050字体创意*48090202040Calligraphy Ori348 B090202060广告史32090202460Hisroty of Adve232 B090202070图形创意*48090202230Graph Originali348 B090202080标志设计*56090202070Logo Design 3.556 B090202090版式设计32090201320Layout Design232 B090202100商业摄影*56090202430Business Photog3.55648Typography and 348 B090202110印刷工艺与设计实B090202120商业插图*48090202420Illustrations f348 B090202130书籍装帧*72090202080Binding 4.57256Foudation and T3.556 B090202140包装设计基础与理72Theory of Adver4.572 B090202150广告设计理论与创B090202160系列包装设计*72090202320Design of Packi4.572 B090202170网页设计与技术*56Web Design and 3.556 B090202180平面广告设计*56Graphic Adverti3.556 B090202190品牌学*72090202130Brand Research4.572 B090202200展览设计*48090202530Design of Exhib34848Visual Inforamt348 B090202210视觉信息与传达设24100100500Generality of M1.524 B100100010工程概论与职业发B100100020工程流体力学48100100380Engineering Flu348 B100100030弹性力学56100100050Elastic Mechani3.55032100100190The Base of Com226 B100100040计算机图形学基础B100100050资源经济学24100100180Resource Econom1.52448100100022Open-pit Mining348 B100100060金属矿床露天开采B100100070凿岩爆破48100100310Drilling and Bl344 B100100080矿山岩体力学40100100510Rock Mechnics o2.540 B100100090矿山机械48100100300Machinery of Mi34832100100210SQL Server Data212 B100100100SQL Server数据库64100100021Underground Min456 B100100110金属矿床地下开采B100100120井巷工程48100100391Mining Developi348 B100100130矿井通风与安全24100100160Mine Ventilatio1.524B100100140应用岩石力学24100100090Applying Rock M1.524 B100100150采矿专业英语36100100219Scientific Engl236 B100100160计算机辅助设计32100100200Computer Aided 222 B100100170岩体测试技术32100100100Rock Measuring 228 B100100180矿用炸药原理32100100240Principle of Mi232 B100100190生态经济学24100100030Ecological Econ1.52424100100290Numerical Test 1.518 B100100200岩石破裂过程数值48100100040Production Mana348 B100100210矿山生产管理与优B100100220放矿理论24100100070Drawing Theory1.520 B100100230充填理论24100100080Filling Theory1.524 B100100240矿业新进展(双语32100100220New Development33224100100462Safety Code and1.524 B100100250矿山生产安全与法B100100260科学实验8100100410Scientific Expe0.50 B100100270特殊凿井32100100270Special Shaft D232 B100100280特殊采矿法24100100120The Specific Mi1.524 B100100290非金属矿床开发24100100150Exploitation of1.524 B100100300计算岩石力学32100100230Numerical Metho232 B100100310控制爆破32100100110Controled Blast228 B100100320无废开采24100100320Non-waste Minin1.524 B100100330数字矿山技术16100100280Digital Mining 114 B100100340矿产源综合利用32100100130Comprehensive U226 B100100350数值计算方法16100100250Numerical simul112 B100100360地下工程24100100170The Underground1.522 B100100370认识实习32100100420Cognitive Pract20 B100100380生产实习64100100440Production Prac40 B100100390上机实习32100100450Computer Operat2048100100460The course Desi30 B100100400采矿方法课程设计B100100410毕业实习16100100470Graduation Prac10 B100100420毕业设计(论文)240100100480Graduation Desi150 B100100430采矿工程概论24100100011Generality of M1.524 B100100440采选冶概论40100100340Generality of M2.54016Frontier Knowle116 B100100450学科前沿知识讲座B100100460科技文体写作16Scientific Pape116 B100100470采矿专业英语32English Literat23224Comprehensive U1.516 B100100480矿产资源综合利用B100100490弹性力学48Elastic Mechani342 B100100500资源经济学48Resource Econom348 B100100510矿山岩体力学48Rock Mechnics o348 B100100520金属矿床地下开采80Underground Min57264Open-pit Mining464 B100100530金属矿床露天开采B100100540计算机辅助设计48Computer Aided 338 B100100550生态经济与复垦32Ecological econ23264The course Desi40 B100100560采矿方法课程设计B100100570矿井通风与安全32Mine Ventilatio232 B100100580放矿理论32Drawing Theory226 B100100590充填理论32Filling Theory230 B100100600数字矿山技术32Digital Mining 230 B100100610采矿三维设计32Three-dimension224 B100300010工业通风56100300010Industry ventil3.550 B100300020安全人机工程学40100300020Safety Ergonom2.538 B100300030安全工程概论16100300030Engineering Out116 B100300040工业生产与安全56100300040Industry Produc3.556 B100300050安全原理40100300050Safety principl2.540 B100300060电气安全32100300060Electric safety232 B100300070防火防爆32100300070Fire and Explos228 B100300080压力容器安全32100300080Pressure Vessel232。

Applying Design Intent in SolidWorksSketchingSolidWorks is a powerful 3D CAD software that allows users to create and design complex models and assemblies. One of its fundamental features is the sketching tool, which enables users to create 2D profiles that can be used as a basis for creating 3D models. When sketching in SolidWorks, it is essential to apply design intent, which is a concept that ensures the sketch remains flexible and allows for easy modifications down the line. In this article, we will explore the importance of applying design intent in SolidWorks sketching and discuss various techniques to achieve it.Design intent refers to the idea that a design should capture the essential features and intentions of the final product. It involves creating sketches that are driven by dimensions, relations, and constraints to maintain their shape and behavior as they are modified. By applying design intent, designers can ensure that the sketches can be easily modified and adapted to incorporate design changes without losing their intended functionality.There are several key principles to keep in mind when applying design intent in SolidWorks sketching. First and foremost, it is crucial to define the sketch's purpose and understand how it fits into the overall design. By clearly defining the sketch's purpose, designers can make informed decisions about the dimensions, relations, and constraints needed to achieve the desired outcome.Secondly, it is essential to establish relationships and constraints within the sketch. SolidWorks provides various tools to apply relationships, such as coincident, parallel, tangent, and concentric, which help define the geometry's behavior. These relationships ensure that when modifications are made to the sketch, the desired proportions and connections are maintained.Another important aspect of applying design intent is the proper use of dimensions. Dimensions define the size and location of sketch entities and provide importantinformation for manufacturing and assembly. It is crucial to add relevant dimensions to control the sketch's overall size and proportions effectively.However, it is important not to over-constrain the sketch with excessive dimensions. Over-constrained sketches are difficult to modify and can lead to unintended consequences when making design changes. Instead, designers should focus on using fewer dimensions and leveraging relations and constraints to control the sketch's behavior.In addition to relationships and dimensions, using sketches that are parametrically driven is vital for maintaining design intent in SolidWorks. Parametric sketching allows users to define relationships and mathematical equations between sketch entities, ensuring that modifications made to one aspect of the design propagate through the entire model. This makes it easier to implement design changes throughout the development process.SolidWorks offers a range of advanced sketching tools that designers can use to maximize design intent. These tools include symmetry and pattern constraints, which ensure that changes made to a single entity propagate symmetrically or repeatedly throughout the sketch. By utilizing these advanced techniques, designers can save time and effort when modifying their sketches.Lastly, it is crucial to perform regular checks and validations throughout the sketching process to ensure that design intent has been maintained. SolidWorks provides tools such as the Fully Defined Sketch tool, which helps identify any under-defined or over-constrained sketches. By resolving these issues, designers can ensure that the sketches are flexible and easily modifiable.In conclusion, applying design intent in SolidWorks sketching is essential to create flexible and easily modifiable models. By understanding the purpose of the sketch, establishing relationships and constraints, using dimensions effectively, and leveraging parametric sketching techniques, designers can ensure that their sketches maintain their intended functionality throughout the design process. With the range of advanced sketching tools and validation options provided by SolidWorks, designers can createaccurate and efficient sketches that form the foundation for successful 3D models and assemblies.。

In the realm of international cuisine, pizza holds a special place in the hearts and palates of food enthusiasts worldwide. This versatile dish, with its crispy crust, savory sauce, gooey cheese, and myriad toppings, has become a universal symbol of culinary delight. As an avid home cook, I have embarked on a journey to master the art of crafting the perfect pizza from scratch. This essay delves into the intricate process of making pizza, examining each step in detail, while reflecting on the challenges faced, the skills honed, and the sheer joy derived from this gastronomic endeavor.**Ingredients: The Foundation of Flavor**The quality of a pizza is intrinsically linked to the freshness and authenticity of its ingredients. I begin my pizza-making odyssey by sourcing premium ingredients that meet my high standards. For the dough, I use a blend of high-protein bread flour and Italian '00' flour, which imparts a delicate texture and allows for optimal gluten development. The yeast, either active dry or instant, is carefully selected for its ability to leaven the dough effectively. Salt, sugar, and olive oil complete the dough's basic components, each contributing their unique properties –salt enhances flavor, sugar aids fermentation, and olive oil adds richness and tenderness.For the sauce, I opt for San Marzano tomatoes, renowned for their sweet, low-acidity profile and meaty texture. Fresh basil, garlic, and a pinch of sea salt create a simple yet flavorful base. Cheese selection is paramount; mozzarella, with its mild taste and excellent melting properties, serves as the foundation. I often complement it with grated Parmigiano-Reggiano for a nutty, umami boost and a sprinkle of Pecorino Romano for a sharp, salty edge.Toppings are where creativity reigns supreme. I choose a mix of fresh vegetables (such as bell peppers, mushrooms, and onions), meats (like pepperoni, sausage, or prosciutto), and herbs (basil, oregano, or rosemary) based on personal preferences and seasonal availability. The key is to strike a balance between flavors, textures, and cooking times to ensure each component reaches its optimal state during baking.**Dough Preparation: Artistry Meets Science**Making pizza dough is a delicate dance between art and science. It begins with activating the yeast in a mixture of warm water and sugar, ensuring the environment is neither too hot nor too cold to hinder or accelerate fermentation. Once frothy, the yeast is incorporated into the flour, salt, and olive oil, forming a shaggy mass. Kneading ensues – a rhythmic, meditative process that transforms the rough dough into a smooth, elastic ball.I then allow the dough to rest in a warm, draft-free area for at least an hour, or until it doubles in size. This stage, known as proofing, is crucial for developing the gluten network and infusing the dough with air pockets, which ultimately contribute to the crust's characteristic chewiness and airy texture. After proofing, the dough is gently punched down, divided, and shaped into individual balls, ready for further resting or immediate use.**Shaping and Topping: Translating Vision to Reality**Shaping the pizza dough requires both skill and patience. I prefer the Neapolitan-style, characterized by its thin, slightly puffed edges and soft center. To achieve this, I stretch the dough by hand, rotating it gently while applying outward pressure, until it forms a thin, even circle. Alternatively, I may use a rolling pin for a more uniform thickness, especially when working with a sturdier dough.Once shaped, the pizza is laid on a lightly floured peel or parchment paper, ready for its topping transformation. First comes the sauce, spread evenly but sparingly, leaving a small border for the crust. Next, a generous layer of mozzarella is scattered across the sauce, followed by the chosen toppings. Here, restraint is key – too many toppings can weigh down the crust and hinder even cooking. Finally, a sprinkle of herbs, a drizzle of olive oil, and a dusting of grated cheese complete the picture-perfect pizza.**Baking: The Crucible of Transformation**Baking pizza is where the magic truly happens. I use a preheated oven, preferably with a pizza stone or steel, to achieve a crispy, evenly cooked crust.The high heat (around 450-500°F or 230-260°C) mimics the intense heat of a traditional wood-fired oven, allowing the pizza to cook rapidly, sealing in moisture and creating those sought-after leopard spots on the crust.The pizza is slid onto the heated surface and baked for 8-12 minutes, depending on the oven and desired level of doneness. Monitoring the pizza closely during this stage is essential, as the difference between perfectly cooked and overcooked can be mere seconds. Once the crust is golden brown, the cheese melted and bubbly, and the toppings caramelized to perfection, the pizza is removed from the oven and allowed to rest for a minute or two. This resting period allows the cheese to set slightly, making slicing and serving easier.**Reflections and Learnings**My journey towards mastering pizza-making has been a gratifying blend of trial, error, and triumph. Each time I roll out the dough, I am reminded of the importance of patience, precision, and adaptability in the kitchen. I have learned to appreciate the nuances of different flours, the transformative power of fermentation, and the delicate balance between toppings. Moreover, I have discovered that the best pizzas are not just about technique or ingredients, but also about the joy of sharing a homemade meal with loved ones.Pizza-making has also taught me the value of sustainability and seasonality. By using locally sourced, organic produce and minimizing food waste, I contribute to a more eco-friendly culinary practice. Additionally, experimenting with seasonal toppings encourages creativity and fosters a deeper connection to the rhythms of nature.In conclusion, crafting the perfect pizza is a multifaceted endeavor that combines culinary expertise, artistic vision, and a deep appreciation for the transformative power of heat. From selecting high-quality ingredients to skillfully shaping the dough, thoughtfully layering toppings, and expertly baking the pie, each step is a testament to the artistry and science behind this beloved dish. As I continue to refine my pizza-making skills, I am constantly reminded that the true essence of this culinary journey lies not only in thefinal product but also in the joy of creation, the satisfaction of self-reliance, and the warmth of sharing delicious food with others.。

外文文献资料(外文文件名:JSP Splitting for Improving ExecutionPerformance)AbstractSplitting a JSP (Java Server Pages) page into fragments can improve the execution performance of JSP pages when the Web application server can separately cache the Web page fragments obtained by executing the JSP fragments. If a JSP page is split into fragments according to the update frequency of each portion of the Web page obtained by executing the JSP page, all of the split JSP fragments do not need to be executed again when only a single cached part of a Web page expires. In addition, the fragments of a JSP page can be reused by other JSP pages. In both cases, the execution results of all of the JSP fragments split from the JSP page must be the same as from the JSP page before it was split. In this paper, we propose JSP splitting, which is a method of splitting a JSP page into fragments maintaining the data and control dependences existing in the original JSP page. JSP splitting automatically detects the portions needed to maintain the data and control dependences of a JSP page for the portions that developers want to split from the JSP page. We implemented JSP splitting with a GUI tool, and confirmed that the split JSP fragments were executed in the same as the way as the JSP page before the split. Experimental results show that the response time to access a Web page can be reduced by splitting a JSP page into fragments and setting different caching periods for the Web page fragments obtained by executing the JSP fragments.1. IntroductionSplitting a JSP (Java Server Pages) page into fragments can improve the execution performance of some JSP pages when the Web application server can separately cache the Web page fragments obtained by executing the fragments of the JSP page. The period of caching dynamic Web pages generated by a JSP engineis limited due to the dynamic nature of the content. When the cached content of a Web page generated by a JSP engine is updated, the entire JSP page must be executed again on the application server, even though the change of the Web page might be small. Since frequent updates of cached Web pages increase the load on an application server, it is reasonable to split a JSP page into fragments and set different caching periods for the Web page fragments obtained by executing the JSP fragments. Of course, the Web page fragments must be merged into a final Web page correctly. The Dynacache technology of IBM WebSphere Application Server allows Web page fragments to have different caching periods. Cache tag libraries provided by the Apache Jakarta Project also support different caching periods for the JSP fragments. In addition, ESI (Edge Side Includes) technology provides a mechanism to cache Web page fragments with different caching periods, and to merge them into a final Web page on an edge server.The application offload technology of IBM WebSphere Edge Server is another approach to improve the execution performance of JSP pages. This technology allows one or more JSP fragments to be cached and executed on edge servers. The remaining JSP fragments are deployed on the application server and are called by the JSP fragments executed on the edge server. Thus, some of the execution of a JSP page is offloaded to the edge server.Splitting a JSP page facilitates the reuse of JSP fragments. When a Web application consists of many JSP pages, the same portions tend to exist in many JSP pages. Examples are the frames, the banners, the headers, and etc.When a JSP page is split into fragments, the total execution result of all of the fragments must be the same as the JSP page before it was split. In addition, when the fragments of a JSP page are executed in different servers, each fragment needs to be executed without the other fragments. In order to satisfy these conditions, we propose JSP splitting, which is the method of splitting a JSP page into fragments described in this paper. Since it is very difficult to automatically find the best way to split a JSP page into fragments for some particular purpose, we assume that the developers will select the portions that they want to split into fragments. In order to execute all of the divided JSP pages correctly, JSP splitting automatically detects any portions that must be moved or copied into a fragment with the selected portions. The detection is done based on the analysis of the data and controldependences existing in a JSP page. JSP splitting is similar to the program slicing technique that slices a program based on the data and the control dependences. However, the program slicing technique does not take into account that the sliced programs are executed independently and that the total execution result of the sliced programs must be the same as the program before the division. In addition, since data is passed to the JSP engine during the execution of JSP pages, the source program of the JSP engine, such as Apache Tomcat, is required in order to analyze the data dependences correctly. This is impractical, because the source program of the JSP engine is very large and complex. JSP splitting avoids the analysis of the JSP engine by utilizing the characteristics of JSP.The rest of the paper is organized as follows. Section 2 explains the difficulty of splitting a JSP page into fragments. Section 3 gives details of the algorithmto split a JSP page. Section 4 describes the JSP splitting tool that is an implementation of JSP splitting and demonstrates how a sample JSP page is split by the tool. Section 5 shows the experimental results obtained by executing the split JSP fragments with different caching periods on the IBM WebSphere Application Server. Section 6 discusses previous work in relation to our contributions. Our conclusions form the final section.2. Difficulty of Splitting a JSP PageIn this paper, splitting a JSP page means that some portions of the JSP page are cut from the JSP page and saved as new JSP pages. Such newly created JSP pages are included in the original JSP page by using some mechanism such as the jsp: include tag. We call the included JSP page the JSP fragment, and call the JSP page that invokes the JSP fragments the master JSP page. A master JSP page invokes JSP fragments and receives Web page fragments obtained by executing them. Then the master JSP page merges its own Web page fragment with the Web page fragments received from the JSP fragments, and creates a final Web page.JSP fragments are not always executed in the same server or at the same time. The application offload technology allows a master JSP page and JSP fragments to be executed in different servers. When the ESI mechanism is used, esi: include tags are put into a Web page fragment obtained by executing a master JSP page andinterpreted in an edge server that supports the ESI mechanism. In this case, the edge server checks whether or not the Web page fragments specified by esi:include tags exist in its cache. If the contents of Web page fragments are not cached or have expired, the JSP fragments are invoked from the edge server, and executed in one or more application servers. If different caching periods can be given to the Web page fragments obtained by executing the JSP fragments, each JSP fragment is executed only when the cached content has expired. The Dynacache technology, the ESI mechanism, and the cache tag libraries can support different caching periods for Web page fragments.When a JSP page is split into fragments, the following two conditions must be satisfied even if the master JSP page and the JSP fragments are not executed in the same server or at the same time.Cond. 1 - 1The total execution result of a master JSP page and the JSP fragments is the same as the JSP page before it was split.Cond. 1 - 2Each JSP page, which is either a master JSP page or a JSP fragment, may be executed without other JSP pages.These conditions are satisfied by maintaining the data and control dependences existing in a JSP page after the JSP page has been split into fragments. However, it is hard work for developers to detect data and control dependent portions in a JSP page, because the data and control flow of a JSP page can be divided among the JSP page, the JSP engine that executes the JSP page, any Java beans used in the JSP page, and etc.. Thus, a natural solution calls for automatically detecting data-dependent and control-dependent portions linked to the portions that developers want to split.The program slicing technique detects a set of program statements that affect a program statement S by analyzing the data and control dependences existing in the program. One program slice consists of the detected set of program statements and the statement S. This technique is useful when debugging or maintaining large programs. Since JSP pages are compiled into servlet programs by using a JSP compiler such as the Apache Jasper compiler [4], JSP slices can be obtained by applying program slicing technique to a servlet program compiled from a JSP page. However, the program slicing technique is not sufficient to split a JSP page into fragments, because the technique does not take into account that program slices areexecuted independently.Figure 1 shows a part of a sample JSP page and a sample servlet program compiled from the JSP page. Figure 2 (a) shows the data dependence graph obtained from the servlet program. In a program, when a statement S1 assigns a value to a variable and a statement S2 following S1 uses that value, a true data dependence exists between S1 and S2. Such a data dependence is denoted as S1 →S2. In Figure 2 (a), due to the data dependences, the program slice for the statement S10 consists of S1, S9, and S10. If the program slice is cut from the servlet program, the remaining program statements have errors because the data dependences S1 →S2, S11, and S12 and S9 → S11 and S12 are not honored. Thus, the program slicing technique does not work well for splitting JSP pages.3. JSP SplittingIn this paper, we propose JSP splitting, a method of splitting a JSP page into fragments. The proposed method analyzes data and control dependences in the servlet program compiled from a JSP page. At the time of analysis, JSP splitting takes into account that split JSP pages will be executed independently, and may not be executed in the same server or at the same time. First, the portions that developers want to split into a JSP fragment are selected. For the selected portions, the portions needed to satisfy the conditions 1 - 1 and 1 - 2 are detected. The detected portions are categorized into moved and copied portions, and are minimized in order to match the intentions of the developers.3.1. Ignorable Data DependencesBasically, JSP splitting does not allow the dependent statements to be split apart. However, if this rule is applied too strictly, none of the statements shown in Figure 1 (b) can be split, because there are interlocking dependences starting from S1 and S9.Here, we consider how the variable out shown in Figure 1 (b) is used. The variable out is used to write the text data of any Web page. Note that the value of out can be retrieved from any JSP engine. When a master JSP page JM includes a JSP fragment JF by using a jsp:include tag and a JSP engine executes both of them, JM first retrieves the value of out from the JSP engine and writes its own text data to the value. Next, J M invokes J F. After being invoked, J F also retrieves the value of out and writes its own text data to the value. The text data written by J M is returned to out through the JSP engine and merged with the text data written by J M. This means that the value of out can be utilized by any JSP page and the text data written to the value is maintained by the JSP engines. In other words, when a JSP page is split into fragments, a statement that retrieves the value of out can exist both in a servlet program compiled from a master JSP page and in servlet programs compiled from JSP fragments. Therefore, the data dependences for the variable out can be ignored at the time of splitting a JSP page.As shown in Figure 2 (a), none of the statements can be split while maintaining the data dependences existing in the servlet program shown in Figure 1 (b). However, if the data dependences for the variable out are ignored, the datadependence graph is changed as shown in Figure 2 (b). Using the data dependence graph shown in Figure 2 (b) makes it possible to split S2 from the set of S9, S10, S11, and S12 which cannot be split due to the data dependences for the variable book.In servlet programs compiled by the Apache Jasper compiler, the data dependences for the variables shown in Table1 can be ignored for the same reason as for the variable out.Since the values of these variables are defined at the top of each servlet program and are frequently referred to, most statements cannot be split if the data dependences are to be maintained.In general, the out-of-order execution is allowed for the statements without data and control dependences. Ignoring the data dependences for the variables shown in Table 1 may introduce an incorrect execution order of statements. For example,if S10 and S12 shown in Figure 1 are split into a JSP fragment and the JSP fragment is included before S11, an incorrect Web page is generated. In order to avoid such incorrect execution, our algorithm does not allow changes in the order of the statements that have ignored data dependences.3.2. Analysis of Data Dependences for Java beansIn a JSP page, Java beans are frequently used to store and retrieve data as property values. Each Java bean is a Java object and developers can use Java beans by using three kinds of tags in a JSP page.● jsp:useBean: Declares a named Java bean with its scope. When an object forthe Java bean does not exist within the declared scope, the bean is instantiated. Java beans can be declared with the scope of page, request,session or application.● jsp:getPrope rty: Calls the get method of a Java bean object and retrieves the property value.● jsp:setProperty: Calls the set method of a Java bean object and sets the property value.Java beans must be declared with the jsp:useBean tag before the other two operations. This means that a declaration of a Java bean and all of the other operations for the Java bean must be included in the same JSP page. This strongly limits the extent of a JSP fragment. In order to relax the limitation, JSP splitting allows declarations of Java beans to be copied to JSP fragments. The reason why declarations of Java beans can be copied is that the declarations do not have side effects. Each declaration merely instantiates a Java bean object when the Java bean object has not yet been instantiated within its scope. In other words, a Java bean object is not instantiated more than one time within its scope even if the declaration is copied to JSP fragments. Therefore, some of the operations for a Java bean can be split into fragments.When a property value is set for a Java bean by using a jsp:setProperty tag and retrieved from the JSP bean by using a jsp:getProperty tag, a true data dependence exists between the two operations.When the rule that data dependent statements cannot be split is applied, data dependent operations for a Java bean must be included in the same fragment. However, a data dependence between an operation that sets a property value for a JSP bean and another operation that retrieves the property value is maintained after the two operations are split if the following two conditions are satisfied.Cond. 2 - 1The scope of the Java bean is ”request”, ”session”, or ”application”. Cond. 2 - 2 The split JSP pages are executed in the same JSP engine.If these conditions are satisfied, JSP splitting allows the operations among which the data dependences exist to be split into different JSP pages, because the Java bean lives in the JSP engine during the execution of the split JSP pages. As a result, the portions split along with the portions selected by a developer can be reduced. However, the Web page fragments obtained by executing the split JSP pages satisfying these conditions must have the same caching period. This is because thedata dependence is not maintained if a JSP page was executed and a value is defined in the JSP page while another JSP page, in which the defined value is used, was not executed due to the valid cached content of the Web page.When a Java bean has the page scope, the dependent operations for the Java bean cannot be split. However, each operation that sets a property value for a Java bean with the page scope can be copied along with one or more operations that retrieve the same property value, because the operations that set property values for Java beans with the page scope do not have side effects.Figures 3 to 6 show the algorithms to split the operations for Java beans. These algorithms try to minimize the number of the operations that are moved or copied to a JSP fragment.4. JSP Splitting ToolWe implemented JSP splitting as a plug-in for Eclipse。