芯片封装可靠性试验专业术语

- 格式:docx

- 大小:10.98 KB

- 文档页数:2

集成电路专业术语一、集成电路设计集成电路设计(IC Design),是指根据功能要求和性能指标,将电路系统设计成一定工艺条件下集成电路的过程。

这个过程涉及到电子学、计算机科学、物理等多个学科的知识。

集成电路设计主要包括电路系统设计、版图设计、仿真验证等步骤。

二、芯片制造工艺芯片制造工艺(IC Manufacturing Process),是指将设计好的集成电路通过一系列复杂的物理和化学过程,在半导体材料上制造出来的过程。

这个过程包括晶圆制备、薄膜制备、掺杂、刻蚀、金属化等多个环节,每个环节都需要精确控制。

三、元件集成元件集成(Device Integration),是指将各种电子元件(如晶体管、电阻、电容等)集成在一块芯片上的过程。

这个过程需要考虑到元件之间的相互影响和相互作用,以保证整个电路的性能和稳定性。

四、电路封装电路封装(Package),是指将制造好的芯片进行封装的过程。

这个过程需要考虑到芯片的机械保护、信号传输、散热等多个方面,以保证整个集成电路的性能和可靠性。

五、芯片测试与可靠性芯片测试与可靠性(IC Testing and Reliability),是指对制造好的芯片进行测试和评估的过程。

这个过程需要用到各种测试设备和测试软件,以保证芯片的性能和可靠性。

六、集成电路应用领域集成电路应用领域(IC Application Fields),是指集成电路应用的各个领域,如通信、计算机、消费电子、汽车电子等。

随着科技的不断发展,集成电路的应用领域越来越广泛,已经成为现代科技的重要组成部分。

七、微电子技术发展微电子技术发展(Microelectronics Technology Development),是指微电子技术的不断发展和进步。

这个领域涉及到半导体材料、器件结构、工艺技术等方面的研究和开发,是集成电路发展的重要推动力。

八、集成电路产业生态集成电路产业生态(IC Industry Ecosystem),是指集成电路产业的上下游关系和生态系统。

半导体封装和质量术语封装和质量术语以下是TI 常见封装组、系列和偏好代码的定义,此外还有在评估TI 封装选项时可能十分有用的其他重要术语。

常见封装组定义BGA球栅阵列CFP同时包括定型和不定型 CFP = 陶瓷扁平封装LGA基板栅格阵列PFM塑料法兰安装封装QFP四方扁平封装SIP单列直插式封装OPTO*光传感器封装 = 光学RFID射频识别设备CGA柱栅阵列COF薄膜覆晶COG玻璃覆晶DIP双列直插式封装DSBGA芯片尺寸球栅阵列(WCSP = 晶圆级芯片封装)LCC引线式芯片载体NFMCA-LID带盖的基体金属腔PGA针栅阵列POS基板封装QFN四方扁平封装无引线SO小外形SON小外形无引线TO晶体管外壳ZIP锯齿形直插式uCSP微型芯片级封装DLP数字光处理模块模块TAB载带自动键合封装封装系列定义CBGA陶瓷球栅阵列CDIP玻璃密封陶瓷双列直插式封装CDIP SB侧面钎焊陶瓷双列直插式封装CPGA陶瓷针栅阵列CZIP陶瓷锯齿形封装DFP双侧引脚扁平封装FC/CSP倒装芯片/芯片级封装HLQFP热增强型低厚度 QFPHQFP热增强型四方扁平封装HSOP热增强型小外形封装HTQFP热增强型薄型四方扁平封装HTSSOP热增强型薄型紧缩小外形封装HVQFP热增强型极薄四方扁平封装JLCC J 形引线式陶瓷或金属芯片载体LCCC无引线陶瓷芯片载体LQFP低厚度四方扁平封装PDIP塑料双列直插式封装SOJ J 形引线式小外形封装SOP小外形封装(日本)SSOP紧缩小外形封装TQFP薄型四方扁平封装TSSOP薄型紧缩小外形封装TVFLGA薄型极细基板栅格阵列TVSOP极薄小外形封装VQFP极薄四方扁平封装DIMM*双列直插式内存模块HSSOP*热增强型紧缩小外形封装LPCC*无引线塑料芯片载体MCM*多芯片模块MQFP*金属四方扁平封装PLCC*塑料引线式芯片载体PPGA*塑料针栅阵列SDIP*紧缩双列直插式封装SIMM*单列直插式内存模块SODIMM*小外形双列直插式内存模块TSOP*薄型小外形封装VSOP*极小外形封装XCEPT*例外 - 可能不是实际封装产品偏好代码定义P首选封装。

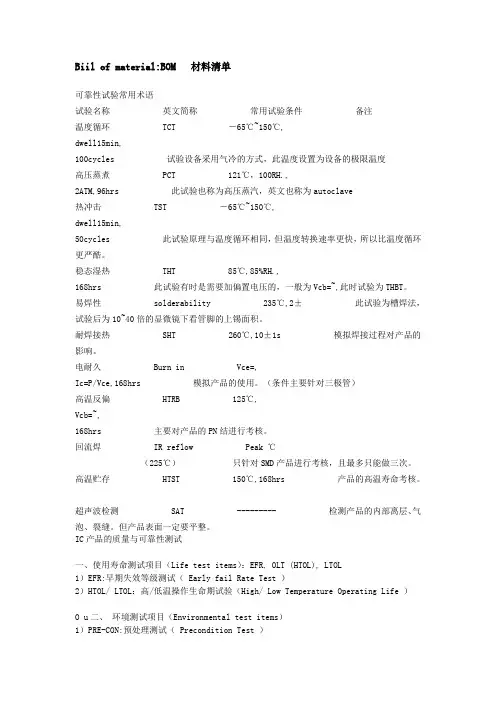

芯片封装可靠性试验专业术语Biil of material:BOM 材料清单可靠性试验常用术语试验名称英文简称常用试验条件备注温度循环 TCT -65℃~150℃,dwell15min,100cycles 试验设备采用气冷的方式,此温度设置为设备的极限温度高压蒸煮PCT 121℃,100RH.,2ATM,96hrs 此试验也称为高压蒸汽,英文也称为autoclave热冲击 TST -65℃~150℃,dwell15min,50cycles 此试验原理与温度循环相同,但温度转换速率更快,所以比温度循环更严酷。

稳态湿热THT 85℃,85%RH.,168hrs 此试验有时是需要加偏置电压的,一般为Vcb=~,此时试验为THBT。

易焊性solderability 235℃,2±此试验为槽焊法,试验后为10~40倍的显微镜下看管脚的上锡面积。

耐焊接热SHT 260℃,10±1s模拟焊接过程对产品的影响。

电耐久 Burn in Vce=,Ic=P/Vce,168hrs 模拟产品的使用。

(条件主要针对三极管)高温反偏HTRB 125℃,Vcb=~,168hrs 主要对产品的PN结进行考核。

回流焊IR reflow Peak ℃(225℃)只针对SMD产品进行考核,且最多只能做三次。

高温贮存HTST 150℃,168hrs 产品的高温寿命考核。

超声波检测 SAT --------- 检测产品的内部离层、气泡、裂缝。

但产品表面一定要平整。

IC产品的质量与可靠性测试一、使用寿命测试项目(Life test items):EFR, OLT (HTOL), LTOL1)EFR:早期失效等级测试( Early fail Rate Test )2)HTOL/ LTOL:高/低温操作生命期试验(High/ Low Temperature Operating Life )O u二、环境测试项目(Environmental test items)1)PRE-CON:预处理测试( Precondition Test )2)THB: 加速式温湿度及偏压测试(Temperature Humidity Bias Test )3)HAST高加速温湿度及偏压测试(HAST: Highly Accelerated Stress Test )4)PCT:高压蒸煮试验 Pressure Cook Test (Autoclave Test)5)TCT: 高低温循环试验(Temperature Cycling Test )6)TST: 高低温冲击试验(Thermal Shock Test )7)HTST: 高温储存试验(High Temperature Storage Life Test )8)可焊性试验(Solderability Test )9)SHT Test:焊接热量耐久测试( Solder Heat Resistivity T est )三、耐久性测试项目(Endurance test items )1)周期耐久性测试(Endurance Cycling Test)2)数据保持力测试(Data Retention T est)。

ic封装术语IC封装术语IC(集成电路)封装是将芯片封装成实际可应用的器件的过程。

在IC封装过程中,使用了许多术语来描述不同的封装类型、尺寸和特性。

本文将介绍一些常见的IC封装术语,以帮助读者更好地理解和选择合适的封装。

1. DIP封装(Dual In-line Package)DIP封装是最早也是最常见的IC封装类型之一。

它采用两排引脚,引脚以直线排列,适用于手工插入和焊接。

DIP封装通常用于较大的芯片,如微控制器和存储器芯片。

2. SOP封装(Small Outline Package)SOP封装是一种比DIP封装更小型的封装类型。

它采用表面贴装技术,引脚以直线或弯曲排列。

SOP封装适用于对空间要求较高的应用,如移动设备和计算机外围设备。

3. QFP封装(Quad Flat Package)QFP封装是一种较大的表面贴装封装类型。

它采用四个方向平均分布的引脚,具有较高的引脚密度和良好的散热性能。

QFP封装适用于需要处理大量信号的芯片,如通信芯片和图形处理器。

4. BGA封装(Ball Grid Array)BGA封装是一种先进的表面贴装封装类型。

它采用小球形引脚,以网格状排列在芯片底部。

BGA封装具有更高的引脚密度和更好的散热性能,适用于高性能处理器和FPGA芯片。

5. LGA封装(Land Grid Array)LGA封装是一种类似于BGA封装的表面贴装封装类型。

它采用金属焊盘而不是小球形引脚,以更好地支持高频率和高速信号传输。

LGA封装适用于需要较高信号完整性的应用,如服务器和网络设备。

6. CSP封装(Chip Scale Package)CSP封装是一种尺寸更小的封装类型,接近芯片的尺寸。

它采用直接焊接或粘贴技术将芯片封装成器件。

CSP封装适用于对尺寸和重量要求极高的应用,如智能卡和便携式设备。

7. QFN封装(Quad Flat No-leads)QFN封装是一种无引脚的封装类型,引脚隐藏在芯片的底部。

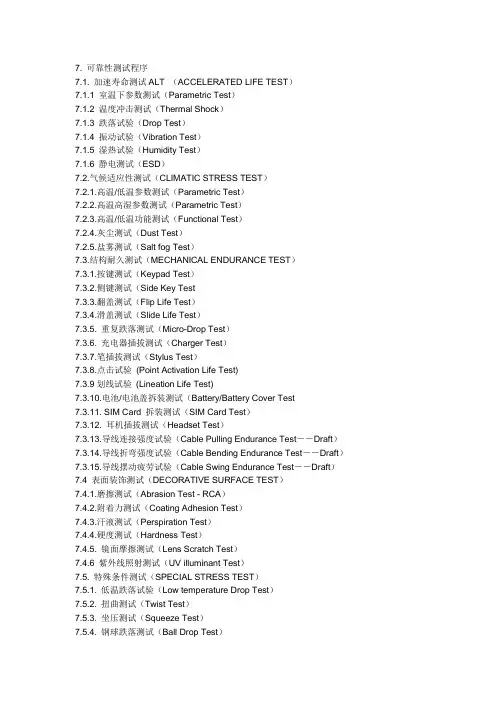

7. 可靠性测试程序7.1. 加速寿命测试ALT (ACCELERATED LIFE TEST)7.1.1 室温下参数测试(Parametric Test)7.1.2 温度冲击测试(Thermal Shock)7.1.3 跌落试验(Drop Test)7.1.4 振动试验(Vibration Test)7.1.5 湿热试验(Humidity Test)7.1.6 静电测试(ESD)7.2.气候适应性测试(CLIMATIC STRESS TEST)7.2.1.高温/低温参数测试(Parametric Test)7.2.2.高温高湿参数测试(Parametric Test)7.2.3.高温/低温功能测试(Functional Test)7.2.4.灰尘测试(Dust Test)7.2.5.盐雾测试(Salt fog Test)7.3.结构耐久测试(MECHANICAL ENDURANCE TEST)7.3.1.按键测试(Keypad Test)7.3.2.侧键测试(Side Key Test7.3.3.翻盖测试(Flip Life Test)7.3.4.滑盖测试(Slide Life Test)7.3.5. 重复跌落测试(Micro-Drop Test)7.3.6. 充电器插拔测试(Charger Test)7.3.7.笔插拔测试(Stylus Test)7.3.8.点击试验(Point Activation Life Test)7.3.9划线试验(Lineation Life Test)7.3.10.电池/电池盖拆装测试(Battery/Battery Cover Test7.3.11. SIM Card 拆装测试(SIM Card Test)7.3.12. 耳机插拔测试(Headset Test)7.3.13.导线连接强度试验(Cable Pulling Endurance Test--Draft)7.3.14.导线折弯强度试验(Cable Bending Endurance Test--Draft)7.3.15.导线摆动疲劳试验(Cable Swing Endurance Test--Draft)7.4 表面装饰测试(DECORATIVE SURFACE TEST)7.4.1.磨擦测试(Abrasion Test - RCA)7.4.2.附着力测试(Coating Adhesion Test)7.4.3.汗液测试(Perspiration Test)7.4.4.硬度测试(Hardness Test)7.4.5. 镜面摩擦测试(Lens Scratch Test)7.4.6 紫外线照射测试(UV illuminant Test)7.5. 特殊条件测试(SPECIAL STRESS TEST)7.5.1. 低温跌落试验(Low temperature Drop Test)7.5.2. 扭曲测试(Twist Test)7.5.3. 坐压测试(Squeeze Test)7.5.4. 钢球跌落测试(Ball Drop Test)7.6 其他条件测试7.6.1螺钉的测试(Screw Test)7.6.2挂绳孔强度的测试(Hand Strap Test)。

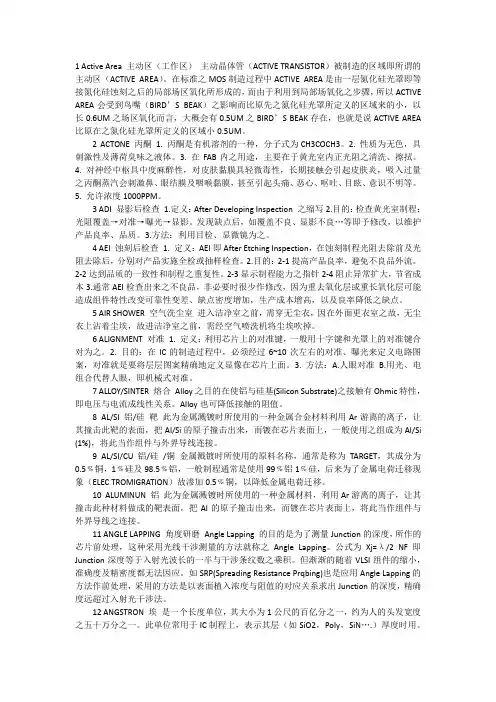

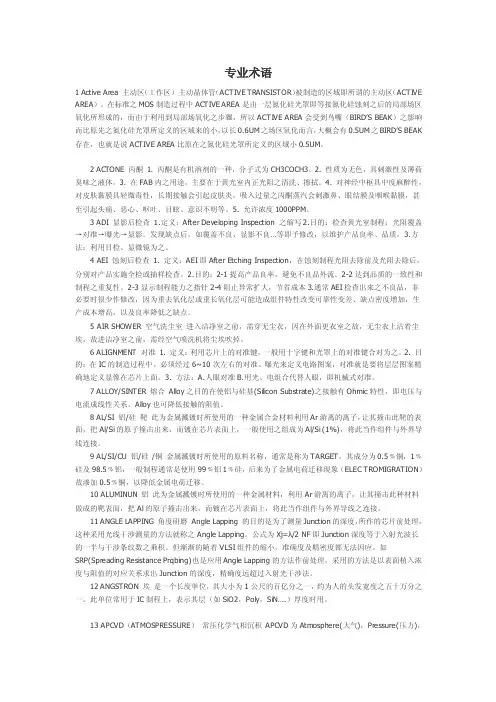

1 Active Area 主动区(工作区)主动晶体管(ACTIVE TRANSISTOR)被制造的区域即所谓的主动区(ACTIVE AREA)。

在标准之MOS制造过程中ACTIVE AREA是由一层氮化硅光罩即等接氮化硅蚀刻之后的局部场区氧化所形成的,而由于利用到局部场氧化之步骤,所以ACTIVE AREA会受到鸟嘴(BIRD’S BEAK)之影响而比原先之氮化硅光罩所定义的区域来的小,以长0.6UM之场区氧化而言,大概会有0.5UM之BIRD’S BEAK存在,也就是说ACTIVE AREA 比原在之氮化硅光罩所定义的区域小0.5UM。

2 ACTONE 丙酮1. 丙酮是有机溶剂的一种,分子式为CH3COCH3。

2. 性质为无色,具刺激性及薄荷臭味之液体。

3. 在FAB内之用途,主要在于黄光室内正光阻之清洗、擦拭。

4. 对神经中枢具中度麻醉性,对皮肤黏膜具轻微毒性,长期接触会引起皮肤炎,吸入过量之丙酮蒸汽会刺激鼻、眼结膜及咽喉黏膜,甚至引起头痛、恶心、呕吐、目眩、意识不明等。

5. 允许浓度1000PPM。

3 ADI 显影后检查1.定义:After Developing Inspection 之缩写2.目的:检查黄光室制程;光阻覆盖→对准→曝光→显影。

发现缺点后,如覆盖不良、显影不良…等即予修改,以维护产品良率、品质。

3.方法:利用目检、显微镜为之。

4 AEI 蚀刻后检查1. 定义:AEI即After Etching Inspection,在蚀刻制程光阻去除前及光阻去除后,分别对产品实施全检或抽样检查。

2.目的:2-1提高产品良率,避免不良品外流。

2-2达到品质的一致性和制程之重复性。

2-3显示制程能力之指针2-4阻止异常扩大,节省成本3.通常AEI检查出来之不良品,非必要时很少作修改,因为重去氧化层或重长氧化层可能造成组件特性改变可靠性变差、缺点密度增加,生产成本增高,以及良率降低之缺点。

5 AIR SHOWER 空气洗尘室进入洁净室之前,需穿无尘衣,因在外面更衣室之故,无尘衣上沾着尘埃,故进洁净室之前,需经空气喷洗机将尘埃吹掉。

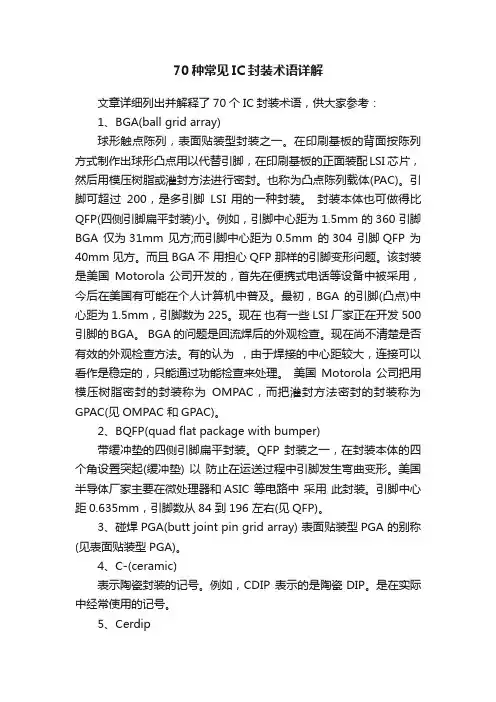

70种常见IC封装术语详解文章详细列出并解释了70个IC封装术语,供大家参考:1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

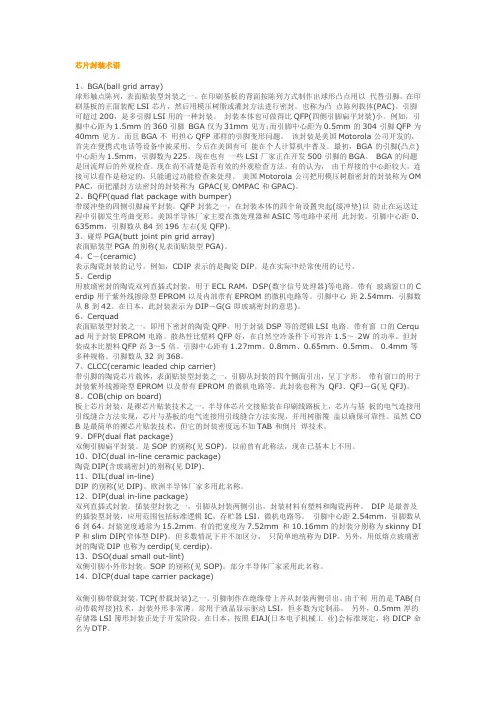

芯片封装术语1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OM PAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0. 635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array)表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

半导体封装术语

1. “封装基板”,你知道手机、电脑这些电子设备里都有它的身影吗?就好比是房子的地基一样重要!

2. “引线键合”,这就像是给半导体元件搭起的特殊桥梁,让它们能更好地沟通协作呢!

3. “倒装芯片”,哎呀,这可真是个厉害的家伙,把芯片倒过来安装,效果却出奇地好,神奇吧!

4. “塑封料”,它就像是半导体的保护衣,把它们好好地包裹起来,给予贴心保护呀!

5. “芯片贴装”,这就像是给芯片找个安稳的家,让它能安心地工作哟!

6. “金线”,这细细的金线可不容小觑,它可是半导体里的重要连接线呢,就像我们的神经一样!

7. “封装工艺”,这可是个复杂又精细的过程,就如同雕琢一件艺术品一样呢!

8. “散热片”,它可是半导体的“清凉小助手”,帮助它们散去多余的热量呀!

9. “封装测试”,这就像是给半导体做一次全面的体检,确保它们健康着呢!

10. “管脚”,这些小小的管脚就像是半导体的触角,用来和外界交流沟通呀!

我的观点结论就是:半导体封装术语真的很神奇,每个术语都有着独特的作用和意义,它们共同推动着半导体行业的发展。

Biil of material:BOM 材料清单可靠性试验常用术语试验名称英文简称常用试验条件备注温度循环 TCT -65℃~150℃,dwell15min,100cycles 试验设备采用气冷的方式,此温度设置为设备的极限温度高压蒸煮 PCT 121℃,100RH.,2ATM,96hrs 此试验也称为高压蒸汽,英文也称为autoclave热冲击 TST -65℃~150℃,dwell15min,50cycles 此试验原理与温度循环相同,但温度转换速率更快,所以比温度循环更严酷。

稳态湿热 THT 85℃,85%RH.,168hrs 此试验有时是需要加偏置电压的,一般为Vcb=~,此时试验为THBT。

易焊性 solderability 235℃,2±此试验为槽焊法,试验后为10~40倍的显微镜下看管脚的上锡面积。

耐焊接热 SHT 260℃,10±1s模拟焊接过程对产品的影响。

电耐久 Burn in Vce=,Ic=P/Vce,168hrs 模拟产品的使用。

(条件主要针对三极管)高温反偏 HTRB 125℃,Vcb=~,168hrs 主要对产品的PN结进行考核。

回流焊 IR reflow Peak ℃(225℃)只针对SMD产品进行考核,且最多只能做三次。

高温贮存 HTST 150℃,168hrs 产品的高温寿命考核。

超声波检测 SAT --------- 检测产品的内部离层、气泡、裂缝。

但产品表面一定要平整。

IC产品的质量与可靠性测试一、使用寿命测试项目(Life test items):EFR, OLT (HTOL), LTOL1)EFR:早期失效等级测试( Early fail Rate Test )2)HTOL/ LTOL:高/低温操作生命期试验(High/ Low Temperature Operating Life )O u二、环境测试项目(Environmental test items)1)PRE-CON:预处理测试( Precondition Test )2)THB: 加速式温湿度及偏压测试(Temperature Humidity Bias Test )3)HAST高加速温湿度及偏压测试(HAST: Highly Accelerated Stress Test )4)PCT:高压蒸煮试验 Pressure Cook Test (Autoclave Test)5)TCT: 高低温循环试验(Temperature Cycling Test )6)TST: 高低温冲击试验(Thermal Shock Test )7)HTST: 高温储存试验(High Temperature Storage Life Test )8)可焊性试验(Solderability Test )9)SHT Test:焊接热量耐久测试( Solder Heat Resistivity Test )三、耐久性测试项目(Endurance test items )1)周期耐久性测试(Endurance Cycling Test)2)数据保持力测试(Data Retention Test)。

专业术语1 Active Area 主动区(工作区)主动晶体管(ACTIVE TR ANSISTOR)被制造的区域即所谓的主动区(ACTI VE AREA)。

在标准之MOS制造过程中ACTIVE AREA是由一层氮化硅光罩即等接氮化硅蚀刻之后的局部场区氧化所形成的,而由于利用到局部场氧化之步骤,所以ACTI VE AREA会受到鸟嘴(BIRD’S BEAK)之影响而比原先之氮化硅光罩所定义的区域来的小,以长0.6UM之场区氧化而言,大概会有0.5UM之BIRD’S BEAK 存在,也就是说ACTIVE AREA比原在之氮化硅光罩所定义的区域小0.5UM。

2 ACTONE 丙酮 1. 丙酮是有机溶剂的一种,分子式为CH3COCH3。

2. 性质为无色,具刺激性及薄荷臭味之液体。

3. 在FAB内之用途,主要在于黄光室内正光阻之清洗、擦拭。

4. 对神经中枢具中度麻醉性,对皮肤黏膜具轻微毒性,长期接触会引起皮肤炎,吸入过量之丙酮蒸汽会刺激鼻、眼结膜及咽喉黏膜,甚至引起头痛、恶心、呕吐、目眩、意识不明等。

5. 允许浓度1000PPM。

3 ADI 显影后检查 1.定义:After Developing Inspection 之缩写2.目的:检查黄光室制程;光阻覆盖→对准→曝光→显影。

发现缺点后,如覆盖不良、显影不良…等即予修改,以维护产品良率、品质。

3.方法:利用目检、显微镜为之。

4 AEI 蚀刻后检查 1. 定义:AEI即After Etching Inspection,在蚀刻制程光阻去除前及光阻去除后,分别对产品实施全检或抽样检查。

2.目的:2-1提高产品良率,避免不良品外流。

2-2达到品质的一致性和制程之重复性。

2-3显示制程能力之指针2-4阻止异常扩大,节省成本3.通常AEI检查出来之不良品,非必要时很少作修改,因为重去氧化层或重长氧化层可能造成组件特性改变可靠性变差、缺点密度增加,生产成本增高,以及良率降低之缺点。

IC封装术语详解1、BGA(ball grid array) 球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC).引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比 QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1。

5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0。

5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm, 引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA.BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper) 带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装.引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic) 表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip 用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路.带有玻璃窗口的Cerdip 用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。

IC封装术语解析1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array)表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

IC封装术语1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为 1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array)表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

半导体封装的常用术语1.引言1.1 概述概述部分的内容可以从以下几个方面进行描述:半导体封装是电子器件中至关重要的一个环节,它是将芯片封装到外部环境中,以保护芯片免受机械和环境的损害,并提供与外部系统的连接。

封装是实现芯片与外界互联的关键技术,它起着桥梁的作用,将微小而脆弱的芯片封装成成品,使之能够安全可靠地运行。

半导体封装领域的发展已经取得了令人瞩目的成就。

随着半导体技术的不断进步和市场需求的不断扩大,不同类型的封装技术应运而生。

目前,常见的半导体封装技术包括裸片封装、芯片级封装、模块级封装等。

每种封装技术都有其特点和适应的应用领域。

本文将重点介绍半导体封装中常用的术语。

这些术语涉及到封装材料、封装结构、封装工艺等方面,对于理解和应用半导体封装技术具有重要意义。

通过对这些术语的详细解释和分析,读者能够更好地了解半导体封装的基本原理和技术要点。

在接下来的章节中,我们将逐一介绍这些常用的术语,并对其背后的原理和应用进行深入探讨。

通过阅读本文,读者将能够系统地理解和掌握半导体封装领域的基本概念和技术,为今后的研究和应用提供有力支持。

半导体封装是半导体技术发展的重要环节,对于提高芯片的可靠性、降低成本、提高性能具有重要作用。

因此,深入了解和掌握半导体封装的常用术语是十分必要的。

本文将为读者提供一个系统、全面的半导体封装术语参考,帮助读者更好地理解和应用半导体封装技术,推动半导体封装领域的发展。

接下来的章节将详细介绍各个术语的含义和应用,希望能够对读者有所帮助。

1.2 文章结构文章结构部分应包括以下内容:文章结构部分主要介绍了整篇文章的构成和布局,为读者提供了整体的把握和导航。

在本文中,文章结构分为三个主要部分:引言、正文和结论。

引言部分首先会概述本文的主要内容和研究对象,介绍半导体封装的意义和重要性,引发读者的兴趣。

接下来,文章结构部分会具体介绍三个小节:概述、文章结构和目的。

概述部分会进一步阐述本文对半导体封装的定义和范围,以及封装技术的重要性。

70种IC封装术语1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且B GA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array)表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

芯片测试的几个术语及解释(CP、FT、WAT)CP是把坏的Die挑出来,可以减少封装和测试的成本。

可以更直接的知道Wafer 的良率。

FT是把坏的chip挑出来;检验封装的良率。

现在对于一般的wafer工艺,很多公司多把CP给省了;减少成本。

CP对整片Wafer的每个Die来测试而FT则对封装好的Chip来测试。

CP Pass 才会去封装。

然后FT,确保封装后也Pass。

WAT是Wafer AcceptanceT est,对专门的测试图形(test key)的测试,通过电参数来监控各步工艺是否正常和稳定;CP是wafer level的chip probing,是整个wafer工艺,包括backgrinding和backmetal(if need),对一些基本器件参数的测试,如vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,一般测试机台的电压和功率不会很高;FT是packaged chip level的Final Test,主要是对于这个(CPpassed)IC或Device芯片应用方面的测试,有些甚至是待机测试;Pass FP还不够,还需要做process qual 和product qualCP 测试对Memory来说还有一个非常重要的作用,那就是通过MRA计算出chip level 的Repair address,通过Laser Repair将CP 测试中的Repairable die 修补回来,这样保证了yield和reliability两方面的提升。

CP是对wafer进行测试,检查fab厂制造的工艺水平FT是对package进行测试,检查封装厂制造的工艺水平对于测试项来说,有些测试项在CP时会进行测试,在FT时就不用再次进行测试了,节省了FT测试时间;但是有些测试项必须在FT 时才进行测试(不同的设计公司会有不同的要求)一般来说,CP测试的项目比较多,比较全;FT测的项目比较少,但都是关键项目,条件严格。