AT89C51的引脚功能

- 格式:doc

- 大小:47.00 KB

- 文档页数:3

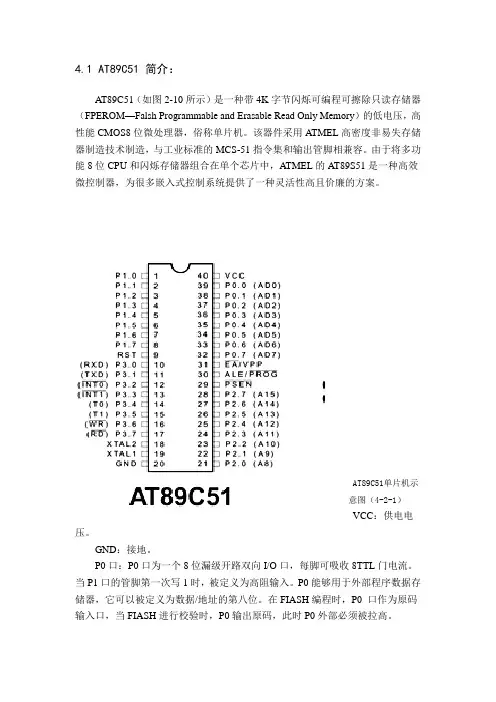

4.1 AT89C51 简介:AT89C51(如图2-10所示)是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。

该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89S51是一种高效微控制器,为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

AT89C51单片机示意图(4-2-1)VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH 编程和校验时,P1口作为第八位地址接收。

P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。

并因此作为输入时,P2口的管脚被外部拉低,将输出电流。

这是由于内部上拉的缘故。

P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。

在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。

P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

AT89S51单片机的认识和管脚功能AT89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。

该器件采用ATMEL 高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89C51是一种高效微控制器,为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

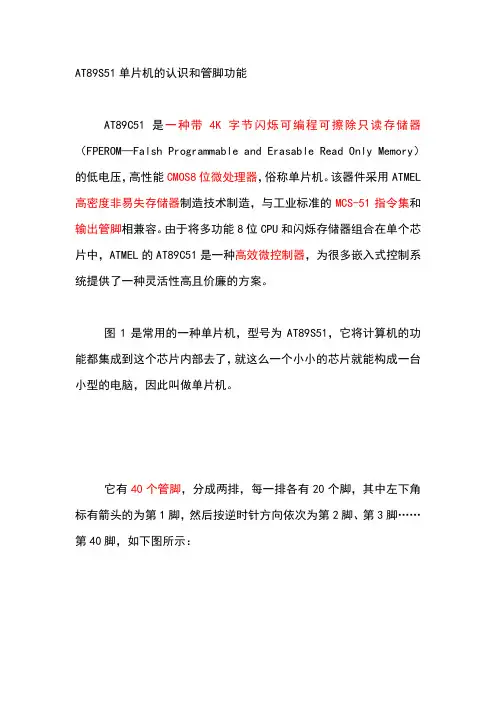

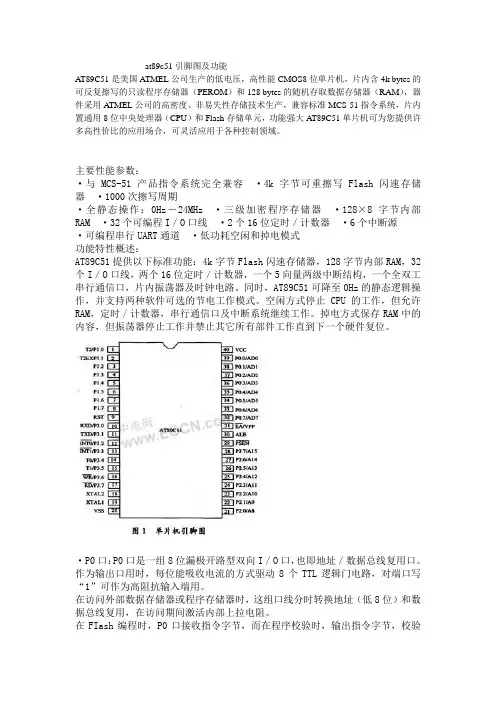

图1是常用的一种单片机,型号为AT89S51,它将计算机的功能都集成到这个芯片内部去了,就这么一个小小的芯片就能构成一台小型的电脑,因此叫做单片机。

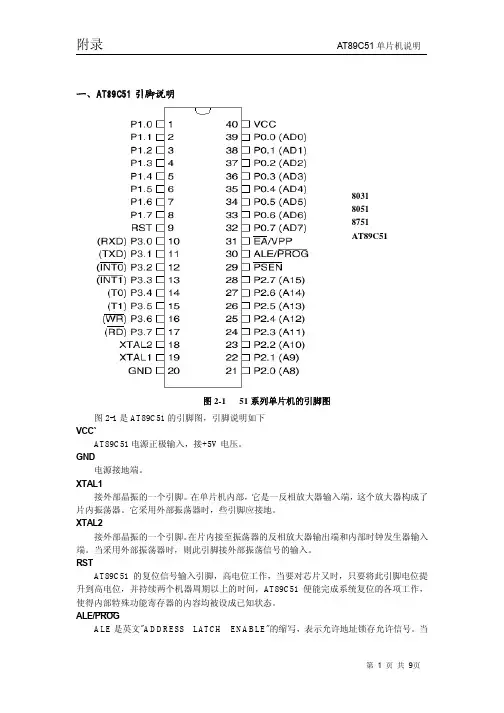

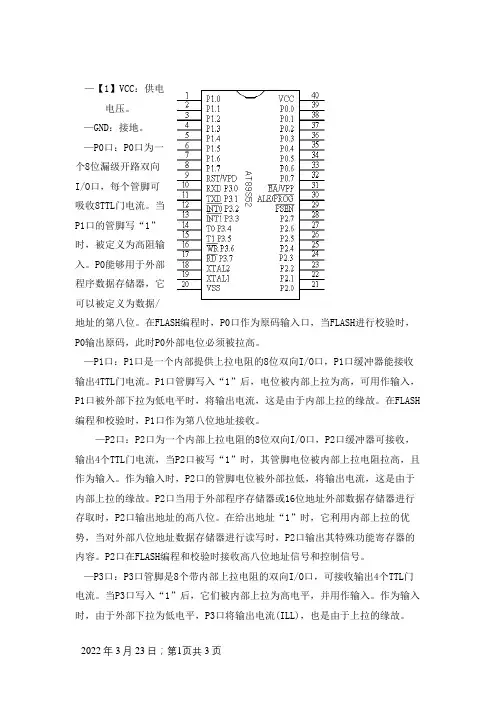

它有40个管脚,分成两排,每一排各有20个脚,其中左下角标有箭头的为第1脚,然后按逆时针方向依次为第2脚、第3脚……第40脚,如下图所示:在40个管脚中,其中有32个脚可用于各种控制,比如控制小灯的亮与灭、控制电机的正转与反转、控制电梯的升与降等,这32个脚叫做单片机的“端口”,在单片机技术中,每个端口都有一个特定的名字,比如第一脚的那个端口叫做“P1.0”,由于本次试验仅仅控制一个小灯的亮与灭,由此只用一个端口就行了,我们就用第一脚的P1.0端口吧,如下图所示:1.主要特性:·与MCS-51 兼容·4K字节可编程闪烁存储器寿命:1000写/擦循环数据保留时间:10年·全静态工作:0Hz-24Hz·三级程序存储器锁定·128*8位内部RAM·32可编程I/O线·两个16位定时器/计数器·5个中断源·可编程串行通道·低功耗的闲置和掉电模式·片内振荡器和时钟电路2.管脚说明:VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL 门电流。

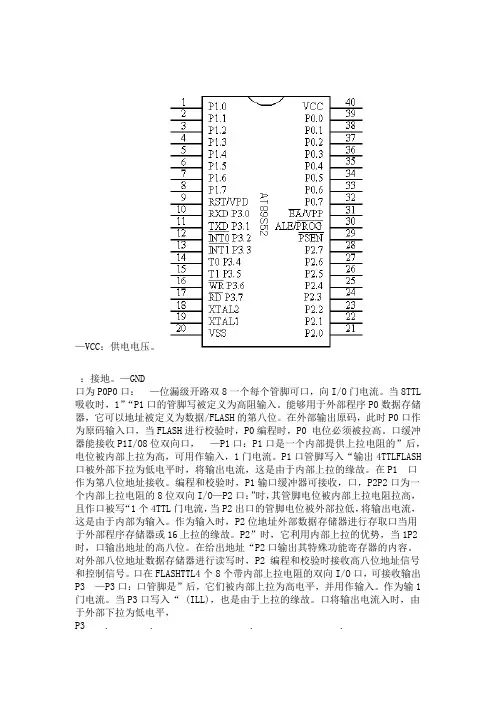

—VCC:供电电压。

:接地。

—GND口为P0P0口:—位漏级开路双8一个每个管脚可口,向I/O门电流。

当8TTL吸收时,1”“P1口的管脚写被定义为高阻输入。

能够用于外部程序P0数据存储器,它可以地址被定义为数据/FLASH的第八位。

在外部输出原码,此时P0口作为原码输入口,当FLASH进行校验时,P0编程时,P0 电位必须被拉高。

口缓冲器能接收P1I/O8位双向口,—P1口:P1口是一个内部提供上拉电阻的”后,电位被内部上拉为高,可用作输入,1门电流。

P1口管脚写入“输出4TTLFLASH口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在P1 口作为第八位地址接收。

编程和校验时,P1输口缓冲器可接收,口,P2P2口为一个内部上拉电阻的8位双向I/O—P2口:”时,其管脚电位被内部上拉电阻拉高,且作口被写“1个4TTL门电流,当P2出口的管脚电位被外部拉低,将输出电流,这是由于内部为输入。

作为输入时,P2位地址外部数据存储器进行存取口当用于外部程序存储器或16上拉的缘故。

P2”时,它利用内部上拉的优势,当1P2时,口输出地址的高八位。

在给出地址“P2口输出其特殊功能寄存器的内容。

对外部八位地址数据存储器进行读写时,P2 编程和校验时接收高八位地址信号和控制信号。

口在FLASHTTL4个8个带内部上拉电阻的双向I/O口,可接收输出P3 —P3口:口管脚是”后,它们被内部上拉为高电平,并用作输入。

作为输1门电流。

当P3口写入“ (ILL),也是由于上拉的缘故。

口将输出电流入时,由于外部下拉为低电平,P3 . . . .P3口也可作为AT89C51的一些特殊功能口,如下所示:P3.0 RXD(串行输入口)P3.1 TXD(串行输出口)P3.2 (外部中断0) 0INT P3.3 (外部中断1) 1INT P3.4 T0(记时器0外部输入)P3.5 T1(记时器1外部输入)WR(外部数据存储器写选通) P3.6P3.7 (外部数据存储器读选通)RD P3口同时为闪烁编程和编程校验接收一些控制信号。

AT89C51引脚图及功能电子元件知识2010-03-04 23:12:41 阅读1759 评论1 字号:大中小订阅89C51外部引脚图:(可以直接拷入ASM程序文件中,作注释使用,十分方便); ┏━┓┏━┓; P1.0 ┫1 ┗┛40┣Vcc; P1.1 ┫2 39┣P0.0; P1.2 ┫3 38┣P0.1; P1.3 ┫4 37┣P0.2; P1.4 ┫5 36┣P0.3; P1.5 ┫6 35┣P0.4; P1.6 ┫7 34┣P0.5; P1.7 ┫8 33┣P0.6; RST/Vpd ┫9 32┣P0.7; RXD P3.0 ┫10 31┣-EA/Vpp(内1/外0 程序地址选择); TXD P3.1 ┫11 30┣ALE/-P (地址锁存输出); -INT0 P3.2 ┫12 29┣-PSEN (外部程序读选通输出); -INT1 P3.3 ┫13 28┣P2.7; T0 P3.4 ┫14 27┣P2.6; T1 P3.5 ┫15 26┣P2.5; -WR P3.6 ┫16 25┣P2.4; -RD P3.7 ┫17 24┣P2.3; X2 ┫18 23┣P2.2; X1 ┫19 22┣P2.1; GND ┫20 21┣P2.0; ┗━━━━┛引脚说明:①电源引脚Vcc(40脚):典型值+5V。

Vss(20脚):接低电平。

②外部晶振X1、X2分别与晶体两端相连接。

当采用外部时钟信号时,X2接振荡信号,X1接地。

③输入输出口引脚:P0口:I/O双向口。

作输入口时,应先软件置“ 1”。

P1口:I/O双向口。

作输入口时,应先软件置“ 1”。

P2口:I/O双向口。

作输入口时,应先软件置“ 1”。

P3口:I/O双向口。

作输入口时,应先软件置“ 1”。

④控制引脚:RST/Vpd、ALE/-PROG、-PSEN、-EA/Vpp组成了MSC-51的控制总线。

RST/Vpd(9脚):复位信号输入端(高电平有效)。

AT89C51引脚图及功能电子元件知识2010-03-04 23:12:41 阅读1759 评论1 字号:大中小订阅89C51外部引脚图:(可以直接拷入ASM程序文件中,作注释使用,十分方便); ┏━┓┏━┓; P1.0 ┫1 ┗┛40┣Vcc; P1.1 ┫2 39┣P0.0; P1.2 ┫3 38┣P0.1; P1.3 ┫4 37┣P0.2; P1.4 ┫5 36┣P0.3; P1.5 ┫6 35┣P0.4; P1.6 ┫7 34┣P0.5; P1.7 ┫8 33┣P0.6; RST/Vpd ┫9 32┣P0.7; RXD P3.0 ┫10 31┣-EA/Vpp(内1/外0 程序地址选择); TXD P3.1 ┫11 30┣ALE/-P (地址锁存输出); -INT0 P3.2 ┫12 29┣-PSEN (外部程序读选通输出); -INT1 P3.3 ┫13 28┣P2.7; T0 P3.4 ┫14 27┣P2.6; T1 P3.5 ┫15 26┣P2.5; -WR P3.6 ┫16 25┣P2.4; -RD P3.7 ┫17 24┣P2.3; X2 ┫18 23┣P2.2; X1 ┫19 22┣P2.1; GND ┫20 21┣P2.0; ┗━━━━┛引脚说明:①电源引脚Vcc(40脚):典型值+5V。

Vss(20脚):接低电平。

②外部晶振X1、X2分别与晶体两端相连接。

当采用外部时钟信号时,X2接振荡信号,X1接地。

③输入输出口引脚:P0口:I/O双向口。

作输入口时,应先软件置“ 1”。

P1口:I/O双向口。

作输入口时,应先软件置“ 1”。

P2口:I/O双向口。

作输入口时,应先软件置“ 1”。

P3口:I/O双向口。

作输入口时,应先软件置“ 1”。

④控制引脚:RST/Vpd、ALE/-PROG、-PSEN、-EA/Vpp组成了MSC-51的控制总线。

RST/Vpd(9脚):复位信号输入端(高电平有效)。

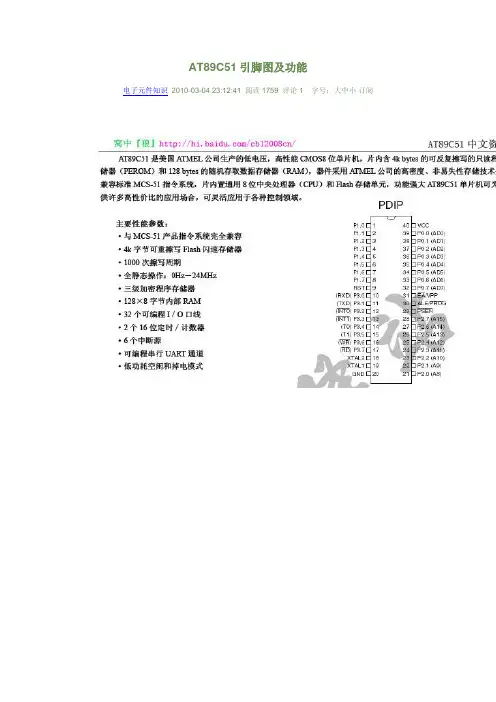

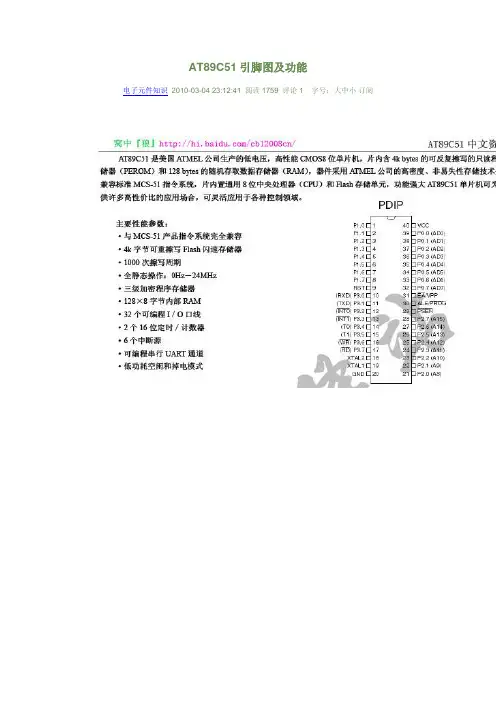

at89c51引脚图及功能AT89C51是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4k bytes的可反复擦写的只读程序存储器(PEROM)和128 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器(CPU)和Flash存储单元,功能强大AT89C51单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。

主要性能参数:·与MCS-51产品指令系统完全兼容·4k字节可重擦写Flash闪速存储器·1000次擦写周期·全静态操作:0Hz-24MHz ·三级加密程序存储器·128×8字节内部RAM ·32个可编程I/O口线·2个16位定时/计数器·6个中断源·可编程串行UART通道·低功耗空闲和掉电模式功能特性概述:AT89C51提供以下标准功能:4k字节Flash闪速存储器,128字节内部RAM,32个I/O口线,两个16位定时/计数器,一个5向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,AT89C51可降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。

空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。

掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。

·P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口。

作为输出口用时,每位能吸收电流的方式驱动8个TTL逻辑门电路,对端口写“1”可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

在FIash编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

AT89C51简介AT89C51是一款由8051微控制器系列衍生的8位单片机。

它由Atmel公司开发,主要用于嵌入式系统和单板计算机中的应用。

AT89C51是一款非常常见的单片机,使用广泛,并且在市场上易于获得。

特性•8位CPU架构•4K字节的Flash存储器•128字节的RAM存储器•32个通用输入/输出引脚•2个计数器/定时器•6个中断源•电源电压范围:4.0V至6.0VAT89C51具有32个引脚,每个引脚都可以配置为输入或输出。

以下是一些重要的引脚功能:1.P0(引脚2至9):P0口是一个8位的双向通用I/O口。

在默认情况下,它被配置为准双向输入口。

用户可以通过设置相应的位来将其配置为输出端口。

2.P1(引脚10至17):P1口也是一个8位的双向通用I/O口。

3.P2(引脚21至28):P2口也是一个8位的双向通用I/O口,但是它还具有其他功能。

P2口可以用作从机模式的串行数据接口。

4.P3(引脚1、16、17):P3口是一个6位的双向通用I/O口。

它还具有其他特殊功能。

P3口的引脚1和引脚16用作外部中断源,引脚17用作时钟输入。

5.EA/VPP(引脚31):EA/VPP用于给单片机提供外部存储器的编程电压。

AT89C51单片机具有许多功能和特性,使其成为嵌入式系统设计的理想选择。

1.存储器:AT89C51具有4K字节的Flash存储器,用于存储程序和数据。

它还具有128字节的RAM存储器,用于临时存储数据。

2.计数器/定时器:AT89C51具有两个16位的计数器/定时器。

这些计数器可以用于计时、生成脉冲和测量时间间隔。

3.中断:AT89C51具有6个中断源,包括外部中断、定时器中断和串行通信中断。

中断可以帮助处理和响应实时事件。

4.串行通信:AT89C51支持串行通信协议,如UART协议。

它可以与其他设备进行数据通信,例如传感器或外部存储器。

5.低功耗模式:AT89C51具有多个节能模式,可最大限度地降低功耗。

—VCC:供电电压.之阳早格格创做—GND:交天.—P0心:P0心为一个8位漏级开路单背I/O心,每个管足可吸支8TTL门电流.当P1心的管足写“1”时,被定义为下阻输进.P0不妨用于中部步调数据保存器,它不妨被定义为数据/天点的第八位.正在FLASH编程时,P0心动做本码输出心,当FLASH举止校验时,P0输出本码,此时P0中部电位必须被推下.—P1心:P1心是一个里面提供上推电阻的8位单背I/O心,P1心慢冲器能交支输出4TTL门电流.P1心管足写进“1”后,电位被里面上推为下,可用做输进,P1心被中脚下推为矮电通常,将输出电流,那是由于里面上推的去由.正在FLASH编程战校验时,P1心动做第八位天点交支.—P2心:P2心为一个里面上推电阻的8位单背I/O心,P2心慢冲器可交支,输出4个TTL门电流,当P2心被写“1”时,其管足电位被里面上推电阻推下,且动做输进.动做输进时,P2心的管足电位被中部推矮,将输出电流,那是由于里面上推的去由.P2心当用于中部步调保存器或者16位天点中部数据保存器举止存与时,P2心输出天点的下八位.正在给出天点“1”时,它利用里面上推的劣势,当对于中部八位天点数据保存器举止读写时,P2心输出其特殊功能寄存器的实质.P2心正在FLASH编程战校验时交支下八位天点旗号战统造旗号.—P3心:P3心管足是8个戴里面上推电阻的单背I/O心,可交支输出4个TTL门电流.当P3心写进“1”后,它们被里面上推为下电仄,并用做输进.动做输进时,由于中脚下推为矮电仄,P3心将输出电流(ILL),也是由于上推的去由.P3心也可动做AT89C51的一些特殊功能心,如下所示:P3.0 RXD(串止输出心)P3.1 TXD(串止输出心)P3.2 0INT(中部中断0)P3.3 1INT(中部中断1)P3.4 T0(记时器0中部输进)P3.5 T1(记时器1中部输进)P3.6 W R(中部数据保存器写选通)P3.7 RD(中部数据保存器读选通)P3心共时为闪烁编程战编程校验交支一些统造旗号.—RST:复位输进.当振荡器复位器件时,要脆持RST足二个呆板周期的下电通常间.—PROGALE/:当考察中部保存器时,天点锁存允许的输出电仄用于锁存天点的职位字节.正在FLASH编程功夫,此引足用于输进编程脉冲.正在通常,ALE端以没有变的频次周期输出正脉冲旗号,此频次为振荡器频次的1/6.果此它可用做对于中部输出的脉冲或者用于定时脚段.然而要注意的是:每当用做中部数据保存器时,将跳过一个ALE脉冲.如念克制ALE的输出可正在SFR8EH天点上置0.此时, ALE 惟有正在实止MOVX,MOVC指令时ALE才起效率.其余,该引足被略微推下.如果微处理器正在中部实奇迹态ALE克制,置位无效.—PSEN:中部步调保存器的选通旗号.正在由中部步调保存器与址功夫,每个呆板周期PSEN二次灵验.但是正在考察中部数据保存器时,那二次灵验的PSEN旗号将没有出现.—VPPEA/:当EA脆持矮电通常,考察中部ROM;注意加稀办法1时,EA将里面锁定为RESET;当EA端脆持下电通常,考察里面ROM.正在FLASH编程功夫,此引足也用于施加12V编程电源(VPP).—XTAL1:反背振荡搁大器的输进及里面时钟处事电路的输进.—XTAL2:去自反背振荡器的输出.③里面结构框图如图10所示.图10 AT89C51的里面结构框图(3)AT89C51的基础支配如图11所示,正在X1战X2之间交一只石英振荡晶体形成了单片机的时钟电路,它另有另一种交法,是把中部振荡器的旗号曲交连交到XTAL1端,XTAL2端悬空没有必.AT89C51复位引足RST/VP通过片内一个施稀特触收器(压造噪声效率)与片内复位电路贯串,施稀特触收器的输出正在每一个呆板周期由复位电路采样一次.当振荡电路处事,而且正在RST引足上加一个起码脆持2个呆板周期的下电通常,便能使AT89C51完毕一次复位.复位没灵验率RAM的实质.复位后,PC指背0000H单元,使单片机从起初天点0000H单元开初沉新实止步调.所以,当单片机运止堕落或者加进死循环时,可按复位键沉新开用.。

—【1】VCC:供电电压。

—GND:接地。

—P0口:P0口为一个8位漏级开路双向I/O口,每个管脚可吸收8TTL门电流。

当P1口的管脚写“1”时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FLASH编程时,P0口作为原码输入口,当FLASH进行校验时,P0输出原码,此时P0外部电位必须被拉高。

—P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入“1”后,电位被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH 编程和校验时,P1口作为第八位地址接收。

—P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚电位被内部上拉电阻拉高,且作为输入。

作为输入时,P2口的管脚电位被外部拉低,将输出电流,这是由于内部上拉的缘故。

P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。

在给出地址“1”时,它利用内部上拉的优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。

P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

—P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。

当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。

作为输入时,由于外部下拉为低电平,P3口将输出电流(ILL),也是由于上拉的缘故。

P3口也可作为AT89C51的一些特殊功能口,如下所示:P3.0 RXD(串行输入口)P3.1 TXD(串行输出口)INT(外部中断0)P3.2 0INT(外部中断1)P3.3 1P3.4 T0(记时器0外部输入)P3.5 T1(记时器1外部输入)P3.6 WR(外部数据存储器写选通)P3.7 RD(外部数据存储器读选通)P3口同时为闪烁编程和编程校验接收一些控制信号。

![at89c51单片机各引角介绍[精华]](https://uimg.taocdn.com/df3246c685254b35eefdc8d376eeaeaad1f31602.webp)

(1)AT89C51的主要特性○18位微处理器和控制器,中央处理器是整个单片机的核心部件,能同时处理8位二进制数据或代码,CPU负责控制、指挥和调度整个单元系统协调的工作,完成运算和控制输入输出功能等操作。

○2内含一个布尔运算器,可直接对数据的位进行操作和运算,特别适用于逻辑控制。

○3内含4KB可重擦写的可编程闪烁程序存贮器(EEPROM)。

○4内含128*8位的数据存贮器(RAM)。

○54个8位(32根)双向且可独立寻址的I/O(输入输出)接口0P~3P。

○62个16位的计数器/定时器。

○7片内振荡器和时钟电路。

○8全双工方式的串行接口(DART)。

○9两级中断优先权的6个中断源/5个中断矢量的中断逻辑。

○10指令集有111条指令,其中64条为单周期指令,支持6种寻址方式。

○11最高时钟振荡频率可达12MHz,大部分指令执行时间为1us,乘、除指令为4us。

○12与MCS-51兼容,寿命为1000次写/擦循环,数据保留时间为10年。

○13低功耗的闲置和掉电模式,可编程串行通道,三级程序存储器锁定。

(2)引脚及功能AT89C51单片机为40脚双列直插式封装结构。

其引脚排列顺序及引脚符号如图4.1所示:图4.1 AT89C51管脚图各引脚功能如下:○1电源及接地GND:电源接地端。

Vcc:供电电压即正常运行和编程校验时为+5V电源(士10%)。

○2时钟及复位信号XTAL1:是片内振荡器反相放大器的输入及内部时钟工作电路的输入。

当采用外部振荡器为时钟源时,此脚必须接地。

XTAL2:是片内振荡器反相放大器的输出端,也是内部时钟发生器的输入端。

使用外部振荡器时,可由此脚引入外部时钟信号。

RST:复位信号输入端,高电平有效。

若此输入端保持2个机器周期(24个时钟振荡周期)以上的高电平,即可以将89C51完成复位操作。

此外,RST引脚的第二功能是VPD,即备用电源的输入端。

当主电源Vcc发生故障,降低到低电平规定值时,单片机自动将+5v电源接入RST端,为RAM提供备用电源,以保证存储在RAM中的信息不丢失,以使复电后能继续正常运行。

AT89C51单片机简介AT89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。

AT89C2051是一种带2K字节闪烁可编程可擦除只读存储器的单片机。

单片机的可擦除只读存储器可以反复擦除100次。

该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL 的AT89C51是一种高效微控制器,AT89C2051是它的一种精简版本。

AT89C单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

1.主要特性:·与MCS-51 兼容·4K字节可编程闪烁存储器寿命:1000写/擦循环数据保留时间:10年·全静态工作:0Hz-24Hz·三级程序存储器锁定·128*8位内部RAM·32可编程I/O线·两个16位定时器/计数器·5个中断源·可编程串行通道·低功耗的闲置和掉电模式·片内振荡器和时钟电路2.管脚说明:VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH编程和校验时,P1口作为第八位地址接收。

89C52引脚功能VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH编程和校验时,P1口作为第八位地址接收。

P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。

并因此作为输入时,P2口的管脚被外部拉低,将输出电流。

这是由于内部上拉的缘故。

P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。

在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。

P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。

当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。

作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。

P3口作为AT89C51的一些特殊功能口,管脚备选功能P3.0 RXD(串行输入口)P3.1 TXD(串行输出口)P3.2 /INT0(外部中断0)P3.3 /INT1(外部中断1)P3.4 T0(记时器0外部输入)P3.5 T1(记时器1外部输入)P3.6 /WR(外部数据存储器写选通)P3.7 /RD(外部数据存储器读选通)RST:复位输入。

at89c51引脚图及功能AT89C51是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4k bytes的可反复擦写的只读程序存储器(PEROM)和128 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器(CPU)和Flash存储单元,功能强大AT89C51单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。

主要性能参数:·与MCS-51产品指令系统完全兼容·4k字节可重擦写Flash闪速存储器·1000次擦写周期·全静态操作:0Hz-24MHz ·三级加密程序存储器·128×8字节内部RAM ·32个可编程I/O口线·2个16位定时/计数器·6个中断源·可编程串行UART通道·低功耗空闲和掉电模式功能特性概述:AT89C51提供以下标准功能:4k字节Flash闪速存储器,128字节内部RAM,32个I/O口线,两个16位定时/计数器,一个5向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,AT89C51可降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。

空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。

掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。

·P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口。

作为输出口用时,每位能吸收电流的方式驱动8个TTL逻辑门电路,对端口写“1”可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

在FIash编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

at89c51引脚图及功能AT89C51是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4k bytes的可反复擦写的只读程序存储器(PEROM)和128 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器(CPU)和Flash存储单元,功能强大AT89C51单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。

主要性能参数:·与MCS-51产品指令系统完全兼容·4k字节可重擦写Flash闪速存储器·1000次擦写周期·全静态操作:0Hz-24MHz ·三级加密程序存储器·128×8字节内部RAM ·32个可编程I/O口线·2个16位定时/计数器·6个中断源·可编程串行UART通道·低功耗空闲和掉电模式功能特性概述:AT89C51提供以下标准功能:4k字节Flash闪速存储器,128字节内部RAM,32个I/O口线,两个16位定时/计数器,一个5向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,AT89C51可降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。

空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。

掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。

·P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口。

作为输出口用时,每位能吸收电流的方式驱动8个TTL逻辑门电路,对端口写“1”可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

在FIash编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

AT89C51单片机简介AT89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。

AT89C2051是一种带2K字节闪烁可编程可擦除只读存储器的单片机。

单片机的可擦除只读存储器可以反复擦除100次。

该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89C51是一种高效微控制器,AT89C2051是它的一种精简版本。

AT89C单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

1.主要特性:·与MCS-51 兼容·4K字节可编程闪烁存储器寿命:1000写/擦循环数据保留时间:10年·全静态工作:0Hz-24Hz·三级程序存储器锁定·128*8位内部RAM·32可编程I/O线·两个16位定时器/计数器·5个中断源·可编程串行通道·低功耗的闲置和掉电模式·片内振荡器和时钟电路2.管脚说明:VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH编程和校验时,P1口作为第八位地址接收。

89c51引脚图及功能89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。

89C2051是一种带2K字节闪烁可编程可擦除只读存储器的单片机。

单片机的可擦除只读存储器可以反复擦除100次。

该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的89C51是一种高效微控制器,89C2051是它的一种精简版本。

89C单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

1.主要特性:·与MCS-51 兼容·4K字节可编程闪烁存储器寿命:1000写/擦循环数据保留时间:10年·全静态工作:0Hz-24Hz·三级程序存储器锁定·128*8位内部RAM·32可编程I/O线·两个16位定时器/计数器·5个中断源·可编程串行通道·低功耗的闲置和掉电模式·片内振荡器和时钟电路2.管脚说明:VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH编程和校验时,P1口作为第八位地址接收。

—VCC:供电电压。

—GND:接地。

—P0口:P0口为

一个8位漏级开路双

向I/O口,每个管脚可

吸收8TTL门电流。

当P1口的管脚写“1”时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FLASH编程时,P0口作为原码输入口,当FLASH进行校验时,P0输出原码,此时P0外部电位必须被拉高。

—P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入“1”后,电位被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH 编程和校验时,P1口作为第八位地址接收。

—P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚电位被内部上拉电阻拉高,且作为输入。

作为输入时,P2口的管脚电位被外部拉低,将输出电流,这是由于内部上拉的缘故。

P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。

在给出地址“1”时,它利用内部上拉的优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。

P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

—P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL

门电流。

当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。

作为输入时,由于外部下拉为低电平,P3口将输出电流(ILL),也是由于上拉的缘故。

P3口也可作为AT89C51的一些特殊功能口,如下所示:

P3.0 RXD(串行输入口)

P3.1 TXD(串行输出口)

P3.2 0

INT(外部中断0)

P3.3 1

INT(外部中断1)

P3.4 T0(记时器0外部输入)

P3.5 T1(记时器1外部输入)

P3.6 WR(外部数据存储器写选通)

P3.7 RD(外部数据存储器读选通)

P3口同时为闪烁编程和编程校验接收一些控制信号。

—RST:复位输入。

当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

—PROG

ALE/:当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。

在FLASH编程期间,此引脚用于输入编程脉冲。

在平时,ALE 端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。

因此它可用作对外部输出的脉冲或用于定时目的。

然而要注意的是:每当用作外部数据存储器时,将跳过一个ALE脉冲。

如想禁止ALE的输出可在SFR8EH地址上置0。

此时, ALE 只有在执行MOVX,MOVC指令时ALE才起作用。

另外,该引脚被略微拉高。

如果微处理器在外部执行状态ALE禁止,置位无效。

—PSEN:外部程序存储器的选通信号。

在由外部程序存储器取址期间,每个机器周期PSEN两次有效。

但在访问外部数据存储器时,这两次有效的PSEN 信号将不出现。

—VPP

EA/:当EA保持低电平时,访问外部ROM;注意加密方式1时,EA将内部锁定为RESET;当EA端保持高电平时,访问内部ROM。

在FLASH编程期间,此

引脚也用于施加12V编程电源(VPP)。

—XTAL1:反向振荡放大器的输入及内部时钟工作电路的输入。

—XTAL2:来自反向振荡器的输出。

③内部结构框图如图10所示。

图10 AT89C51的内部结构框图

(3)AT89C51的基本操作

如图11所示,在X1和X2之间接一只石英振荡晶体构成了单片机的时钟电路,它还有另一种接法,是把外部振荡器的信号直接连接到XTAL1端,XTAL2端悬空不用。

AT89C51复位引脚RST/VP通过片内一个施密特触发器(抑制噪声作用)与片内复位电路相连,施密特触发器的输出在每一个机器周期由复位电路采样一次。

当振荡电路工作,并且在RST引脚上加一个至少保持2个机器周期的高电平时,就能使AT89C51完成一次复位。

复位不影响RAM的内容。

复位后,PC指向0000H单元,使单片机从起始地址0000H单元开始重新执行程序。

所以,当单片机运行出错或进入死循环时,可按复位键重新启动。