n阱CMOS芯片制作工艺设计

- 格式:ppt

- 大小:450.00 KB

- 文档页数:25

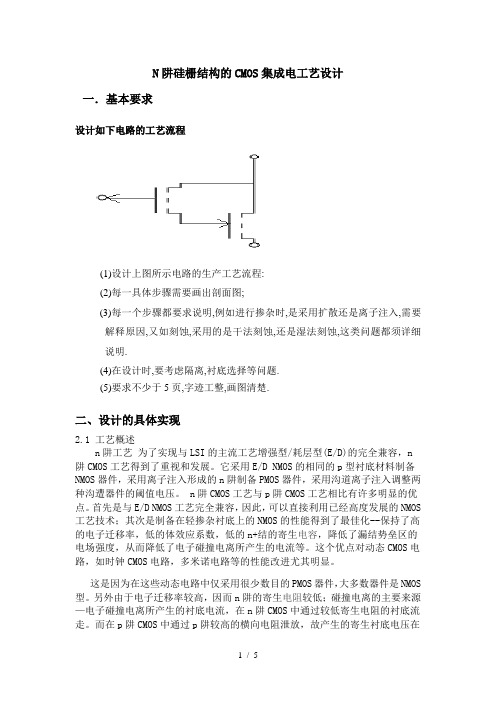

N阱硅栅结构的CMOS集成电工艺设计一.基本要求设计如下电路的工艺流程(1)设计上图所示电路的生产工艺流程:(2)每一具体步骤需要画出剖面图;(3)每一个步骤都要求说明,例如进行掺杂时,是采用扩散还是离子注入,需要解释原因,又如刻蚀,采用的是干法刻蚀,还是湿法刻蚀,这类问题都须详细说明.(4)在设计时,要考虑隔离,衬底选择等问题.(5)要求不少于5页,字迹工整,画图清楚.二、设计的具体实现2.1 工艺概述n阱工艺为了实现与LSI的主流工艺增强型/耗层型(E/D)的完全兼容,n 阱CMOS工艺得到了重视和发展。

它采用E/D NMOS的相同的p型衬底材料制备NMOS器件,采用离子注入形成的n阱制备PMOS器件,采用沟道离子注入调整两种沟遭器件的阈值电压。

n阱CMOS工艺与p阱CMOS工艺相比有许多明显的优点。

首先是与E/D NMOS工艺完全兼容,因此,可以直接利用已经高度发展的NMOS 工艺技术;其次是制备在轻掺杂衬底上的NMOS的性能得到了最佳化--保持了高的电子迁移率,低的体效应系数,低的n+结的寄生电容,降低了漏结势垒区的电场强度,从而降低了电子碰撞电离所产生的电流等。

这个优点对动态CMOS电路,如时钟CMOS电路,多米诺电路等的性能改进尤其明显。

这是因为在这些动态电路中仅采用很少数目的PMOS器件,大多数器件是NMOS 型。

另外由于电子迁移率较高,因而n阱的寄生电阻较低;碰撞电离的主要来源—电子碰撞电离所产生的衬底电流,在n阱CMOS中通过较低寄生电阻的衬底流走。

而在p阱CMOS中通过p阱较高的横向电阻泄放,故产生的寄生衬底电压在n阱CMOS中比p阱要小。

在n阱CMOS中寄生的纵向双极型晶体管是PNP型,其发射极电流增益较低,n阱CMOS结构中产生可控硅锁定效应的几率较p阱为低。

由于n阱CMOS的结构的工艺步骤较p阱CMOS简化,也有利于提高集成密度.例如由于磷在场氧化时,在n阱表面的分凝效应,就可以取消对PMOS的场注入和隔离环。

试简述n陷cmos晶体管的的工艺流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!简述n沟道互补金属氧化物半导体(nMOSFET)的工艺流程在微电子学领域,n沟道互补金属氧化物半导体(nMOSFET)晶体管是构建现代集成电路的基础组件之一。

工艺步骤工艺名称工艺目的设计目标结构参数工艺方法工艺条件1 衬底选择衬底电阻率cm⋅Ω50晶向(100)2 一次氧化(外延)为n阱形成提供掩蔽厚度:1.5um 干氧—湿氧—干氧干氧1200度,10min湿氧1200度,30min干氧1200度10min3 一次光刻为磷提供掩蔽膜电子束曝光正胶4 一次离子注入注入形成n阱离子注入kevE40=2151057.1-⨯=cmQ5 一次扩散热驱入达到n阱所需深度结深:5.65um方块电阻:Ω690有限表面源扩散CT01150=ht5.4=6 二次氧化作为氮化硅膜的缓冲层膜厚膜厚600Å干氧氧化1200T C=9mint=7 氮化硅膜淀积作为光刻有源区的掩蔽膜膜厚1000ÅLPCVD8 二次光刻为磷扩散提供窗口电子束曝光正胶9 场氧一利用氮化硅的掩蔽,在没有氮化硅、经P+离子注入的区域生成一层场区氧化层厚度1000Å湿氧氧化1200T C=,95℃水温。

10 三次光刻除N阱中有源区的氮化硅和二氧化硅层电子束曝光正胶11 场氧二生长场氧化层厚度约为1微米湿氧氧化1200T C=12 栅极氧化形成栅极氧化层厚度400Å干氧1200T C=62min.t=13 多晶硅淀积淀积多晶硅层厚度4000ÅLPCVD T=600℃10mint=14 四次光刻形成NMOS多晶硅栅,并刻出NMOS有源区的扩散窗口电子束曝光正胶15 三次离子注入形成NMOS有源漏区表面浓度320101-⨯cm结深mμ3.0注入P+kevkev80~40E=16 五次光刻形成PMOS多晶硅栅,并刻出PMOS有源区的扩散窗口电子束曝光正胶2-161015.8cmQ⨯=17 四次离子注入形成PMOS有源漏区表面浓度320101-⨯cm结深mμ3.0注入B+2-171021.2cmQ⨯=kevkev45~25E=18 淀积磷硅玻璃保护LPCVD600T C=10mint=19 六次光刻刻金属化的接触孔电子束曝光正胶20 蒸铝、刻铝淀积Al-Si合金,并形成集成电路的最后互连溅射。

N 阱硅栅CMOS 集成电路制造工艺的主要流程(1)生长一层SiO 2。

(2)在SiO 2上涂光刻胶,光刻N 阱掺杂窗口(一次光刻)。

(3)用HF 刻蚀窗口处的SiO 2,去胶。

(4)在窗口处注入N 型杂质。

(5)形成N 阱,去除硅片上的SiO 2。

(6)生长一层SiO 2,再生长一层Si 3N 4。

光刻场区(二次光刻),刻蚀场区的Si 3N 4,去胶。

由于Si 3N 4和Si 之间的应力较大,而SiO 2与Si 和Si 3N 4之间的应力较小,所以用SiO 2作为过渡层。

(7)生长场区SiO 2(场氧)。

CMOS 工艺之所以不象NMOS 工艺那样直接生长场氧,一是因为CMOS 工艺比NMOS 工艺出现得晚,更先进;二是因为生长场氧时间很长,会消耗很多硅,这样会使有源区边缘产生很高的台阶,给以后台阶覆盖带来困难,台阶太高会产生覆盖死角。

(8)去除Si 3N 4和有源区处的SiO 2。

(9)重新生长一层薄薄的SiO 2(栅氧)。

(10)生长一层多晶硅。

(11)光刻多晶硅栅极(三次光刻)。

(12)刻蚀栅极以外的多晶硅,去胶。

(13)光刻P +离子注入窗口(四次光刻),刻蚀窗口处的SiO 2,去胶。

在窗口处注入P 型杂质,形成PMOS 的源漏区和衬底欧姆接触。

生长SiO 2。

(14)光刻N +离子注入窗口(五次光刻),刻蚀窗口处的SiO 2,去胶。

在窗口处注入N 型杂质,形成NMOS 的源漏区和阱欧姆接触。

(15)生长一层SiO 2。

(16)光刻接触孔(六次光刻),刻蚀接触孔处的SiO 2,去胶。

(17)生长一层金属,光刻金属引线(七次光刻)。

(18)刻蚀引线外的金属,去胶。

(19)淀积钝化层。