专题:存储器与接口设计

- 格式:doc

- 大小:60.50 KB

- 文档页数:4

单片机与外部存储器的接口设计与应用单片机作为一种微型计算机的核心处理器,通常具有较小的存储容量,为了扩展其存储能力和功能,外部存储器成为了必不可少的组成部分。

本文将重点讨论单片机与外部存储器的接口设计与应用,希望能够为相关领域的工程师和爱好者提供一些参考和帮助。

一、外部存储器概述外部存储器是指连接在单片机之外的存储器设备,一般具有较大的存储容量和高速的数据传输能力。

常见的外部存储器包括闪存、SD卡、EEPROM等,不同的存储器设备在容量、存取速度、寿命等方面有所不同,需要根据具体需求进行选择。

二、接口标准单片机与外部存储器之间的接口可以通过多种标准实现,常见的接口标准有SPI、I2C、UART等。

其中,SPI(Serial Peripheral Interface)是一种全双工的同步串行数据总线,具有高速传输率和灵活的接口设计,适用于连接高速外部存储器。

I2C(Inter-Integrated Circuit)是一种双线制的串行总线,适用于连接低速外部存储器。

UART(Universal Asynchronous Receiver/Transmitter)是一种异步串行通信接口,适用于连接需要长距离传输的外部存储器。

三、接口设计在设计单片机与外部存储器的接口时,首先需要了解外部存储器的通讯协议和工作方式,选择合适的接口标准。

然后根据接口标准的要求设计连接电路和通讯协议,包括时序控制、数据传输方式、地址传输等。

接口设计需要考虑到时序稳定性、数据完整性和通讯效率等因素,确保单片机和外部存储器之间能够正常通讯和数据传输。

四、应用案例以SPI接口为例,设计一款单片机与外部SPI闪存的接口电路。

首先连接单片机的SPI主机接口和外部闪存的SPI从机接口,设置好时钟频率和数据传输模式。

然后通过单片机编程控制SPI总线进行数据读写操作,实现对外部闪存的存储管理和数据传输。

在应用中可以实现数据的存储、读取、更新等功能,提高单片机的存储容量和功能性。

单片机外部存储器接口设计与应用摘要:本文将深入探讨单片机外部存储器接口设计与应用。

首先,介绍了单片机和外部存储器的基本概念和原理。

然后,详细讨论了不同类型的外部存储器接口的设计和应用,包括并行接口、串行接口以及SPI接口。

最后,给出了一些实际应用案例,并讨论了各种接口的优缺点。

关键词:单片机、外部存储器、接口设计、应用1. 引言单片机是一种具备处理器、存储器和输入输出设备等功能的微型计算机,广泛应用于各行各业。

由于单片机内部存储器大小有限,无法满足大规模数据存储的需求,因此常需要与外部存储器进行接口设计与应用。

2. 单片机与外部存储器2.1 单片机的概念单片机是一种内部集成了CPU、ROM、RAM、IO口和计时器等基本部件的微型计算机系统。

它体积小、功耗低、成本低廉,在工业控制、仪器设备、消费电子等领域得到广泛应用。

2.2 外部存储器的概念外部存储器是与单片机相连的存储设备,用于扩展单片机的存储容量。

常见的外部存储器包括EPROM、EEPROM、Flash、SD卡等。

3. 外部存储器接口设计3.1 并行接口并行接口是一种数据在多个信号线上同时传输的接口方式。

它具有传输速度快、可靠性高的特点,适合于大容量数据的传输。

并行接口的设计需要考虑地址线、数据线和控制线的布线和连接方式。

3.2 串行接口串行接口是一种数据逐位传输的接口方式。

它相对于并行接口来说,线路复杂度低、成本较低,适合于远距离传输。

串行接口的设计主要包括通信协议的选择、波特率的设置等。

3.3 SPI接口SPI(Serial Peripheral Interface)接口是一种串行同步通信接口,常用于单片机与外围设备之间的通信。

SPI接口具有传输速度快、可靠性高、接口简单的特点,适用于多种外围设备的接口设计与应用。

4. 外部存储器接口的应用4.1 数据日志记录器数据日志记录器是一种能够存储大量数据的设备,广泛应用于气象测量、环境监控等领域。

单片机中的外部存储器接口设计与优化探讨近年来,随着科技的迅猛发展,单片机逐渐成为嵌入式系统中不可或缺的组成部分。

而在单片机的设计过程中,外部存储器接口的设计与优化成为了一个至关重要的问题。

本文将对单片机中的外部存储器接口进行探讨,包括其设计原理、常见的接口类型及其优化方法。

一、外部存储器接口设计原理外部存储器接口设计的目的是实现单片机与外部存储器之间的数据交换。

为了高效地使用外部存储器,并满足实际应用的需求,需要一种高速、稳定、可靠的接口方案。

在单片机中,外部存储器接口采用的最常见的方式是总线接口。

总线接口可分为数据总线、地址总线和控制总线三部分。

数据总线用于传输数据,地址总线用于传输外部存储器的地址,控制总线用于传输读写控制信号。

单片机通过控制总线发出读写命令,各个存储器通过地址总线传输地址,数据则通过数据总线进行传输。

这种总线接口的设计能够有效地提高单片机与外部存储器之间的数据传输速度和稳定性。

除了总线接口,还有一些专用的接口类型,常见的有SPI(Serial Peripheral Interface)、I2C(Inter-Integrated Circuit)和SD卡接口等。

这些接口类型在不同的应用场景中具有不同的特点和优势。

例如,SPI接口具有高速率、长距离传输和灵活性等优势,适用于对数据传输速度要求高的应用场景;而I2C接口则适用于连接多个设备,具有简化设计、节省IO口和支持点对点或多主从通信等特点。

二、常见的外部存储器接口类型1. 并行接口并行接口是一种常见且广泛应用的外部存储器接口类型。

通过同时传送多个数据位,使得数据传输速度更快。

并行接口的数据线和外部存储器的数据线一一对应,传输的数据位数较多,相对而言,传输速度较快。

然而,并行接口的接线比较复杂,需要较多的引脚,对布局设计和电路连接要求较高。

2. 串行接口串行接口是一种通过逐位传输数据的接口类型。

相比于并行接口,串行接口在传输速度上要慢一些。

计算机硬件设计中的存储器接口设计技术计算机硬件设计中的存储器接口设计技术是计算机系统中极为重要的一部分。

存储器接口的设计直接决定了计算机系统的性能和可靠性。

本文将探讨计算机硬件设计中的存储器接口设计技术,从存储器接口的基本原理、接口类型、设计要求等方面进行详细介绍。

存储器接口可以被定义为计算机系统中连接主存和CPU的桥梁,它负责将CPU的读写指令转换成主存的操作信号。

存储器接口的设计需要考虑如何提高数据传输的速度、提高系统的存取效率、确保数据的安全性等方面的要求。

在存储器接口的设计中,有几个关键的技术需要重点考虑。

首先是总线的设计,总线是CPU和存储器之间的数据通道,它需要能够支持高速数据传输和多设备的连接。

在总线的设计中,需要考虑数据的传输速度、总线的宽度、数据的并行传输还是串行传输等因素。

另一个关键的技术是存储器的映射方式。

存储器的映射方式可以分为直接映射、全映射和组相联映射三种。

在直接映射方式中,CPU的内存地址直接对应存储器的物理地址;在全映射方式中,CPU的内存地址可以映射到存储器的任意位置;而在组相联映射方式中,CPU的内存地址需要经过一定的计算才能映射到存储器的物理地址。

不同的映射方式在性能和复杂度上都有所不同,需要根据具体的应用场景选择合适的映射方式。

此外,在存储器接口设计中,还需要考虑存储器的时序控制和数据校验等技术。

时序控制是指存储器接口需要遵循一定的时序要求,保证存储器的读写操作能够按照正确的顺序进行。

数据校验是指在数据传输过程中需要确保数据的准确性,通常通过奇偶校验、循环冗余校验等技术来实现。

综上所述,计算机硬件设计中的存储器接口设计技术是非常重要的。

通过合理设计存储器接口,可以提高计算机系统的性能和可靠性。

在实际应用中,需要根据具体的需求和系统架构选择合适的存储器接口设计技术,以满足不同应用场景的需求。

存储器接口设计技术的不断创新和发展也是推动计算机硬件技术进步的关键之一。

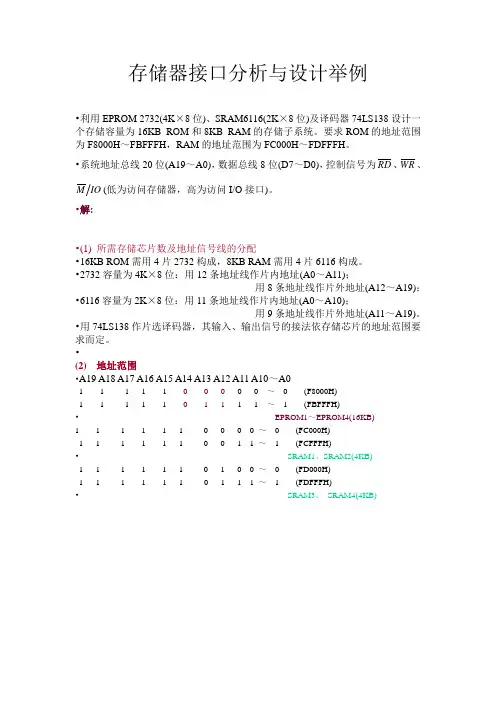

存储器接口分析与设计举例•利用EPROM 2732(4K×8位)、SRAM6116(2K×8位)及译码器74LS138设计一个存储容量为16KB ROM和8KB RAM的存储子系统。

要求ROM的地址范围为F8000H~FBFFFH,RAM的地址范围为FC000H~FDFFFH。

•系统地址总线20位(A19~A0),数据总线8位(D7~D0),控制信号为RD、WR、M IO(低为访问存储器,高为访问I/O接口)。

•解:•(1) 所需存储芯片数及地址信号线的分配•16KB ROM需用4片2732构成,8KB RAM需用4片6116构成。

•2732容量为4K×8位:用12条地址线作片内地址(A0~A11);用8条地址线作片外地址(A12~A19);•6116容量为2K×8位:用11条地址线作片内地址(A0~A10);用9条地址线作片外地址(A11~A19)。

•用74LS138作片选译码器,其输入、输出信号的接法依存储芯片的地址范围要求而定。

•(2) 地址范围•A19 A18 A17 A16 A15 A14 A13 A12 A11 A10~A01 1 1 1 1 0 0 00 0 ~0 (F8000H)1 1 1 1 1 0 1 1 1 1 ~ 1 (FBFFFH)•EPROM1~EPROM4(16KB)1 1 1 1 1 1 0 0 0 0 ~0 (FC000H)1 1 1 1 1 1 0 0 1 1 ~ 1 (FCFFFH)•SRAM1、SRAM2(4KB)1 1 1 1 1 1 0 1 0 0 ~0 (FD000H)1 1 1 1 1 1 0 1 1 1 ~ 1 (FDFFFH)•SRAM3、SRAM4(4KB)前例逻辑图。

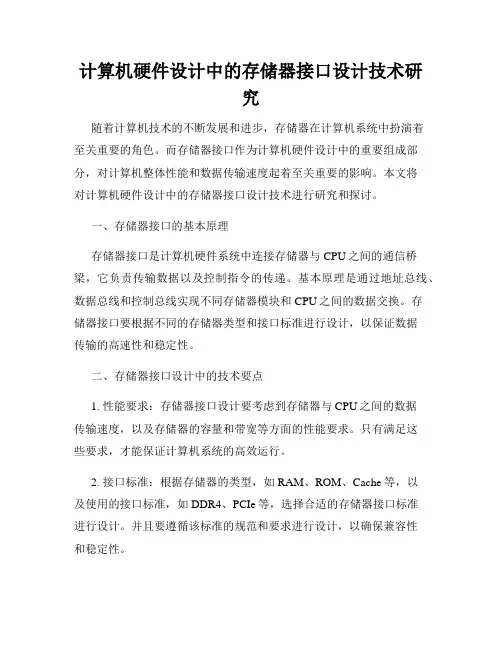

计算机硬件设计中的存储器接口设计技术研究随着计算机技术的不断发展和进步,存储器在计算机系统中扮演着至关重要的角色。

而存储器接口作为计算机硬件设计中的重要组成部分,对计算机整体性能和数据传输速度起着至关重要的影响。

本文将对计算机硬件设计中的存储器接口设计技术进行研究和探讨。

一、存储器接口的基本原理存储器接口是计算机硬件系统中连接存储器与CPU之间的通信桥梁,它负责传输数据以及控制指令的传递。

基本原理是通过地址总线、数据总线和控制总线实现不同存储器模块和CPU之间的数据交换。

存储器接口要根据不同的存储器类型和接口标准进行设计,以保证数据传输的高速性和稳定性。

二、存储器接口设计中的技术要点1. 性能要求:存储器接口设计要考虑到存储器与CPU之间的数据传输速度,以及存储器的容量和带宽等方面的性能要求。

只有满足这些要求,才能保证计算机系统的高效运行。

2. 接口标准:根据存储器的类型,如RAM、ROM、Cache等,以及使用的接口标准,如DDR4、PCIe等,选择合适的存储器接口标准进行设计。

并且要遵循该标准的规范和要求进行设计,以确保兼容性和稳定性。

3. 数据传输方式:根据存储器接口标准的要求,选择合适的数据传输方式,如并行传输方式或串行传输方式。

并采用适当的数据传输协议和编码方式,以确保数据传输的准确性和稳定性。

4. 时序控制:存储器接口设计中的关键问题是时序控制。

通过合理的时序设计,可以减少数据传输的延迟和传输错误的概率。

同时,还要考虑到存储器接口与其他外设接口的协同工作,以避免冲突和数据丢失。

三、存储器接口设计的优化技术1. 性能优化:通过增加总线带宽、减少数据传输延迟和优化数据传输协议等方式,提高存储器接口的性能。

同时,还可以采用读写缓存和预取技术等方法,优化数据访问和读写速度。

2. 安全性优化:存储器接口设计需要考虑到数据的安全性和完整性。

可以采用错误检测和纠正技术,如CRC校验等,以保证数据传输的正确性和可靠性。

专题:存储器与接口设计

存储器接口类型可分为:异步存储器接口和同步存储器接口2大类型

异步存储器接口类型是最常见的,也是我们最熟知的,MCU一般均采用此类接口。

相应的存储器有:SRAM、Flash、NvRAM……等,另外许多以并行方式接口的模拟/数字I/O器件,如A/D、D/A、开入/开出等,也采用异步存储器接口形式实现。

同步存储接口相对比较陌生,一般用于高档的微处理器中,TI DSP中只有C55x 和C6000系列DSP包含同步存储器接口。

相应的存储器有:同步静态存储器:SBSRAM和ZBTSRAM,同步动态存储器: SDRAM,同步FIFO等。

SDRAM可能是我们最熟知的同步存储器件,它被广泛用作PC机的内存。

C2000、C3x、C54x系列DSP只提供异步存储器接口,所以它们只能与异步存储器直接接口,如果想要与同步存储器接口,则必须外加相应的存储器控制器,从电路的复杂性和成本的考虑,一般不这么做。

C55x、C6000系列DSP不仅提供了异步存储器接口,为配合其性能还提供了同步存储器接口。

C55x和C6000系列DSP的异步存储器接口主要用于扩展Flash和模拟/数字I/O,Flash主要用于存放程序,系统上电后将Flash中的程序加载到DSP片内或片外的高速RAM 中,这一过程我们称为BootLoader同步存储器接口主要用于扩展外部高速数据或程序RAM,如SBSRAM、 ZBTSRAM或SDRAM等。

现在的问题是如何设计DSP系统的外部存储器电路,即DSP如何正确地与各种类型的存储器芯片接口。

在DSP外部存储器电路设计中经常会遇到下列一些问题:DSP提供的外部存储器接口信号与存储器芯片所需要的接口信号不完全一致某

些DSP支持多种数据宽度的访问,如8/16/32位数据宽度等,存储器电路中如何实现?数据、地址线在PCB布线时,为了走线方便,经常会进行等效交换,哪些存储器可以作等效交换、哪些不行?

下面我们将按存储器类型分别来解答这些问题

异步存储器:Flash

对于flash,读操作与SRAM相同;擦除和写入操作以命令序列形式给出,厂商不同,命令序列可能稍有不同写入命令序列后,Flash自动执行相应操作,直到完成,随后自动转为读状态。

在完成相应操作前,读Flash得到操作是否完成的状态信息,而非存储单元数据.

对于flash,因为擦除跟写入操作以命令序列形式给出,可以对进行编程,包括两种方式:

1、在线,load2段程序,把要烧写的程序当作文件写入到Flash中

2、离线,通过JTAG烧写

3.3V、16位宽度的、工业标准Flash有4种,它们的引脚兼容,均为48引脚的TSOP封装在PCB布线时,以最大容量1M×16位Flash布线,则可根据容量需要安装如何一种FlashFlash的数据和地址线不可以等效交换BootLoader考虑Flash应定位于特殊的位置,设计时应参考相应器件的数据手册

1、VC33,Flash应定位在PAGE0的1000H、或PAGE1的400000H、或PAGE3的FFF000H,可支持8/16/32位数据宽度

2、C54x系列DSP,Flash应定位在数据存储空间的8000H~FFFFH,可支持8/16位数据宽度

3、C55x系列DSP,Flash应定位在CE1存储空间的200000H,C5509只支持16位宽度,而C5510可支持8/16/32位数据宽度

4、C620x/C670x系列DSP,Flash应定位在CE1存储空间,大小为64K字节,支持8/16/32位数据宽度,只能是Little Endian格式

5、C621x/C671x系列DSP,Flash应定位在CE1存储空间,大小为1K字节,支持8/16/32位数据宽度,可以是Little Endian格式,也可以是Big Endian 格式

6、C64x系列DSP,Flash应定位在EMIFB的CE1存储空间,大小为1K字节,仅支持8位数据宽度,可以是Little Endian格式,也可以是Big Endian格式

常用的Flash

SST39VF400A-70-4C-EK,256K×16位、3.3V、70ns

SDRAM

SDRAM,即Synchronous DRAM(同步动态随机存储器),曾经是PC电脑上最为广泛应用的一种内存类型,即便在今天SDRAM仍旧还在市场占有一席之地。

既然是“同步动态随机存储器”,那就代表着它的工作速度是与系统总线速度同步的。

SDRAM内存又分为PC66、PC100、PC133等不同规格,而规格后面的数字就代表着该内存最大所能正常工作系统总线速度,比如PC100,那就说明此内存可以在系统总线为100MHz的电脑中同步工作。

与系统总线速度同步,也就是与系统时钟同步,这样就避免了不必要的等待周期,减少数据存储时间。

同步还使存储控制器知道在哪一个时钟脉冲期由数据请求使用,因此数据可在脉冲上升期便开始传输。

SDRAM采用3.3伏工作电压,168Pin 的DIMM接口,带宽为64位。

SDRAM不仅应用在内存上,在显存上也较为常见。

SDRAM工作过程:

1. 上电稳定后经过8个刷新周期,进入模式寄存器设置(MRS),确定芯片的工作模式,CL,BL,突发传输方式。

2. 行有效,同时进行了片选和BANK选择工作。

CS RAS有效 CAS WE无效,地址线和BA上选择相应的BANK和行(有些文档中将这两种都归为地址线,BA 为地址的最高位)。

3. 列读写,当行有效后,选择需要的列进行读或写操作,CAS有效,RAS无效,地址线上为列地址,WE信号决定了究竟是读还是写操作。

SDRAM中的一些重要知识:

1. tRCD,RAS到CAS的延迟,也就是说当行有效后不能在下一个时钟周期就进行读写操作,而是要等待一定的时间,这个时间就是tRCD,一般为2个或3个时钟周期。

2. CL,读取潜伏期,读取过程中当CAS到达后并不能马上将数据输出到IO 总线上,而是要经过一定的时间,这个时间就是CL,它是由于信号要经过放大等处理造成的,它的数值可以在MRS中改变,单位是芯片时钟周期。

3. 写入操作是没有任何延迟的,在CAS发出后数据就可以发出SDRAM

4. 利用设置BL可以连续传送一组数据而不需要给出相应的地址只要给出第一个数据的地址就可以了。

5. 预充电过程,当选择同一BANK的不同行的时候就要进行预充电操作,一般为2个时钟周期。

6. 刷新过程分两种,一种是自动刷新还有一种是自刷新。

提高SDRAM效率必须要尽量减少以上提到的各种时间造成数据的延迟。

令读 1 00h/ 01h(1) -

读 2 50h -

读

ID

90h -

复位FFh - O 页编

程

80h 10h

块擦

除

60h D0h

读状

态

70h - O

注 1. 00h命令定义了寄存器的第一个半页

的起始地址

01h命令定义了寄存器的第二个半页的起

始地址

当使用 01h命令访问完寄存器的第二个

半页的数据后

起始指针在下个周期自动移至寄存器的

第一

个半页 00h

注意除表 1中定义的命令外禁止输入任何未定义的命令。