第5章存储器原理与接口

- 格式:ppt

- 大小:2.13 MB

- 文档页数:58

第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个?逻辑地址呢?答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。

第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成它们的主要功能是什么答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处8086CPU内部的并行操作体现在哪里答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个逻辑地址呢答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。

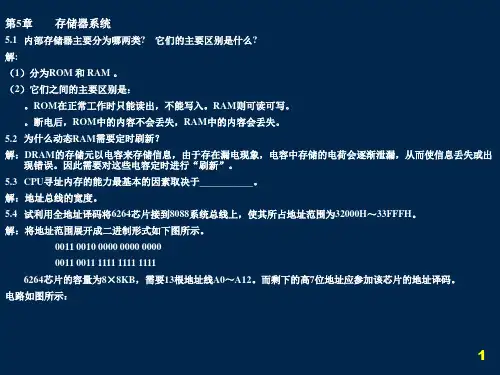

微机原理与接⼝技术第五章课后答案第五章参考答案1.简述SRAM 芯⽚与DRAM 芯⽚的共同点与不同点。

答:SRAM 与DRAM 的共同点:都属于随机存取存储器,具有易失性。

SRAM 与DRAM 的共同点:SRAM 利⽤双稳态触发器电路保存信息,集成度⽐DRAM 低,功耗⽐DRAM ⼤;DRAM 利⽤MOS 管栅极和源极之间的极间电容C 保存信息,需要刷新电路保证信息较长时间保存。

2.叙述ROM 芯⽚的常见分类,各种ROM 芯⽚的特点及其适⽤场合。

答:ROM 的常⽤分类结果:掩膜ROM :⽣产完成的芯⽚已保存了信息,保存的信息⽆法修改,适⽤于⼤批量的定型产品中。

PROM :PROM 可以⼀次写⼊信息,⼀旦写⼊⽆法更改,适⽤于⼩批量的定型产品中。

EPROM :紫外线擦除可多次编程的存储器,适⽤于新产品的开发。

EEPROM :电擦除可多次编程的存储器,适⽤于需要在线修改的场合。

3.利⽤4⽚6116(2K ×8位)芯⽚设计连续存储器,采⽤全地址译码。

设起始地址为60000H ,求存储器的最后⼀个单元地址。

答:存储器的最后⼀个单元地址为:61FFFH.4.⽤6264 RAM (8K ×8位)芯⽚构成256K 字节存储器系统,需要多少⽚6264芯⽚20位地址总线中有多少位参与⽚内寻址有多少位可⽤作⽚选控制信号答:需要32⽚6264芯⽚。

20位地址总线中有13位参与⽚内寻址;有7位可⽤作⽚选控制信号。

5.某微机系统中ROM 区有⾸地址为9000H ,末地址为FFFFH ,求其ROM 区域的存储容量。

答:其ROM 区域的存储容量为28K 。

6.在8088CPU 的系统中扩展32K 字节的RAM ,其扩充存储空间的起始地址为08000H 。

设系统的地址总线为A 19~A 0,数据总线为D 7~D 0,存储器芯⽚选⽤6264。

利⽤74LS138译码器设计译码电路,并画出扩充的存储器系统的连线图。

第2章微型计算机基础2.8 在执行指令期间,BIU能直接访问存储器吗?为什么?解:可以.因为EU和BIU可以并行工作,EU需要的指令可以从指令队列中获得,这时BIU预先从存储器中取出并放入指令队列的。

在EU执行指令的同时,BIU 可以访问存储器取下一条指令或指令执行时需要的数据。

2.9 8086与8088CPU的主要区别有哪些?解:主要区别有以下几点:①8086的外部数据总线有16位,而8088的外部数据总线只有8位。

②8086指令队列深度为6个字节,而8088的指令队列深度为4个字节.③因为8086的外部数据总线有16位,故8086每个总线周期可以存取两个字节.而8088的外部数据总线因为只有8位,所以每个总线周期只能存取1个字节.④个别引脚信号的含义稍有不同.2.10 解:(1)要利用信号线包括WR#、RD#、IO/M#、ALE 以及AD0~AD7、A8~A19。

(2)同(1)。

(3)所有三态输出的地址信号、数据信号和控制信号均置为高阻态。

2.11解:在每个总线周期的T3的开始处若READY 为低电平,则CPU在T3后插入一个等待周期TW。

在TW的开始时刻,CPU还要检查READY状态,若仍为低电平,则再插入一个TW 。

此过程一直进行到某个TW开始时,READY已经变为高电平,这时下一个时钟周期才转入T4。

可以看出,插入TW周期的个数取决于READY电平维持的时间。

2.14 解:通用寄存器包含以下8个寄存器:AX、BX、CX和DX寄存器一般用于存放参与运算的数据或运算的结果。

除此之外:AX:主要存放算术逻辑运算中的操作数,以及存放I/O操作的数据。

BX:存放访问内存时的基地址。

CX:在循环和串操作指令中用作计数器。

DX:在寄存器间接寻址的I/O指令中存放I/O地址。

在做双字长乘除法运算时,DX与AX合起来存放一个双字长数。

SP:存放栈顶偏移地址。

BP:存放访问内存时的基地址。

SP和BP也可以存放数据,但它们的默认段寄存器都是SS。

&电子工业出版社&第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个?逻辑地址呢?答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。