若干常用的时序逻辑电路_寄存器和移位寄存器

- 格式:ppt

- 大小:1.19 MB

- 文档页数:26

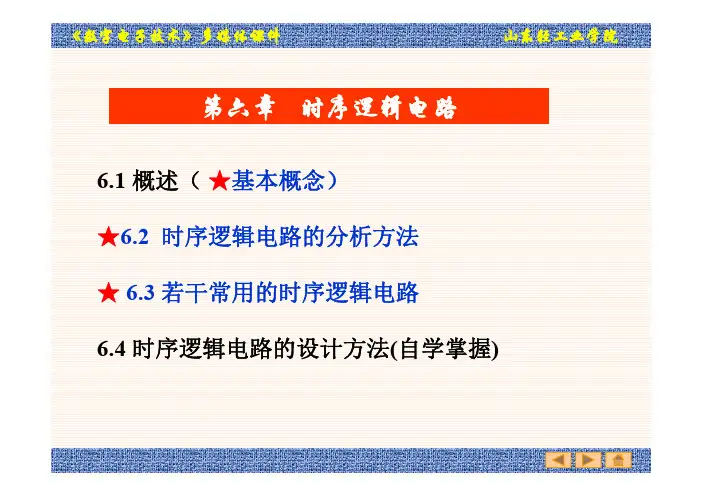

第六章 时序逻辑电路(14课时)本章教学目的、要求:1.掌握时序逻辑电路的分析方法。

2.掌握常用时序逻辑部件:寄存器、移位寄存器、由触发器构成的同步二进制递 增计数器和异步十进制递减计数器,及由集成计数器构成任意进制计数器。

3.熟悉常用中规模集成时序逻辑电路的逻辑功能及使用方法。

4.掌握同步时序逻辑电路的设计方法。

重点:时序逻辑电路在电路结构和逻辑功能上的特点;同步时序逻辑电路的分析方法;常用中规模集成时序逻辑电路的逻辑功能及使用方法;由集成计数器构成任意进制计数器。

难点:同步时序逻辑电路的设计方法第一节 概述(0.5课时)一、定义:1.定义:任一时刻电路的稳定输出不仅取决于当时的输入信号,而且还取决于电路原来的状态。

2.例:串行加法器:指将两个多位数相加时,采取从低位到高位逐位相加的方式完成相加运算。

需具备两个功能:将两个加数和来自低位的进位相加, 记忆本位相加后的进位结果。

全加器执行三个数的相加运算, 存储电路记下每次相加后的运算结果。

CP a i b i c i-1(Q ) s i c i (D )0 a 0 b 0 0 s 0 c 0 1 a 1 b 1 c 0 s 1 c 1 2 a 2 b 2 c 1 s 2 c2 3.结构上的特点:①时序逻辑电路通常包含组合电路和存储电路两部分,存储电路(触发器)是必不可少的;②存储器的输出状态必须反馈到组合电路的输入端,与外部输入信号共同决定组合逻辑电路的输出。

∑CI COCLKC1<1DQ 'Qia ic i-1c ib is 串行加法器电路二、时序电路的功能描述原状态:q1, q2, …, q l新状态:q1*,q2 *,…,q l*1.逻辑表达式。

Y = F [X,Q] 输出方程。

Z = G [X,Q] 驱动方程(或激励方程)。

Q* = H [Z,Q] 状态方程。

2.状态表、状态图和时序图。

三、时序电路的分类1. 按逻辑功能划分有:计数器、寄存器、移位寄存器、读/写存储器、顺序脉冲发生器等。

时序逻辑电路的分类时序逻辑电路是现代数字电路设计中的重要组成部分,广泛应用于计算机、通信系统、工业控制等领域。

根据时序逻辑电路的特点和功能,可以将其分为同步和异步两类,每一类又可以进一步细分为多个子类。

同步时序逻辑电路同步时序逻辑电路是指所有触发器在一个时钟信号的控制下工作的电路。

它们的特点是逻辑部件和触发器之间存在明确的时钟信号传输路径,通过时钟信号的统一控制可以确保各个部件在相同的时间点进行状态的更新。

同步时序逻辑电路主要包括以下几种分类:1.锁存器(Latch):锁存器是一种用触发器实现的存储元件,可以存储一个比特的信息,并在时钟信号的边沿进行更新。

常见的锁存器有D锁存器、JK锁存器等,它们可以应用于寄存器、缓存等场景。

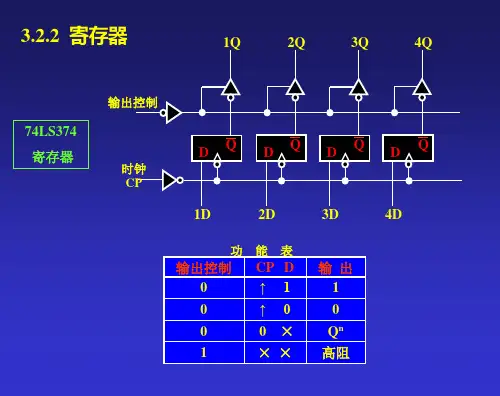

2.寄存器(Register):寄存器是由若干个锁存器组成的存储单元,可以同时存储多个比特的信息。

根据输入输出的配置,寄存器可以分为并行输入输出寄存器和串行输入输出寄存器。

3.计数器(Counter):计数器是一种能够在一个范围内进行计数的时序逻辑电路。

常见的计数器有二进制计数器、同步计数器和异步计数器等,它们可以应用于时钟频率分频、时钟周期计数等场景。

4.移位寄存器(Shift Register):移位寄存器是一种可以将输入序列移位输出的时序逻辑电路。

常见的移位寄存器有串行输入并行输出寄存器和并行输入串行输出寄存器等,它们可以应用于数据的平行-串行和串行-平行转换。

5.状态机(Finite State Machine,FSM):状态机是一种通过多个状态和状态之间的转移来对系统进行建模的时序逻辑电路。

常见的状态机包括Mealy状态机和Moore状态机,它们可以用于设计数字系统的控制器、序列检测电路等。

异步时序逻辑电路异步时序逻辑电路是指各个逻辑部件之间没有明确的时钟信号传输路径,它们是基于组合逻辑电路的延时和信号传播来完成状态更新的。

与同步时序逻辑电路相比,异步时序逻辑电路的设计更加灵活,但同时也面临着时序和稳定性等问题的挑战。

时序逻辑电路的功能时序逻辑电路是数字电子电路中一种重要的电路类型,它的功能主要用于处理和控制时序信号。

时序信号是指按照一定的时间顺序变化的信号,如时钟信号、计数信号等。

时序逻辑电路能够对这些时序信号进行处理和控制,实现各种复杂的功能。

时序逻辑电路主要由触发器、计数器、移位寄存器等组成,通过这些元件的组合和连接,可以实现各种不同的功能需求。

下面将介绍几种常见的时序逻辑电路及其功能。

1. 时钟发生器时钟发生器是时序逻辑电路中最基本的电路之一。

它的功能是产生稳定的时钟信号,用于同步整个数字系统中的各个部件。

时钟信号的频率和占空比可以通过时钟发生器进行调节,以满足不同的应用需求。

2. 触发器触发器是一种存储器件,它的功能是在时钟信号的作用下,根据输入信号的变化产生相应的输出信号。

触发器有多种类型,如D触发器、JK触发器、T触发器等。

它们可以用于存储和传输数据,实现数据的暂存和延迟等功能。

3. 计数器计数器是一种能够对输入的时序信号进行计数操作的电路。

它的功能是将输入的时序信号进行计数,并输出相应的计数值。

计数器可以实现简单的计数功能,也可以根据特定的计数模式,实现复杂的计数功能,如循环计数、递减计数等。

4. 移位寄存器移位寄存器是一种具有移位功能的存储器件。

它的功能是将输入信号按照一定的规律进行移位操作,并输出相应的移位结果。

移位寄存器可以实现数据的串行输入和串行输出,还可以实现数据的并行输入和并行输出,广泛应用于数据通信和数字信号处理等领域。

5. 状态机状态机是一种能够根据输入信号的变化,自动改变状态和执行相应操作的电路。

它的功能是根据特定的状态转移规则,实现复杂的控制逻辑。

状态机可以分为Moore型和Mealy型,它们在输出信号的计算方式上有所不同,但都能实现复杂的状态和控制逻辑。

时序逻辑电路的功能多种多样,它们在数字系统中起到了至关重要的作用。

无论是计算机、通信设备还是数字家电,都离不开时序逻辑电路的支持。

906-数字电路(专)

一、考试性质

《数字电路》是电子与通信工程(专业学位)、集成电路工程(专业学位)专业学位研究生入学考试的科目之一。

《数字电路》考试力求反映信息学科相关专业的特点,科学、公平、准确、规范地测评考生的基本素质和综合能力,以利用选拔具有发展潜力的优秀人才入学,为我国快速发展的信息产业培养出具有良好职业道德、国际化视野、较强分析与解决实际问题能力的高层次、应用型、复合型的专业人才。

二、考试要求

《数字电路》是信息类学科的一门重要的基础课。

通过本课程测试考生对本专业的基本概念、基础知识的掌握情况和运用能力。

三、考试形式和试卷结构

1.试卷满分及考试时间

本试卷满分为150分,考试时间为180分钟

2.答题方式

答题方式为闭卷、笔试。

试卷由试题和答题纸组成。

3.考试题型

试卷由题库组题,题型主要有填空题、选择题、简答题、综合分析题、综合设计题等。

四、考试内容

(一)数制与码制

1.概述

2.几种常见的数制

3.不同数制间的转换

4.二进制算术运算

1)二进制算术运算的特点

2)反码、补码和补码运算

5.几种常用的编码

(二)逻辑代数基础

1.概述

2.逻辑代数中的三种基本运算

3.逻辑代数的基本公式和常用公式。

常用的时序逻辑电路时序逻辑电路是数字电路中一类重要的电路,它根据输入信号的顺序和时序关系,产生对应的输出信号。

时序逻辑电路主要应用于计时、控制、存储等领域。

本文将介绍几种常用的时序逻辑电路。

一、触发器触发器是一种常见的时序逻辑电路,它具有两个稳态,即SET和RESET。

触发器接受输入信号,并根据输入信号的变化产生对应的输出。

触发器有很多种类型,常见的有SR触发器、D触发器、JK 触发器等。

触发器在存储、计数、控制等方面有广泛的应用。

二、时序计数器时序计数器是一种能按照一定顺序计数的电路,它根据时钟信号和控制信号进行计数。

时序计数器的输出通常是一个二进制数,用于驱动其他电路的工作。

时序计数器有很多种类型,包括二进制计数器、BCD计数器、进位计数器等。

时序计数器在计时、频率分频、序列生成等方面有广泛的应用。

三、时序比较器时序比较器是一种能够比较两个信号的大小关系的电路。

它接受两个输入信号,并根据输入信号的大小关系产生对应的输出信号。

时序比较器通常用于判断两个信号的相等性、大小关系等。

常见的时序比较器有两位比较器、四位比较器等。

四、时序多路选择器时序多路选择器是一种能够根据控制信号选择不同输入信号的电路。

它接受多个输入信号和一个控制信号,并根据控制信号的不同选择对应的输入信号作为输出。

时序多路选择器常用于多路数据选择、时序控制等方面。

五、时序移位寄存器时序移位寄存器是一种能够将数据按照一定规律进行移位的电路。

它接受输入信号和时钟信号,并根据时钟信号的变化将输入信号进行移位。

时序移位寄存器常用于数据存储、数据传输等方面。

常见的时序移位寄存器有移位寄存器、移位计数器等。

六、状态机状态机是一种能够根据输入信号和当前状态产生下一个状态的电路。

它由状态寄存器和状态转移逻辑电路组成,能够实现复杂的状态转移和控制。

状态机常用于序列识别、控制逻辑等方面。

以上是几种常用的时序逻辑电路,它们在数字电路设计中起着重要的作用。