寄存器和移位寄存器

- 格式:ppt

- 大小:588.00 KB

- 文档页数:15

寄存器的原理寄存器是用来存放二进制数码的逻辑部件,在计算机和数字电路中应用广泛。

寄存器存放数码的方式有并行和串行两种。

并行方式是数码各位从各对应位输入端同时输入到寄存器中;串行方式是数码从一个输入端逐位输入到寄存器中。

寄存器取出数码的方式也有并行和串行两种。

并行方式是指被取出的数码在各对应位输出端上同时出现;串行方式是指被取出的数码在一个输出端上逐位出现。

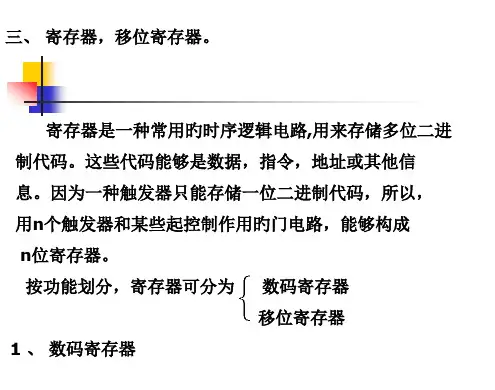

寄存器分数码寄存器和移位寄存器两种。

一、数码寄存器这种寄存器只有寄存数码和清除原有数码的功能。

寄存器由触发器组成。

由于一个触发器可以存储1位二进制数,因而要存储几位二进制数就需要几个触发器。

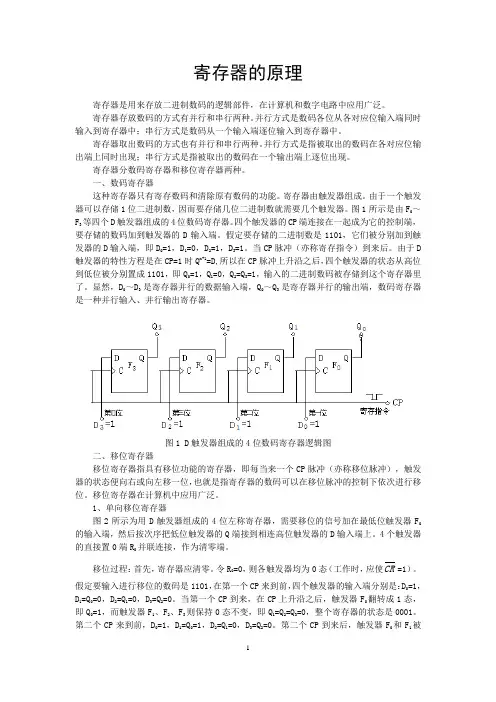

图1所示是由F0~F3等四个D触发器组成的4位数码寄存器。

四个触发器的CP端连接在一起成为它的控制端,要存储的数码加到触发器的D输入端。

假定要存储的二进制数是1101,它们被分别加到触发器的D输入端,即D0=1,D1=0,D2=1,D3=1。

当CP脉冲(亦称寄存指令)到来后。

由于D 触发器的特性方程是在CP=1时Q n+1=D,所以在CP脉冲上升沿之后,四个触发器的状态从高位到低位被分别置成1101,即Q0=1,Q1=0,Q2=Q3=1,输入的二进制数码被存储到这个寄存器里了。

显然,D0~D3是寄存器并行的数据输入端,Q0~Q3是寄存器并行的输出端,数码寄存器是一种并行输入、并行输出寄存器。

图1 D触发器组成的4位数码寄存器逻辑图二、移位寄存器移位寄存器指具有移位功能的寄存器,即每当来一个CP脉冲(亦称移位脉冲),触发器的状态便向右或向左移一位,也就是指寄存器的数码可以在移位脉冲的控制下依次进行移位。

移位寄存器在计算机中应用广泛。

1、单向移位寄存器图2所示为用D触发器组成的4位左称寄存器,需要移位的信号加在最低位触发器F0的输入端,然后按次序把低位触发器的Q端接到相连高位触发器的D输入端上。

4个触发器的直接置0端R0并联连接,作为清零端。

移位过程:首先,寄存器应清零。

寄存器和移位寄存器简介

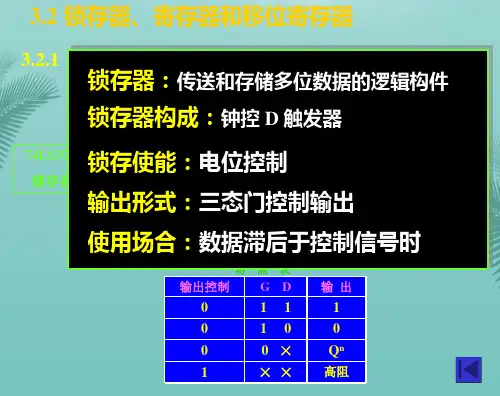

( 1 )寄存器

能够把二进制数码存贮起来的的部件叫数码寄存器,简称寄存器。

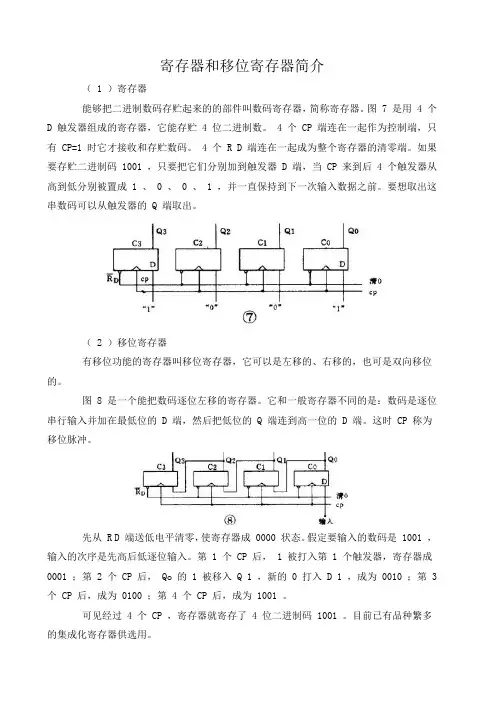

图 7 是用 4 个D 触发器组成的寄存器,它能存贮 4 位二进制数。

4 个 CP 端连在一起作为控制端,只有 CP=1 时它才接收和存贮数码。

4 个 R D 端连在一起成为整个寄存器的清零端。

如果要存贮二进制码 1001 ,只要把它们分别加到触发器 D 端,当 CP 来到后 4 个触发器从高到低分别被置成 1 、 0 、 0 、 1 ,并一直保持到下一次输入数据之前。

要想取出这串数码可以从触发器的 Q 端取出。

( 2 )移位寄存器

有移位功能的寄存器叫移位寄存器,它可以是左移的、右移的,也可是双向移位的。

图 8 是一个能把数码逐位左移的寄存器。

它和一般寄存器不同的是:数码是逐位串行输入并加在最低位的 D 端,然后把低位的 Q 端连到高一位的 D 端。

这时 CP 称为移位脉冲。

先从 R D 端送低电平清零,使寄存器成 0000 状态。

假定要输入的数码是 1001 ,输入的次序是先高后低逐位输入。

第 1 个 CP 后, 1 被打入第 1 个触发器,寄存器成0001 ;第 2 个 CP 后, Qo 的 1 被移入 Q 1 ,新的 0 打入 D 1 ,成为 0010 ;第 3 个 CP 后,成为 0100 ;第 4 个 CP 后,成为 1001 。

可见经过 4 个 CP ,寄存器就寄存了 4 位二进制码 1001 。

目前已有品种繁多的集成化寄存器供选用。

寄存器和移位寄存器基于EWB的电路设计和仿真――寄存器与移位寄存器部分前言在现今电子设计领域中,EDA设计和仿真是一个非常重要的环节。

在众多的EDA设计和仿真软件中,EWB软件以其强大的仿真设计应用功能,在各高校电信类专业电子电路的仿真和设计中得到了较为广泛的应用。

EWB软件及其相关的应用对提高学生的仿真设计能力,更新设计理念有较大的好处及帮助。

EWB(电子工作平台)软件,最突出的特点是用户界面友好,各类器件和集成芯片丰富,尤其是其直观的虚拟仪表是EWB软件的一大特色。

它采用直观的图形界面创建电路:在计算机屏幕上模仿真实实验室的工作台,绘制电路图需要的元器件、电路仿真需要的测试仪器均可直接从屏幕上选取。

EWB软件所包含的虚拟仪表有:示波器,万用表,函数发生器,波特图图示仪,失真度分析仪,频谱分析仪,逻辑分析仪,网络分析仪等。

这些仪器的使用使仿真分析的操作更符合平时实验的习惯。

本次毕业设计主要是利用EWB软件来仿真和设计寄存器和移位寄存器电路,并通过硬件实验调试来验证理论和仿真结果。

1 EWB软件的简介1.1 EWB软件的概述随着电子技术和计算机技术的发展,电子产品已与计算机紧密相连,电子产品的智能化日益完善,电路的集成度越来越高,而产品的更新周期却越来越短。

电子设计自动化(EDA)技术,使得电子线路的设计人员能在计算机上完成电路的功能设计、逻辑设计、性能分析、时序测试直至印刷电路板的自动设计。

EDA是在计算机辅助设计(CAD)技术的基础上发展起来的计算机设计软件系统。

与早期的CAD软件相比,EDA软件的自动化程度更高、功能更完善、运行速度更快,而且操作界面友善,有良好的数据开放性和互换性。

电子工作平台Electronics Workbench (EWB)(现称为MultiSim) 软件是加拿大Interactive Image Technologies公司于八十年代末、九十年代初推出的电子电路仿真的虚拟电子工作台软件,它具有这样一些特点:(1)软件仪器的控制面板外形和操作方式都与实物相似,可以实时显示测量结果。