最新ARM体系简介14

- 格式:ppt

- 大小:2.41 MB

- 文档页数:7

ARM架构(过去称作进阶精简指令集机器(Advanced RISC Machine),更早称作Acorn RISC Machine)是一个32位元精简指令集(RISC)中央处理器(processor)架构,其广泛地使用在许多嵌入式系统(embedded)设计。

由于节能的特点,ARM处理器非常适用于行动通讯领域,符合其主要设计目标为低耗电的特性。

在今日,ARM家族占了所有32位元嵌入式处理器75%的比例[1],使它成为占全世界最多数的32位元架构之一。

ARM处理器可以在很多消费性电子产品上看到,从可携式装置(PDA、移动电话、多媒体播放器、掌上型电玩,和计算机)到电脑周边设备(硬盘、桌上型路由器)甚至在导弹的弹载计算机等军用设施中都有他的存在。

在此家族中衍伸的重要产品还包括Marvell的XScale架构和德州仪器的OMAP系列。

编辑本段历史ARM的设计是Acorn电脑公司(Acorn Computers Ltd)于1983年开始的开发计划。

这个团队由Roger Wilson和Steve Furber带领,着手开发一种新架构,类似进阶的MOS Technology 6502处理器。

Acorn有一大堆建构在6502架构上的电脑,因此能设计出一颗类似的芯片即意味着对公司有很大的优势。

团队在1985年时开发出ARM1 Sample版,而首颗"真正"的产能型ARM2于次年量产。

ARM2具有32位的数据总线、26位的寻址空间,并提供64 Mbyte 的寻址范围与16个32-bit的暂存器。

这些暂存器其中有一颗做为(word大小)程式计数器,其前面6 bits和后面2 bits用来保存处理器状态标记(Processor Status Flags)。

ARM2可能是全世界最简单实用的32位微处理器,其仅容纳了30,000个晶体管(相较于Motorola六年后的68000其包含了70,000颗)。

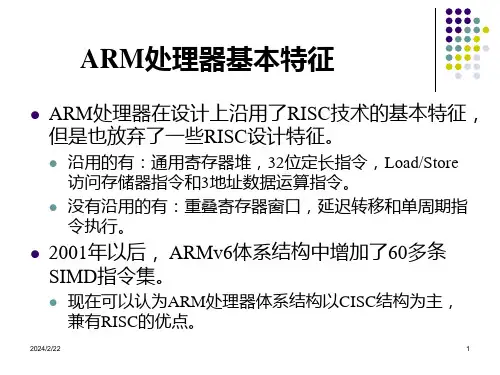

A R M体系及原理体系结构概述指令集体系结构1. 一条ARM指令的最高四位bit[31:28]为条件域(condition field),根据其值的不同来确定当前指令对CPSR中的N、Z、C和V标志的设置与否。

2. ARM指令集支持一个向前或向后32M范围内跳转的Branch指令。

如果是Branch and Link指令,则除了支持向前或向后的32M范围跳转外,还能将跳转指令的下一条指令地址(返回地址)压入R14(LR)。

而在ARMv4以上支持T的版本中,还有Branch and Exchange指令,此指令可以拷贝通用寄存器Rm的值到PC中,而若其bit[0]为0,则进行ARM至Thumb的切换。

3. ARM指令集中包含了状态寄存器获取指令MSR和MRS用来对CPSR和SPSR进行操作。

同时ARM指令集还提供了对协处理器的操作指令MCR和MRC。

4. SWI提供了软件中断的功能,此指令的bit[23:0]为一个立即数,ARM处理器会忽略这个立即数,但这个立即数可以提供异常处理程序使用。

寄存器通用寄存器(r0-r15):不分组寄存器r0-r7:可以工作在所有的处理模式下,没有隐含的特殊用途分组寄存器r8-r14:分组寄存器的使用取决于当前的处理器模式,每种模式有专用的分组寄存器用于快速异常处理。

寄存器R13通常用作堆栈指针,称作sp。

每种异常模式都有自己的R13。

通常R13被初始化为指向异常模式分配的堆栈。

在入口处,异常处理程序将用到的其他寄存器的值保存到堆栈中,返回时,重新将这些值加载到寄存器中。

寄存器R14用作子程序链接寄存器lr。

当指令BL指令时,得到R15(PC)寄存器的备份。

程序寄存器R15:ARM状态下,PC位[1:0]为0(字对齐)。

Thumb状态下,位[0]为0(半字对齐)。

由于流水线特性,PC总是指向当前执行指令的下两条指令地址。

程序状态寄存器:所有处理器模式下都访问相同的CPSR,CPSR包含条件码标志。

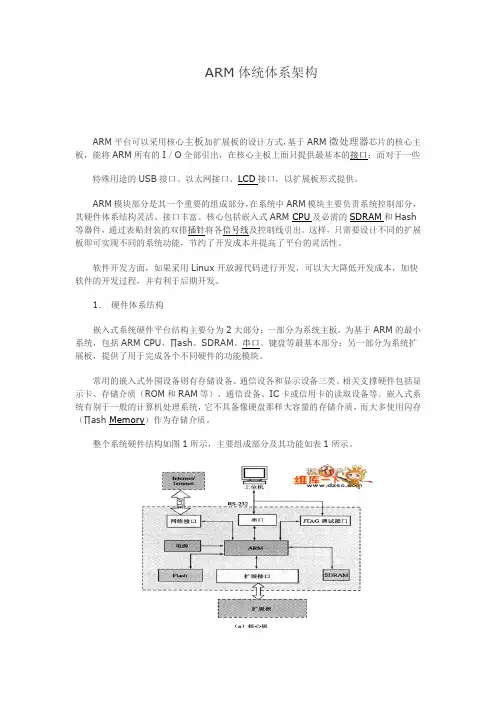

ARM体统体系架构ARM平台可以采用核心主板加扩展板的设计方式,基于ARM微处理器芯片的核心主板,能将ARM所有的I/O全部引出,在核心主板上面只提供最基本的接口;而对于一些特殊用途的USB接口、以太网接口、LCD接口,以扩展板形式提供。

ARM模块部分是其一个重要的组成部分,在系统中ARM模块主要负责系统控制部分,其硬件体系结构灵活、接口丰富。

核心包括嵌入式ARM CPU及必需的SDRAM和Hash 等器件,通过表贴封装的双排插针将各信号线及控制线引出。

这样,只需要设计不同的扩展板即可实现不同的系统功能,节约了开发成本并提高了平台的灵活性。

软件开发方面,如果采用Linux开放源代码进行开发,可以大大降低开发成本,加快软件的开发过程,并有利于后期开发。

1.硬件体系结构嵌入式系统硬件平台结构主要分为2大部分:一部分为系统主板,为基于ARM的最小系统,包括ARM CPU、∏ash、SDRAM、串口、键盘等最基本部分;另一部分为系统扩展板,提供了用于完成各个不同硬件的功能模块。

常用的嵌入式外围设备则有存储设备、通信设各和显示设备三类。

相关支撑硬件包括显示卡、存储介质(ROM和RAM等)、通信设备、IC卡或信用卡的读取设备等。

嵌入式系统有别于一般的计算机处理系统,它不具备像硬盘那样大容量的存储介质,而大多使用闪存(∏ash Memory)作为存储介质。

整个系统硬件结构如图1所示,主要组成部分及其功能如表1所示。

图1 ARM嵌入式硬件平台表1 系统硬件主要组成及其功能描述另外,系统总线扩展引出数据总线、地址总线和必需的控制总线,便于用户根据自身的特定需求,扩展外围电路。

在选择嵌入式系统的硬件时,最重要的是要先选择ARM处理器类型,因为ARM处理器不仅决定整个系统的性能,而且影响其他硬件的选用,以及操作系统和软件代码的配置。

一个设计好的ARM核心板硬件如图2所示。

图2 ARM核心板硬件图软件体系结构嵌入式软件包括与硬件相关的底层软件、操作系统、图形界面、通信协议、数据库系统、标准化浏览器和应用软件等。

ARM 处理器的三大特点是:耗电少功能强、16 位 /32 ARM 商品模式的强大之处在于它在世界范围有超过位双指令集和众多合作伙伴。

100 个的合作伙伴 (Partners)。

ARM是设计公司,本身不生产芯片。

采用转让许可证制度,由合作伙伴生产芯片。

当前 ARM 体系结构的扩充包括:·Thumb 16 位指令集,为了改善代码密度;·DSP DSP 应用的算术运算指令集;·Jazeller 允许直接执行Java 字节码。

ARM 处理器系列提供的解决方案有:·无线、消费类电子和图像应用的开放平台;·存储、自动化、工业和网络应用的嵌入式实时系统;·智能卡和S IM 卡的安全应用。

ARM 处理器本身是32 位设计,但也配备16 位指令集。

一般来讲存储器比等价32 位代码节省达35%,然而保留了32 位系统的所有优势。

ARM 的 Jazelle 技术使 Java 加速得到比基于软件的 Java 虚拟机 (JVM) 高得多的性能,和同等的非Java 加速核相比功耗降低 80%。

CPU 功能上增加 DSP 指令集提供增强的 16 位和 32 位算术运算能力,提高了性能和灵活性。

ARM 还提供两个前沿特性来辅助带深嵌入处理器的高集成SoC 器件的调试,它们是嵌入式ICE-RT 逻辑和嵌入式跟踪宏核 (ETMS) 系列。

当前有 5 个产品系列—— ARM7 、 ARM9 、ARM9E 、 ARM10 和 SecurCore。

1、 ARM7 系列优化用于对价位和功耗敏感的消费应用的低功耗·嵌入式 ICE-RT 逻辑;32 位核,有:·非常低的功耗;·三段流水线和冯·诺依曼结构,提供0.9MIPS/MHz 。

2、 SecurCore SC100 特为安全市场设计,带特定的抗拒窜改和反工程的特性。

还带灵活的保护单元确保操作系统和应用数据的安全。

ARM标准主要涉及ARM处理器体系结构和ARM处理器指令集。

ARM处理器体系结构,如ARM7、ARM9、ARM11等,通常用于移动设备和嵌入式系统等。

这些体系结构采用低功耗设计,体积小、低成本、高性能,支持Thumb(16位)/ARM(32位)双指令集,能很好的兼容8位/16位器件,且大量使用寄存器,指令执行速度更快,寻址方式灵活简单,执行效率高。

ARM处理器指令集,分为16位和32位指令集。

ARM处理器的指令集具有体积小、低功耗、低成本、高性能的特点。

其中,Jazelle技术使Java加速得到比基于软件的Java虚拟机(JVM)高得多的性能,和同等的非Java加速核相比功耗降低80%。

CPU功能上增加DSP指令集提供增强的16位和32位算术运算能力,提高了性能和灵活性。

此外,ARM还提供两个前沿特性来辅助带深嵌入处理器的高集成SoC器件的调试,它们是嵌入式ICE-RT逻辑和嵌入式跟踪宏核(ETMS)系列。

如果有更多相关问题,可以咨询ARM官方工作人员获取解答。